去耦电容的有效使用方法有哪些

模拟技术

描述

去耦电容有效使用方法的要点大致可以分为以下两种。去耦电容有效使用方法的要点大致可以分为以下两种。

要点1:使用多个去耦电容

去耦电容的有效使用方法之一是用多个(而非1个)电容进行去耦。使用多个电容时,使用相同容值的电容时和交织使用不同容值的电容时,效果是不同的。

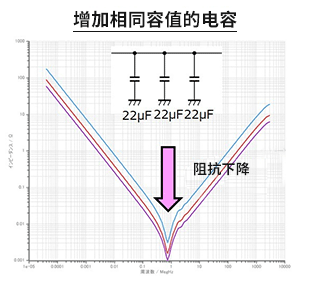

・使用多个容值相同的电容时

右图是使用1个22µF的电容时(蓝色)、增加1个变为2个时(红色)、再增加1个变为3个(紫色)时的频率特性。

如图所示,当增加容值相同的电容后,阻抗在整个频率范围均向低的方向转变,也就是说阻抗越来越低。

这一点可通过思考并联连接容值相同的电容时,到谐振点的容性特性、取决于ESR(等效串联电阻)的谐振点阻抗、谐振点以后的ESL(等效串联电感)影响的感性特性来理解。

并联的电容容值是相加的,所以3个电容为66µF,容性区域的阻抗下降。

谐振点的阻抗是3个电容的ESR并联,因此为 ,假设这些电容的ESR全部相同,则ESR减少至1/3,阻抗也下降。

,假设这些电容的ESR全部相同,则ESR减少至1/3,阻抗也下降。

谐振点以后的感性区域的ESL也是并联,因此为 ,假设3个电容的ESL全部相同,则ESL减少至1/3,阻抗也下降。

,假设3个电容的ESL全部相同,则ESL减少至1/3,阻抗也下降。

由此可知,通过使用多个相同容值的电容,可在整个频率范围降低阻抗,因此可进一步降低噪声。

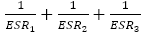

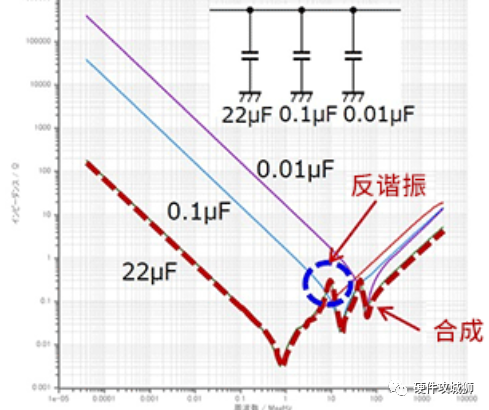

・使用多个容值不同的电容时

这些曲线是在22µF的电容基础上并联增加0.1µF、以及0.01µF的电容后的频率特性。

通过增加容值更小的电容,可降低高频段的阻抗。相对于一个22µF电容的频率特性来说,0.1µF和0.01µF的特性是合成后的特性(红色虚线)。

这里必须注意的是,有些频率点产生反谐振,阻抗反而增高,EMI恶化。反谐振发生于容性特性和感性特性的交叉点。

所增加电容的电容量,一般需要根据目标降噪频率进行选型。

另外,在这里给出的频率特性波形图是理想的波形图,并未考虑PCB板的布局布线等引起的寄生分量。在实际的噪声对策中,需要考虑寄生分量的影响。

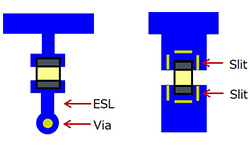

要点2:降低电容的ESL

去耦电容的有效使用方法的第二个要点是降低电容的ESL(即等效串联电感)。虽说是“降低ESL”,但由于无法改变单个产品的ESL本身,因此这里是指“即使容值相同,也要使用ESL小的电容”。通过降低ESL,可改善高频特性,并可更有效地降低高频噪声。

・即使容值相同也要使用尺寸较小的电容

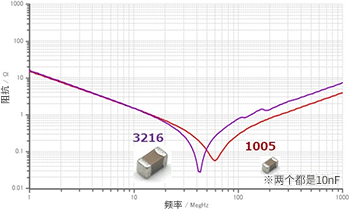

对于积层陶瓷电容(MLCC),有时会准备容值相同但尺寸不同的几个封装。ESL取决于引脚部位的结构。尺寸较小的电容基本上引脚部位也较小,通常ESL较小。

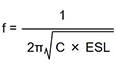

右图是容值相同、大小不同的电容的频率特性示例。如图所示,更小的1005尺寸的谐振频率更高,在之后感性区域的频率范围阻抗较低。这正如在“电容的频率特性”中所介绍的,电容的谐振频率是基于以下公式的,从公式中可见,只要容值相同,ESL越低谐振频率越高。另外,感性区域的阻抗特性取决于ESL,这一点也曾介绍过。

关于噪声对策,当需要降低更高频段的噪声时,可以选择尺寸小的电容。

・使用旨在降低ESL的电容

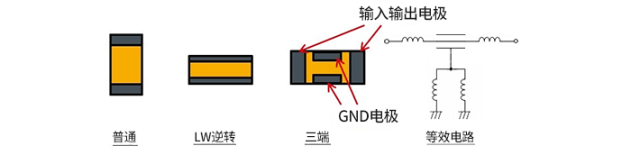

积层陶瓷电容中,有些型号采用的是旨在降低ESL的形状和结构。

如图所示,普通电容的电极在短边侧,而LW逆转型的电极则相反,在长边侧。由于L(长度)和W(宽度)相反,故称“LW逆转型”。是通过增加电极的宽度来降低ESL的类型。

三端电容是为了改善普通电容(两个引脚)的频率特性而优化了结构的电容。三端电容是将双引脚电容的一个引脚(电极)的另一端向外伸出作为直通引脚,将另一个引脚作为GND引脚。在上图中,输入输出电极相当于两端伸出的直通引脚,左右的电极当然是导通的。这种输入输出电极(直通引脚)和GND电极间存在电介质,起到电容的作用。

将输入输出电极串联插入电源或信号线(将输入输出电极的一端连接输入端,另一端连接输出端),GND电极接地。这样,由于输入输出电极的ESL不包括在接地端,因此接地的阻抗变得非常低。另外,输入输出电极的ESL通过在噪声路径直接插入,有利于降低噪声(增加插入损耗)。

通过在长边侧成对配置GND电极,可抑制ESL;再采用并联的方式,可使ESL减半。

基于这样的结构,三端电容不仅具有非常低的ESL,而且可保持低ESR,与相同容值相同尺寸的双引脚型电容相比,可显著改善高频特性。

去耦电容的有效使用方法:其他注意事项

①Q较高的陶瓷电容

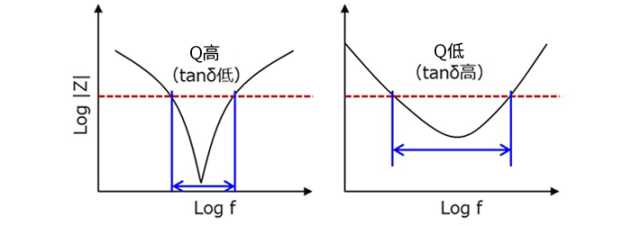

电容具有被称为“Q”的特性。下图即表示Q和频率-阻抗特性之间的关系。

当Q值高时,阻抗在特定的窄带会变得非常低。当Q值低时,阻抗虽然不会极度下降,但可以在很宽的频段内降低。这种特性可能有助于符合某些EMC标准。例如,使用电容量变化较大的电容时,如果Q值很高,则可能存在无法消除目标频率噪声的个体。在这种情况下,还有一种通过使用具有低Q的电容来抑制波动影响的手法。

②热风焊盘等的PCB图形

旨在提高散热性的热风焊盘等的PCB图形,图形的电感分量会增加。电感分量的增加会使谐振频率向低频端移动,所以有时可能无法获得理想的噪声消除效果。

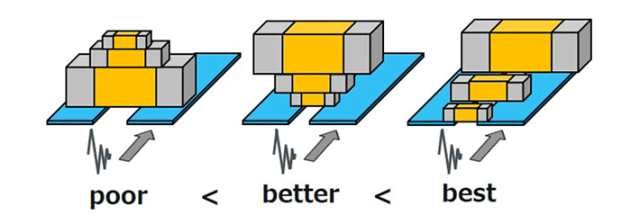

③探讨对策时的电容试装

试制后需要对高频噪声采取对策,可以考虑增加小容量的电容器。此时,如下图所示,如果在大容量电容器上安装要增加的电容器(左例),则纵向会增加额外的电感分量,因此不能充分发挥增加电容器的效果。在中间的例子中,虽然未违背“尽可能使小容量电容靠近噪声源”的理论,但阻抗会与实际修改的PCB布局不同。最好的方法是以尽量接近实际修改的配置进行探讨(右例)。

在探讨对策时,也可能会发生虽然噪声试验OK,但安装到修改后的PCB时NG的现象,因此需要在探讨时就有意识地按照实际来安装。

④电容的电容量变化率

噪声对策用的电容的电容量变化率较大时,谐振频率的波动会变大,目标消减频段会产生变化或波动,有时很难找到理想的噪声对策。尤其是需要在窄频段大幅消除噪声时,需要格外注意。下表表示电容量变化率和实际的电容量和谐振频率之间的关系。仔细看这个表的话可以看出,虽然视条件而定,不过很多情况是无法接受的。

| 电容量变化率(%) | 电容量(pF) | 谐振频率(MHz) |

|---|---|---|

| +20 | 1,200 | 145 |

| +10 | 1,100 | 152 |

| +5 | 1,050 | 155 |

| ±0 | 1,000 | 159 |

| -5 | 950 | 163 |

| -10 | 900 | 168 |

| -20 | 800 | 178 |

※ 按L=1nH计算

⑤电容器的温度特性

众所众知,电容的特性会受温度影响。目前,EMC测试的温度特性尚未标准化,但在某些应用中,不得不在明显的高温或低温条件/环境下工作、或在会产生较大温度变化的条件/环境下使用。

在这类情况下,非常有可能发生“④电容量变化率”中提到的问题,所以,用于噪声对策的电容,需要尽量使用具有CH、C0G特性的温度特性优异的产品。

总结

前面分三次对“去耦电容的有效使用方法”进行了介绍。利用电容来降低噪声是非常重要的,所以在这里总结一下。

要点1:使用多个去耦电容

使用多个电容去耦时,使用多个相同容值的电容和交织使用不同容值的电容时,效果是不同的。

■使用多个相同容值的电容时

在整个频率范围内阻抗下降,可有效降低整体噪声。

■使用多个不同容值的电容时

可降低更高频段的阻抗,可有效降低高频噪声。但是需要注意的是,有些频率会产生反谐振,阻抗反而增高,噪声反而恶化。

要点2:降低电容的ESL

如果容量相同,则ESL越低谐振频率越高,因此通过降低ESL可改善高频特性,从而可更有效地降低高频噪声。

■即使容值相同也要使用尺寸较小的电容

ESL取决于电容引脚部位的结构,因此尺寸较小的电容基本上引脚部位也较小,通常ESL较小。当需要降低更高频段的噪声时,方法之一是选择尺寸小的电容。但是,要注意DC偏置特性。

■使用旨在降低ESL的电容

积层陶瓷电容中,有些型号采用的是旨在降低ESL的形状和结构,比如LW逆转型电容、三端电容。

去耦电容的有效使用方法:其他注意事项

■Q较高的陶瓷电容

当Q值高时,阻抗在特定的窄带会变得非常低。当Q值低时,阻抗虽然不会极度下降,但可以在较宽的频段内降低。

■热风焊盘等的PCB图形

旨在提高散热性的热风焊盘等的PCB图形,图形的电感分量会增加,会使谐振频率向低频端移动,所以有时可能无法获得理想的噪声消除效果。

■探讨对策时的电容试装

增加小容量电容以降低高频噪声时,要基于“尽可能使小容量电容靠近噪声源”的理论,以尽量接近实际修改的配置进行探讨。探讨时如果和修改后的配置不同,阻抗也会不同,很可能无法获得评估时的效果。

■电容的电容量变化率

噪声对策用的电容的电容量变化率较大时,谐振频率的波动会变大,目标消减频段会产生变化或波动,有时很难找到理想的噪声对策。尤其是需要在窄频段大幅消除噪声时,需要格外注意。

■电容的温度特性

电容的特性会受温度影响,因此,在明显的高温、低温、较大温度变化的条件/环境下使用的应用,需要采用温度特性优异的电容。

编辑:黄飞

-

旁路电容 和去耦电容 !#电容学习电子知识 2022-10-20

-

EMC基础:去耦电容的有效使用方法2023-01-03 419

-

去耦电容的作用及方法2023-08-07 769

-

去耦电容怎么用?2019-08-02 0

-

电容局部如何去耦?2021-03-04 0

-

去耦电容的有效使用方法要点二2019-04-04 1521

-

关于去耦电容的有效使用方法要点分享2019-08-22 3016

-

分享去耦电容的有效使用方法和应用2019-08-22 3266

-

五种去耦电容的有效使用方法解析2021-03-29 4625

-

去耦电容的有效使用方法2022-11-23 680

-

去耦电容有效使用方法2022-12-22 533

-

使用电容器降低噪声:去耦电容的有效使用方法 要点12023-02-15 533

-

使用电容器降低噪声:去耦电容的有效使用方法 要点22023-02-15 433

-

使用电容器降低噪声-去耦电容的有效使用方法 其他注意事项2023-02-15 289

-

使用电容器降低噪声-去耦电容的有效使用方法总结2023-02-15 559

全部0条评论

快来发表一下你的评论吧 !