第4代碳化硅场效应晶体管的应用

功率器件

描述

Qorvo 的新型 750V 第 4 代 SiC FET

Qorvo (UnitedSiC) 近宣布推出采用新型表面贴装 TOLL 封装的 750V/5.4mΩ SiC FET,扩大了公司的性能地位,并扩大了其突破性的第 4 代 SiC FET 产品组合。该产品是 750V SiC FET 系列中的首款产品,R DS(on)范围为 5.4 mΩ 至 60 mΩ,将采用 TOLL 封装。这些组件非常适合空间有限的应用,例如可处理 100 A 电流和数百瓦到数千瓦的交流/直流电源的固态继电器和断路器。

通过2021 年 10 月收购 UnitedSiC,Qorvo 构建了基于 SiC 的 FET 产品的高性能产品组合,使公司能够提供涵盖功率转换、运动控制和电路保护等应用的电源解决方案。

具有挑战性的应用

新器件满足了服务器电源对尺寸、效率和成本的需求,其中功率密度已增加到 100 W/in 以上。3因为处理器耗电量大,并且在相同尺寸下需要更多功率(每个 AC/DC PSU 》3 kW)。同样,固态断路器需要能够满足空间受限应用要求的解决方案,其中主动冷却是一种选择,并且必须具有承受高电流和高电压的能力。

Qorvo 的新型 TOLL 封装器件满足上述要求,因为它们:

减少封装占地面积

更薄的封装,允许更厚的散热器

低功率损耗

表面贴装技术封装,可自动组装到 PCB 子卡上,从而降低成本

每个封装的电阻较低,无需并联多个 FET

高电流承受能力和更长的短路承受时间

具有足够的响应时间的抗噪能力

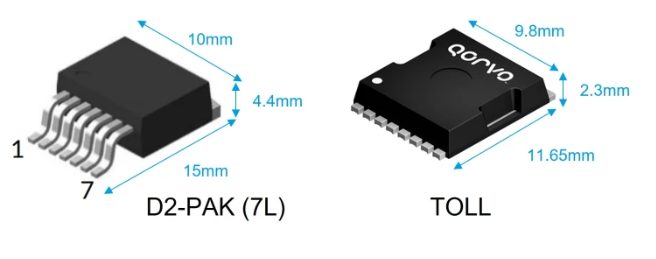

与传统的 D2-PAK 封装相比,TOLL 具有减小占地面积和高度的优点,如图 1 所示。

低 RDS(on) 表面贴装产品的尺寸 — D2PAK7L 与 TOLL。

图 1:低 R DS(on)表面贴装产品的尺寸 — D2PAK7L 与 TOLL(Qorvo)

第 4 代 SiC FET在 600/750V 级功率 FET 中的R DS(on)和输出电容的关键品质因数方面提供了无与伦比的性能。此外,该器件采用 TOLL 封装的 R DS(on)为 5.4 mΩ,比GaN 晶体管、SiC MOSFET 和一流的硅 MOSFET 低 4 至 10 倍。SiC FET 的 750V 额定值也比竞争技术高 100 至 150V,从而显着提高了处理电压瞬变的设计余量。

如图 1 所示,与同类 D2PAK 表面贴装替代方案相比,TOLL 封装的占地面积小 30%,高度短 50%(2.3 毫米)。TOLL 封装还具有开尔文源连接,可通过更清晰的栅极波形可靠、快速地切换大电流。

新型 SiC FET 利用 Qorvo 独有的共源共栅电路布置(其中 SiC JFET 与硅 MOSFET 共同封装)来创建一种器件,该器件充分利用宽带隙开关技术带来的效率优势以及硅 MOSFET 更简单的栅极驱动。SiC JFET 提供与 SiC MOSFET 相同的 R DS(on),但需要更小的芯片面积,并且通常位于器件上。将 SiC JFET 与常关硅 MOSFET 相结合,共源共栅配置保留了 JFET 的优点,同时允许与标准SiC MOSFET兼容。共源共栅是一种常关配置,对客户透明,并具有带栅极、源极和漏极的标准三端器件。

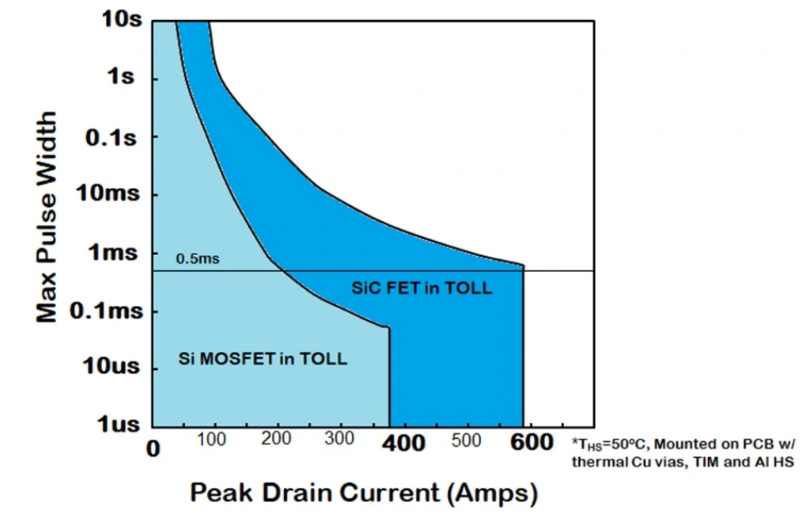

尽管尺寸大幅减小,但新型 FET 从结到外壳的热阻达到了业界的 0.1°C/W。新型 750V/5.4mΩ UJ4SC075005L8S 采用先进的生产工艺(例如烧结芯片贴装),在外壳温度高达 144°C 的情况下具有 120A 的连续额定电流,在高达 0.5ms 的情况下具有 588A 的脉冲电流额定值。

这使得“I 2 t”额定值比相同封装中的硅 MOSFET 高大约 8 倍,从而增强了鲁棒性和瞬态过载抗扰度,同时简化了设计流程。极低的 R DS(on)、高 T j(max) = 175°C 和出色的瞬态热行为相结合,实现了这一点。此外,SiC FET 的过电流比同一封装中 R DS(on)硅 MOSFET 高 2.8 倍 (tp~0.5–1 ms)。图 2 显示了采用 TOLL 封装的硅和 SiC FET 的脉冲电流与脉冲宽度的关系,对此进行了例证。

750V/5.4mΩ SiC FET 的脉冲宽度与(方波)脉冲电流与 TOLL 封装中 RDS(on) 的 600V 硅 MOSFET 的比较。

图 2:750V/5.4mΩ SiC FET 的脉冲宽度与(方波)脉冲电流与 TOLL 封装中 R DS(on) 600V 硅 MOSFET 的比较(Qorvo)

这些新型超低 R DS(on) TOLL 器件由于传导损耗低、尺寸紧凑、高浪涌耐用性和出色的关断能力,是在没有主动冷却的小型封闭场所中经常面临热挑战的保护应用的选择。它们可以地减少散热并避免并联多个 FET 的需要。

-

如何判断场效应晶体管方向,学会这几步轻松搞定2019-03-29 0

-

一文让你秒懂场效应晶体管的所有参数2019-04-04 0

-

MOS管与场效应晶体管背后的联系,看完后就全明白了2019-04-15 0

-

场效应晶体管在电路中的特别应用,你未必全都清楚2019-04-16 0

-

场效应晶体管的分类及作用2019-05-08 0

-

场效应晶体管知识和使用分享!2019-08-11 0

-

场效应晶体管的选用经验分享2021-05-13 0

-

什么是鳍式场效应晶体管?鳍式场效应晶体管有哪些优缺点?2023-02-24 0

-

Qorvo推出新一代1200V碳化硅场效应晶体管(FET)系列2022-05-12 1574

-

Qorvo®推出新一代碳化硅场效应晶体管 (FET) 系列2022-05-17 1438

-

Qorvo推出新一代1200V碳化硅场效应晶体管2022-05-25 1135

-

Qorvo发布碳化硅场效应晶体管产品2024-02-01 232

全部0条评论

快来发表一下你的评论吧 !