DDR电路的叠层与阻抗设计

描述

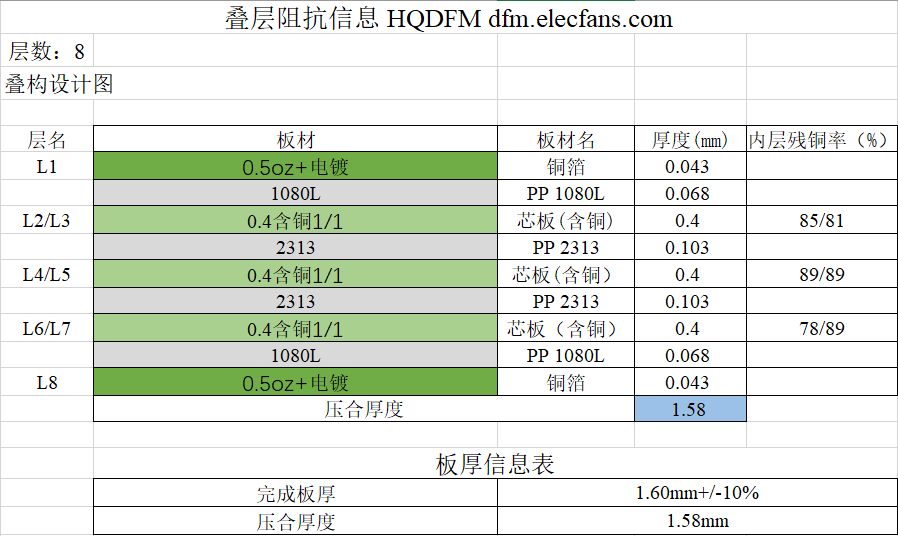

8层通孔板1.6mm厚度叠层与阻抗设计

在8层通孔板叠层设计中,顶层信号 L1 的参考平面为 L2,底层信号 L8 的参考平面为 L7。

建议层叠为TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基铜厚度建议全部采用1oZ,厚度为1.6mm。

板厚推荐叠层如下图(上)所示(8层通孔1.6mm厚度推荐叠层),阻抗线宽线距如下图(下)所示(8层通孔1.6mm厚度各阻抗线宽线距)。

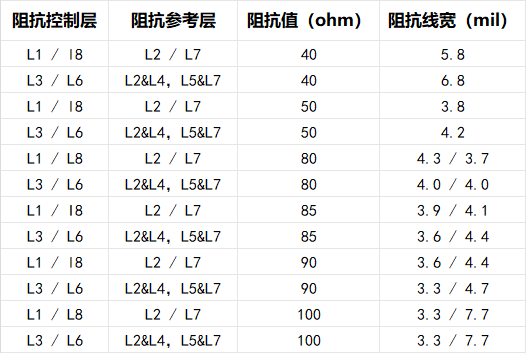

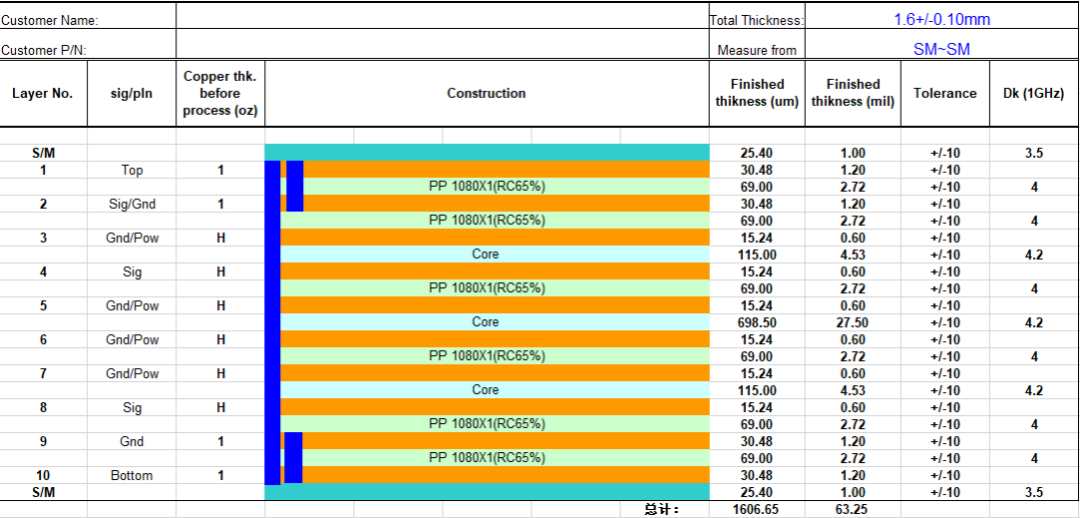

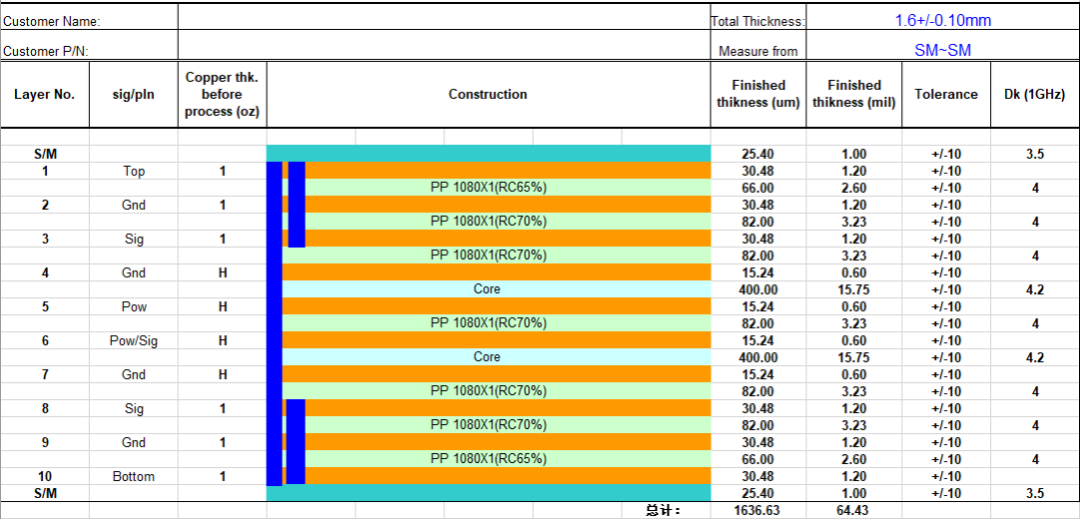

10层1阶HDI板1.6mm厚度叠层与阻抗设计

在10层1阶板叠层设计中,顶层信号L1的参考平面为L2,底层信号L10的参考平面为L9。

建议层叠为TOP-Signal/Gnd-Gnd/Power-Signal-Gnd/Power-Gnd/Power-Gnd/Power-Signal-Gnd-Bottom,其中L1,L2,L9,L10,建议采用1oZ,其它内层采用HoZ。

板厚推荐叠层如下图(上)所示(10层1阶HDI板叠层设计),阻抗线宽线距如下图(下)所示(10层1阶HDI板阻抗设计)。

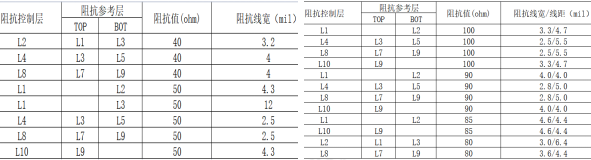

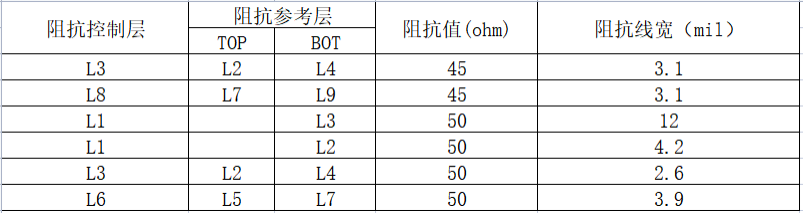

10层2阶HDI板1.6mm厚度叠层与阻抗设计

在10层2阶板叠层设计中,顶层信号L1的参考平面为L2,底层信号L10的参考平面为L9。

建议层叠为TOP-Gnd-Signal-Gnd-Power-Signal/Pow -Gnd-Signal-Gnd-Bottom,其中L1,L2,L3,L8,L9,L10,建议采用1oZ,其它内层采用HoZ。

板厚推荐叠层如下图(上)所示(10层2阶HDI板叠层设计),阻抗线宽线距如下图(中、下)所示(10层2阶HDI板单端、差分阻抗设计图)。

DDR电路阻抗线与阻抗要求

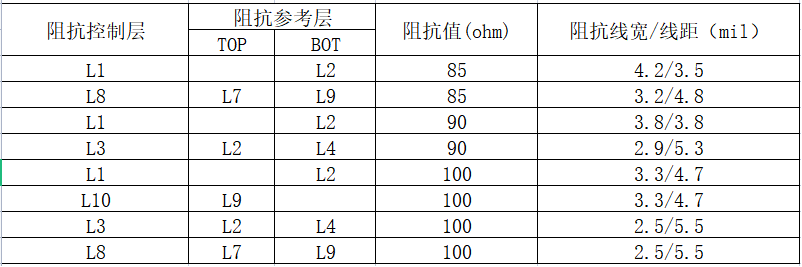

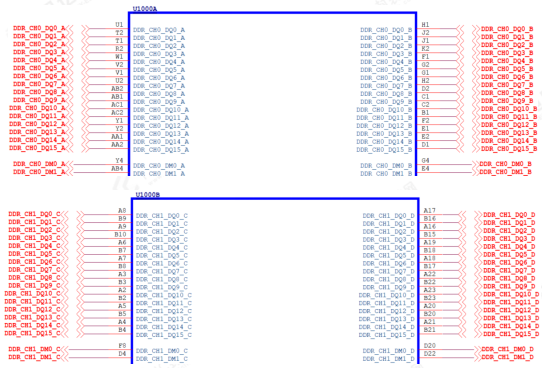

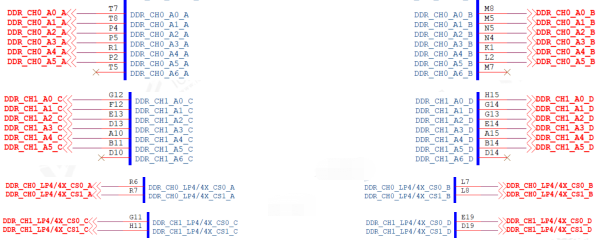

所有通道数据DQ、DM单端信号阻抗40欧姆,如果叠层无法满足40欧目标阻抗,至少保证阻抗满足45ohm±10%,40欧目标阻抗信号余量会更大,45欧目标阻抗信号余量会更小,如下图是CH0与CH1通道数据DQ、DM阻抗线。

所有通道地址、控制单端信号阻抗40欧姆,如下图是CH0与CH1通道地址、控制阻抗线。

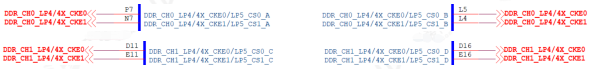

CKE单端信号阻抗50欧姆,如下图是CH0与CH1通道CKE阻抗线。

所有通道数据锁存信号DQS与时钟差分信号阻抗80欧姆,如果叠层无法满足80欧目标阻抗,至少保证阻抗满足90ohm±10%,如下图是CH0与CH1通道DQS与CLK差分阻抗线。

阻抗的知识点非常多,相信大家也竟然为此困扰,这里推荐一款可以一键智能计算阻抗自动叠层的工具:华秋DFM软件,使用其阻抗计算功能,可以高效轻松反算和计算所需阻抗和线宽线距等。

华秋DFM软件是国内首款免费PCB可制造性和装配分析软件,拥有300万+元件库,可轻松高效完成装配分析。其PCB裸板的分析功能,开发了19大项,52细项检查规则,PCBA组装的分析功能,开发了10大项,234细项检查规则。

基本可涵盖所有可能发生的制造性问题,能帮助设计工程师在生产前检查出可制造性问题,且能够满足工程师需要的多种场景,将产品研制的迭代次数降到最低,减少成本。

华秋DFM软件下载地址(复制到电脑浏览器打开):

https://dfm.elecfans.com/uploads/software/promoter/HQDFM%20V3.7.0_DFMGZH.zip

专属福利

上方链接下载还可享多层板首单立减50元

每月1次4层板免费打样

并领取多张无门槛“元器件+打板+贴片”优惠券

审核编辑 黄宇

-

DDR电路的叠层与阻抗设计2023-12-25 0

-

DDR电路的叠层与阻抗设计!2023-12-25 0

-

PCB叠层设计及阻抗计算2016-06-02 0

-

PCB设计中叠层算阻抗时需注意的四大事项2018-01-22 0

-

PCB设计中叠层算阻抗时需注意哪些事项?2019-05-16 0

-

画ddr的八层板子这样叠层可以吗?2019-05-29 0

-

PCB阻抗控制和叠层设计2019-05-30 0

-

【干货】阻抗设计必备:PCB阻抗参数推荐及叠层结构(4层板)2020-06-10 0

-

DDR4信号参考电源层,阻抗会有影响吗?2021-11-05 0

-

电路板的叠层设计的相关资料分享2021-11-12 0

全部0条评论

快来发表一下你的评论吧 !