论SRAM型FPGA软核Microblaze抗单粒子加固的方法

描述

Microblaze是32位/64位 RISC软核处理器,可以用作微处理器、实时处理器和应用处理器(Linux+MMU)。Microblaze作为FPGA的软核,搭建硬件系统时有丰富的IP资源,软件开发则有配套的SDK软件。 目前Microblaze在工业、医疗、汽车、消费以及通信市场有着广泛的应用。

Microblaze有这么多优点,是否可以用在宇航市场上呢?空间环境中,FPGA会受到单粒子效应影响,Microblaze是使用FPGA内部的资源来实现的,可能会发生功能中断或程序跑飞等情况,因此需要对Microblaze进行软件层面的加固来降低SEE的影响。

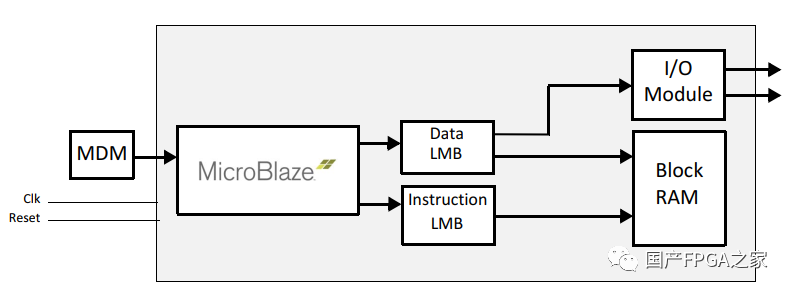

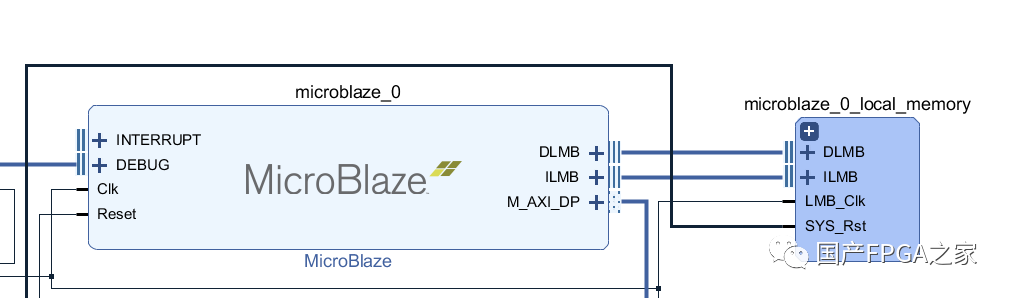

Microblaze最小系统的组成包括Clock Wizard,Processor System Reset,Microblaze IP,Data Local Memory Bus, Instruction Local Memory Bus,Data LMB BRAM Controller, Instruction LMB BRAM Controller和Block Memory。 今天贫道以Microblaze最小系统为例,简单介绍一下PG268 Xilinx方案(Fault torelant和Fail safe),然后着重介绍高可靠加固方案、方案在TMR工具的实现和故障注入验证结果,如图1所示:

图1 Microblaze最小系统

01

Xilinx 加固方案

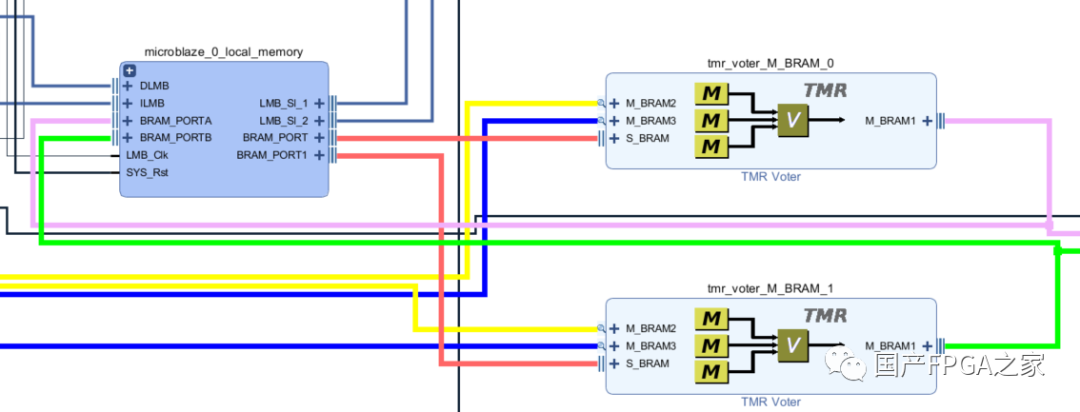

Fault-tolerant Type是对原系统整体复制两份,并在关键的Data LMB Controller和Instruction LMB Controller增加判决器,并对IO接口增加判决器。假如单路MB由于SEE发生软错误,那么通过判决器能够把软错误屏蔽掉。Fault-tolerant Type优点是实现简单,只需要利用好TMR Manager的Run block Automation功能,就能一键实现加固。Fault-tolerant Type属于粗粒度加固,因此缺点是可靠性提升有限。

图2 Fault-tolerant默认框图

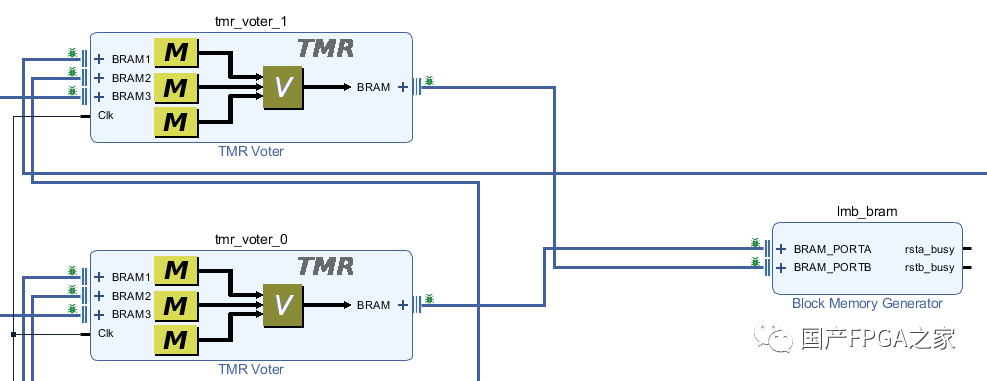

图3 TMR Voter插入位置 值得一提的是Fault-tolerant Type默认的方案是对BRAM做TMR,如果BRAM资源受限,那么可以更改设计对BRAM做ECC。

图4 Fault-tolerant Type ECC实现

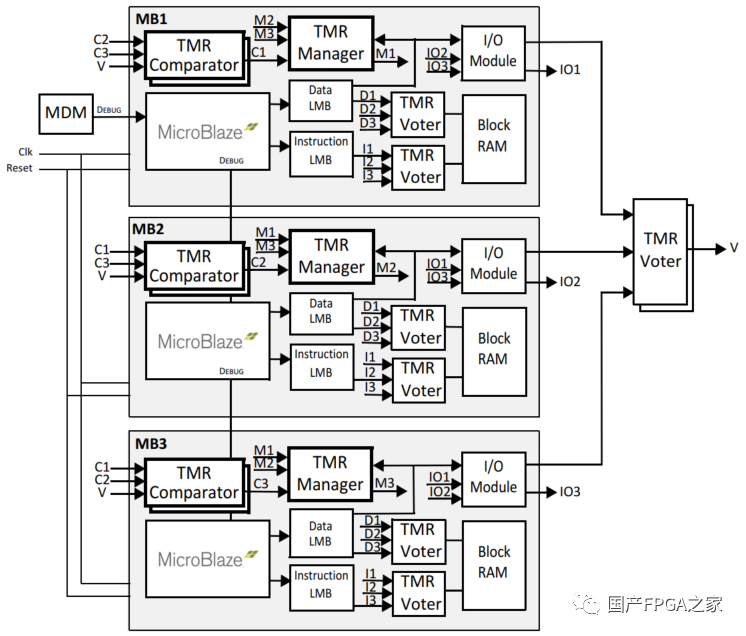

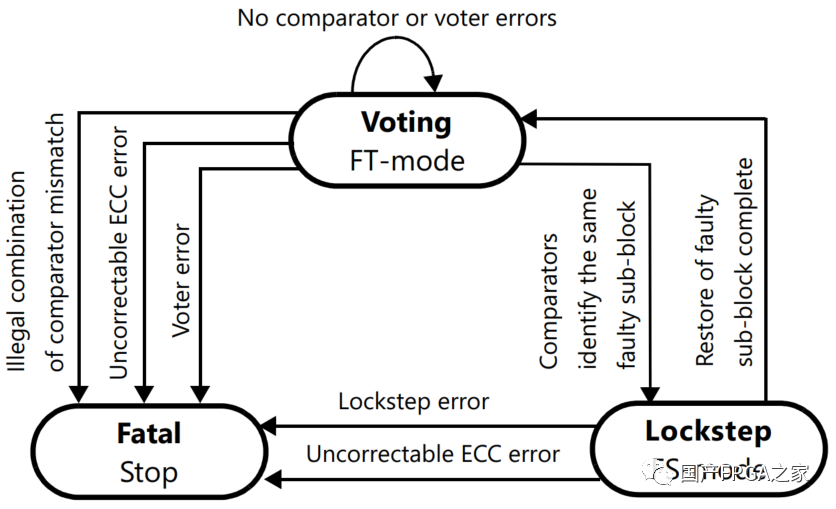

Fail-Safe Type加入了TMR Comparator,实时对三个sub block进行比较。当某一个sub block发生异常的时候,另外两路正常的sub block进入到lock step模式。Lock step模式下,一旦发现两路sub block数据不一致,那么就会进入到Fatal stop模式。

Fail-Safe Type的优点是可以在lock step模式下,通过APP尝试进行恢复,恢复成功后重新返回到fault torelant模式。Fail-Safe Type的优点也是缺点,APP需要用户自行开发,设计比较复杂。此外如果软错误比较严重,会进入到Fatal stop模式,该模式没法完成恢复,只能重新加载来解决软错误。

图5 Fail-Safe Type框图

图6 Fail-Safe Type故障模式转换流程

02

高可靠加固方案

高可靠加固方案是把Microblaze当做一般的IP,在网表层面采用TMR工具进行细粒度加固。同时考虑Microblaze的特点,对存储器BRAM进行TMR加固或者ECC加固。考虑到TMR或者ECC只能屏蔽错误,无法消除错误。因此为了更进一步提高可靠性,对储存器采用ECC+回写刷新,这样可以消除错误。本文只讨论Local Memory应用场景的加固方案和实现,下面将对实现部分做简要的介绍。

1.1 存储器BRAM ECC实现

Microblaze默认的Local Memory结构如下图所示,需要做的是展开microblaze_0_local_memory。

图7 MicroblazeLocal Memory

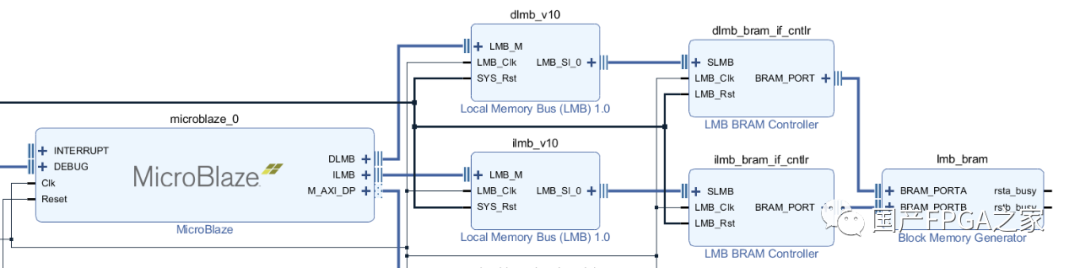

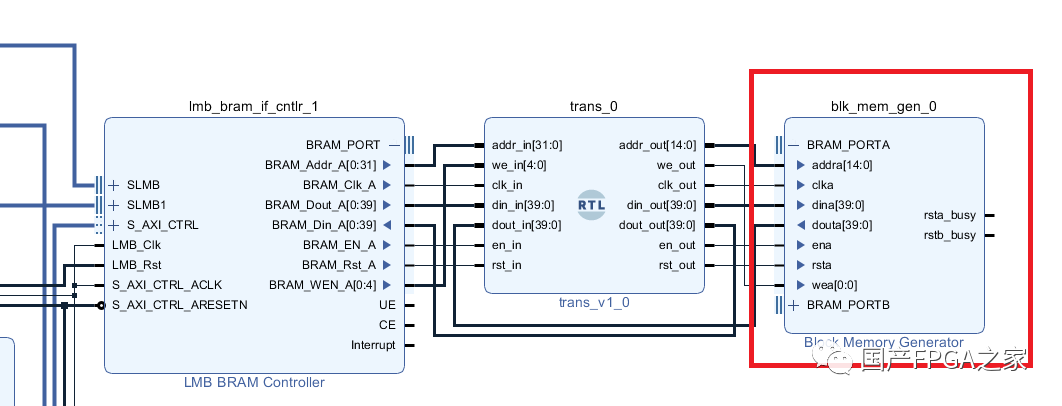

展开microblaze_0_local_memory,可以看到local_memory是由LMB Bus、LMB BRAM Controller和Block Memory组成。

图8 LocalMemory结构

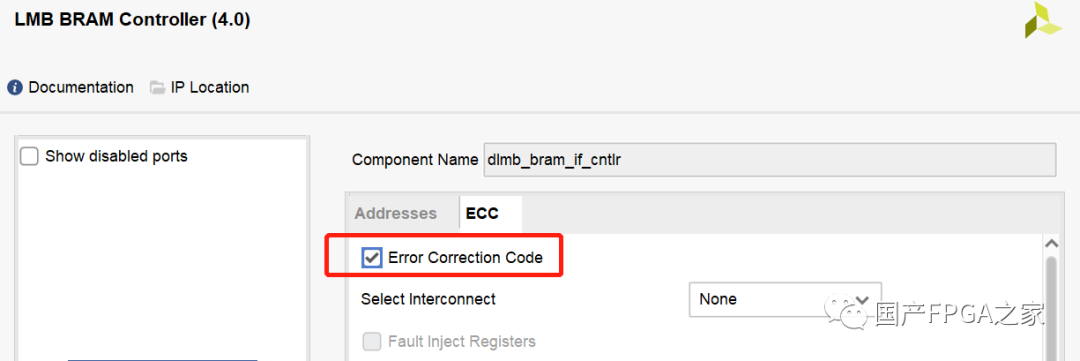

需要做的是打开LBM BRAM Controller,勾选Error Correction Code。

图9 LMB BRAM Controller设置

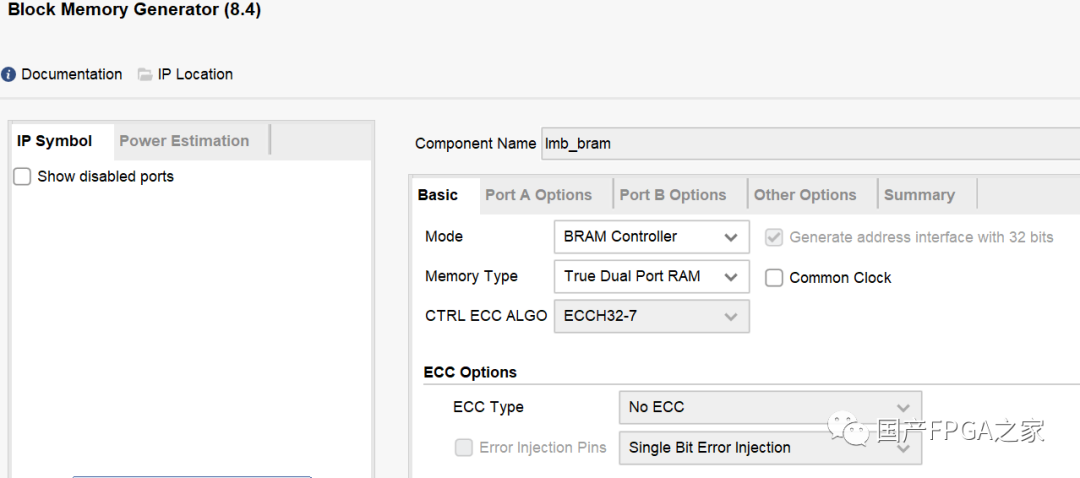

工具自动实现更改Block Memory属性,使用Soft方式来实现BRAM的ECCH32-7编解码。

图10 Block Memroy ECC参数设置

2.1 存储器BRAM ECC+自刷新逻辑

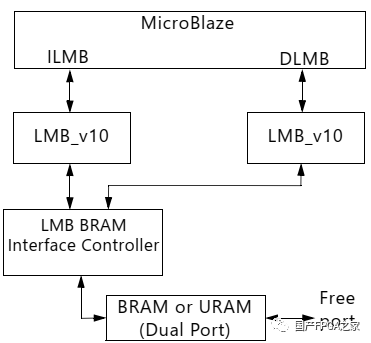

默认的Local Memroy结构里面,BRAM的两个端口都被占用住,要想实现自刷新就得更改Local Memroy结构。Microblaze支持复用DLMB和ILMB的控制器,这样两个控制器就共用一个BRAM端口,另一个端口用于自刷新,如下图所示:

图11 共享memory结构

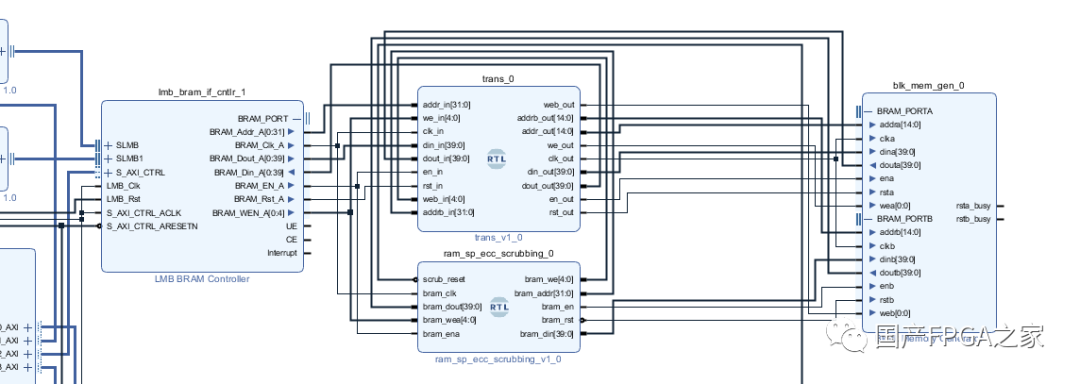

开发的自刷新模块连接到Freeport上,对BRAM全地址循环遍历,读出数据(32bit)和校验位(7bit)进行1bit错误纠错。如果解码过程出现1bit错误,把纠错后的数据回写到BRAM中。

图12 自刷新结构

2.2 MicroBlaze System TMR实现

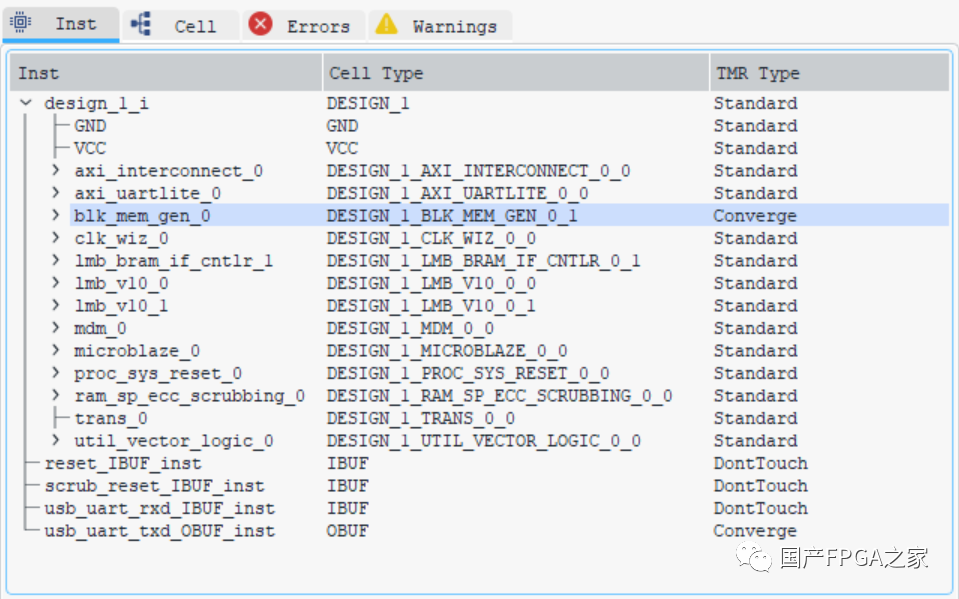

TMR工具可以对任意资源设置属性,Block Memroy采样ECC方案,因此属性设置为Converge。

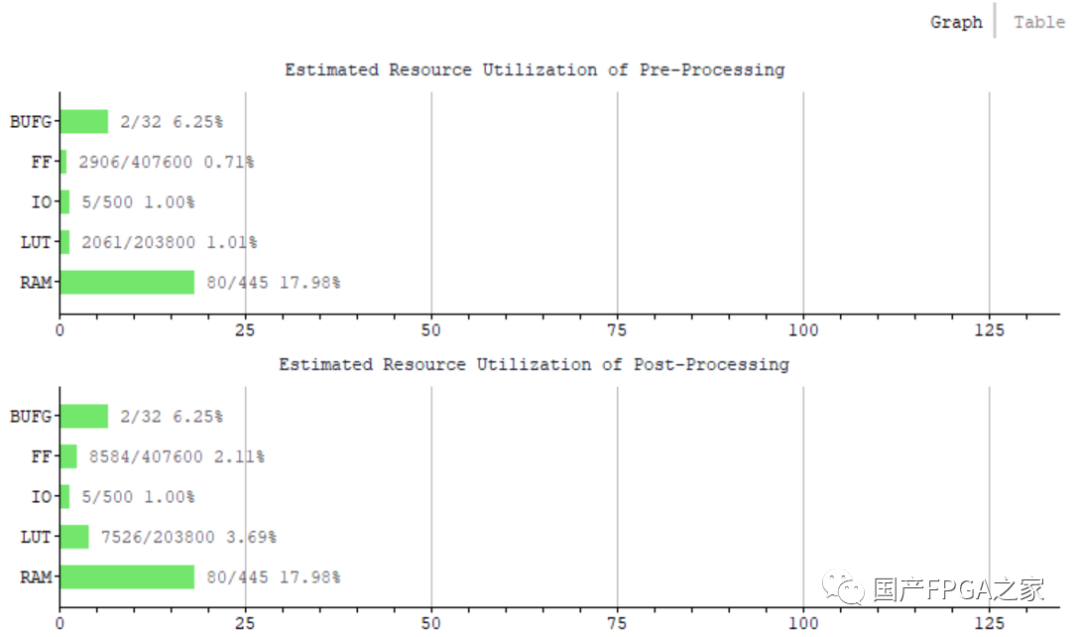

图13 TMR工具Custom模式下参数自定义设置 TMR工具可以统计出加固前的资源消耗,以及预估加固后的资源消耗,便于设计师进行评估和迭代设计。

图14TMR工具加固前资源统计和加固后资源预估

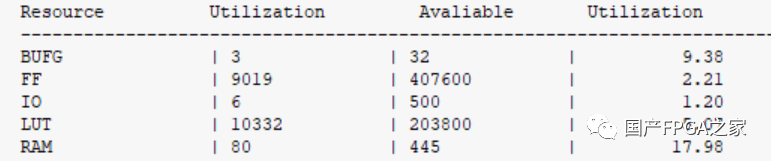

加固完成后,TMR工具可以统计出准确的资源使用情况。

图15TMR工具加固后资源统计

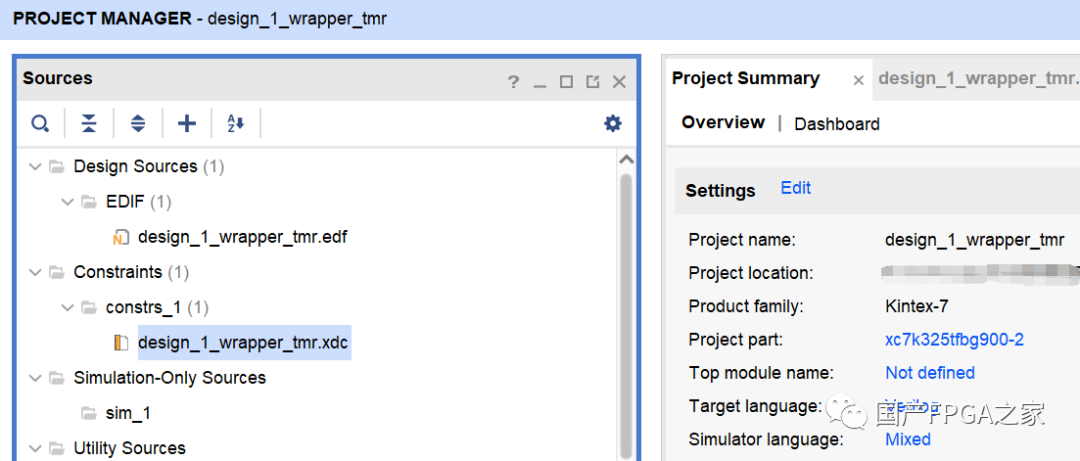

TMR工具自动创建加固后工程并自动添加约束文件。

图16 TMR PSOT工程

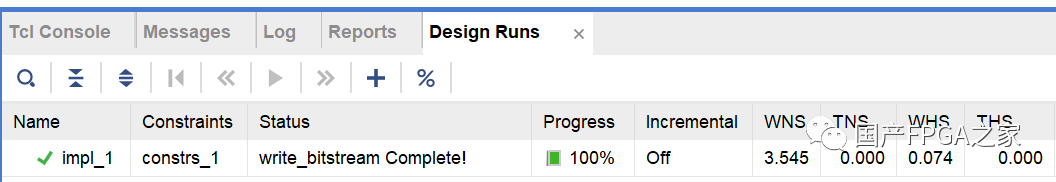

执行Implementation和Generate Bitstream。

图17 POST工程完成IMPL和BITGEN

2.3 故障注入验证

Microblaze System采用TMR进行加固可靠性得到提升,TMR加固推荐采用DTMR/GTMR加固方式。Microblaze System中存储器部分选择的是ECC加固,需要针对Block Memroy进行故障注入验证。

图18 BRAM故障注入测试 故障注入验证结果如下:

1)存储区不加固,随机注入70~100bit错,系统异常

2)存储区ECC纠错,随机注入700~800bit错,系统异常

3)存储区ECC纠错+回写,随机注入10000bit错,系统仍正常工作 Microblaze采样高可靠方案进行加固后可靠性得到提升,采用ECC纠错+自刷新措施可靠性最高。软核除了在FPGA内部进行软加固外,还应该采用外部Scrubber来消除CRAM的累积错误,这样经过多种加固措施后的软核应该能满足大部分的空间应用需求。

审核编辑:刘清

-

用SOI技术提高CMOSSRAM的抗单粒子翻转能力2010-04-22 0

-

抗辐射加固封装国产存储器的电子辐照试验2010-04-22 0

-

特征工艺尺寸对CMOS SRAM抗单粒子翻转性能的影响2010-04-22 0

-

Xilinx SRAM型FPGA抗辐射设计技术研究2012-08-17 0

-

请教:基于fpga软核的c语言编程2014-03-04 0

-

ISE中应用MicroBlaze软核2015-12-14 0

-

FPGA在航天领域有什么应用2020-07-07 0

-

【正点原子FPGA连载】第一章MicroBlaze简介--摘自【正点原子】达芬奇之Microblaze 开发指南2020-10-16 0

-

求一款双MicroBlaze软核处理器的SOPC系统设计2021-03-16 0

-

基于microblaze的vivado开发流程2022-01-18 0

-

反熔丝型FPGA单粒子效应及加固技术研究2016-01-04 485

-

基于TDICE单元的SRAM抗SEU加固设计2017-01-07 587

-

SRAM型FPGA在轨会遇到的问题及其影响2023-08-11 1402

-

讲解一下SRAM型FPGA在轨会遇到的问题及其影响2023-08-11 1317

-

SRAM型FPGA的抗辐照加固设计2023-08-15 2242

全部0条评论

快来发表一下你的评论吧 !