高速PCB走线的3-W原则

PCB设计

2495人已加入

描述

PCB走线之问会产生串扰现象,这种串扰不仅仅会在时钟和其周围信号之间产生,也会发生在其他关键信号上,如数据、地址、控制和输入/输出信号线等,都会受到串扰和耦合影响。为了解决这些信号的串扰问题,布线应遵循3-W原则。

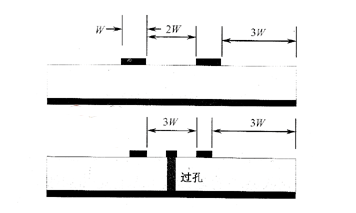

3-W原则就是让所有的信号走线的间隔距离满足:走线边沿之间的距离应该大于或等于2倍的走线宽度,即两条走线中心之间的距离应该大于或等于走线宽度的3倍。对于靠近PCB边缘的走线,PCB边缘到走线边缘的距离应该大于3倍的走线宽度。如果走线之间有过孔,那么走线间距应大于或等于走线宽度的3倍,如图所示。

图 走线的3-W原则

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

#硬声创作季 高速PCB信号走线常见的九大规则(二)Mr_haohao 2022-09-13

-

#硬声创作季 高速PCB信号走线常见的九大规则(三)Mr_haohao 2022-09-13

-

#硬声创作季 高速PCB信号走线常见的九大规则(一)Mr_haohao 2022-09-13

-

什么是PCB走线的3W原则#电路设计小鱼教你模数电 2022-10-12

-

【PCB小知识 6 】3W原则2015-12-12 0

-

【快点PCB-3W和20H原则】2016-09-06 0

-

硬件工程师谈高速PCB信号走线的九个规则2018-09-20 0

-

【转】高速PCB之EMC 47原则2018-11-23 0

-

高速PCB走线的3-W原则2018-11-27 0

-

高速PCB布线差分对走线2018-11-27 0

-

带你读懂PCB设计的3W原则、20H原则及五五原则2019-05-08 0

-

PCB设计中,3W原则、20H原则和五五原则都是什么?2020-09-27 0

-

3W原则是什么2022-01-26 0

-

PCB走线不要随便拉2023-12-12 0

-

高速PCB布板原则2015-12-25 1065

全部0条评论

快来发表一下你的评论吧 !