芯片尺寸封装技术解析

制造/封装

描述

所谓芯片尺寸封装就是CSP (Chip Size Package或Chip Scale Package)。JEDEC(美国EIA协会联合电子器件工程委员会)的JSTK一012标准规定,LSI芯片封装面积小于或等于LSI芯片面积的120%的产品称之为CSP。CSP技术的出现确保VLSI在高性能、高可靠性的前提下实现芯片的最小尺寸封装(接近裸芯片的尺寸),而相对成本却更低,因此符合电子产品小型化的发展潮流,是极具市场竞争力的高密度封装形式。本文从CSP的特点、类别和制作上艺以及生产和研发等几个方面详细论述这种先进的封装技术,并提出几点建议。

CSP的特点

CSP实际上是在BGA封装小型化过程中形成的,所以有人也将CSP称之为μBGA(微型球栅阵列,现在仅将它划为CSP的一种形式),因此它自然地具有BGA封装技术的许多优点。

1.封装尺寸小

CSP是目前体积最小的VLSI封装之一。一般,CSP封装面积不到0.5 mm,而间距是QFP的1/10,BGA的1/3~l/10。

2.可容纳引脚的数最多

在各种相同尺寸的芯片封装中,CSP可容纳的引脚数最多,适宜进行多引脚数封装,甚至可以应用在I/0数超过2000的高性能芯片上。例如,引脚间距为0.5 mm,封装尺寸为40 mm×40 mm的QFP,引脚数最多为304根,若要增加引脚数,只能减小引脚间距,但在传统工艺条件下,OFP难以突破0.3 mm的技术极限;与CSP相提并论的是BGA封装,它的引脚数可达600~1000根,但值得重视的是,在引脚数相同的情况下,CSP的组装远比BGA容易。

3 .电性能优良

CSP的内部布线长度(仅为0.8~1.O mm)比QFP或BGA的布线长度短得多,寄生引线电容、引线电阻及引线电感均很小,从而使信号传输延迟大为缩短。

CSP的存取时间比QFP或BGA短1/5~1/6左右,同时CSP的抗噪能力强,开关噪声只有DIP(双列直插式封装)的1/2。这些主要电学性能指标已经接近裸芯片的水平,在时钟频率己超过双G的高速通信领域,LSI芯片的CSP将是十分理想的选择。

4 .测试、筛选、老化操作容易实现

MCM技术是当今最高效、最先进的高密度封装之一,其技术核心是采用裸芯片安装,优点是无内部芯片封装延迟及大幅度提高了组件封装密度,因此未来市场令人乐观。但它的裸芯片测试、筛选、老化问题至今尚未解决,合格裸芯片的获得比较困难,导致成品率相当低,制造成本很高;而CSP则可进行全面老化、筛选、测试,并且操作、修整方便,能获得真正的KGD芯片,在目前情况下用CSP替代裸:芯片安装势在必行。

5 .散热性能优良

CSP封装通过焊球与PCB连接,由于接触面积大,所以芯片在运行时所产生的热量可以很容易地传导到PCB上并散发出去;而传统的TSOP(薄型小外形封装)方式中,芯片是通过引脚焊在PCB上,焊点和PCB板的接触面积小,使芯片向PCB板散热相对困难。测试结果表明,通过传导方式的散热量可占到80%以上。同时,CSP芯片正面向下安装,可以从背面散热,且散热效果良好。例如松下电子开发的10 mm×10mm CSP的热阻为35℃/W,而TSOP、QFP的热阻则可达40℃/W。若通过散热片强制冷却,CSP的热阻可降低到4.2℃/W,而QFP的则为11.8℃/W。

6. 封装内无需填料

大多数CSP封装中凸点和热塑性粘合剂的弹性很好,不会因晶片与基底热膨胀系数不同而造成应力,因此也就不必在底部填料,省去了填料时间和填料费用,这在传统的SMT封装中是不可能的。

7 .制造工艺、设备的兼容性好

CSP与现有的SMT工艺和基础设备的兼容性好,而且它的引脚间距完全符合当前使用的SMT标准(0.5~1 mm),无需对PCB进行专门设计,而且组装容易,因此完全可以利用现有的半导体工艺设备、组装技术组织生产。

CSP的分类

目前全球有50多家IC厂商生产各种结构的CSP产品。根据目前各厂商的开发情况,可将CSP封装分为下列主要类别:

1.柔性基板封装CSP

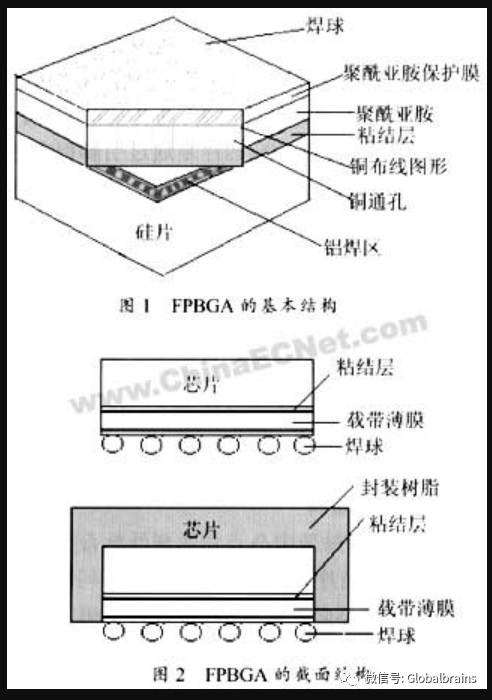

柔性基板封装CSP是由日本的NEC公司利用TAB技术研制开发出来的一种窄间距的BGA,因此也可以称之为FPBGA。这类CSP封装的基本结构如图1所示,截面结构如图2所示。主要由IC芯片、载带(柔性体)、粘接层、凸点(铜/镍)等构成。载带是用聚酰亚胺和制箔组成。采用共晶焊料(63%Sn一37%Pb)作外部互连电极材料。

其主要特点是结构简单,可靠性高,安装方便,可利用传统的TAB(Tape Automated Bonding)焊接机进行焊接。

2.刚性基板CSP

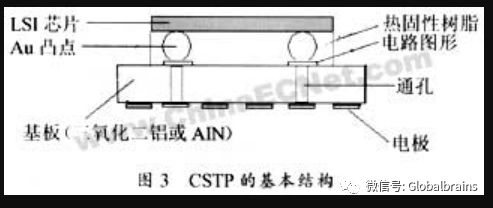

刚性基板CSP是由日本的Toshiba公司开发的一种陶瓷基板超薄型封装,因此又可称之为陶瓷基板薄形封装CSTP(Ceramic Substrate Thin Package)。其基本结构见图3。它主要由芯片、氧化铝(Al2O3)基板、铜(Au)凸点和树脂构成。通过倒装焊、树脂填充和打印3个步骤完成。它的封装效率(芯片与基板面积之比)可达到75%,是相同尺寸的TQFP的2.5倍。

3.引线框架式CSP

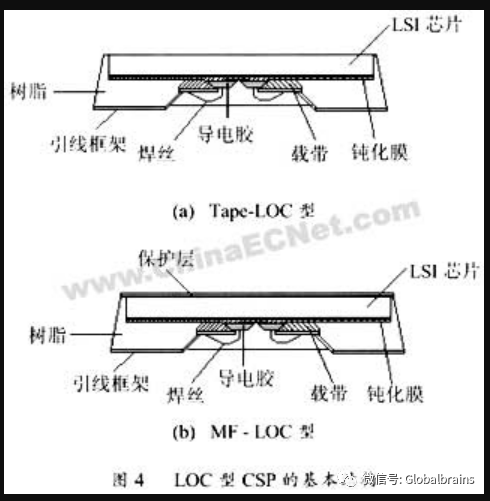

引线框架式CSP是由日本的Fujitsu公司研制开发的一种芯片上引线的封装形式,因此也被称之为LOC(Lead On Chip)形CSP。通常情况下分为Tape-LOC型和MF- LOC型(Mul-ti-frame-LOC)两种形式,其基本结构如图4所示。

由图可知,这两种形式的LOC形CSP都是将LSI芯片安装在引线框架上,芯片面朝下,芯片下面的引线框架仍然作为外引脚暴露在封装结构的外面。因此,不需要制作工艺复杂的焊料凸点,可实现芯片与外部的互连,并且其内部布线很短,仅为0.1 mm左右。

4.焊区阵列CSP

焊区阵列CSP是由日本的Panasonic公司研制开发的一种新型封装形式,也被称之为LGA(Land Grid Array)型CSP,主要由LSI芯片、陶瓷载体、填充用环氧树脂和导电粘结剂等组成。这种封装的制作工艺是先用金丝打球法在芯片的焊接区上形成Au凸点,然后在倒装焊时,在基板的焊区上印制导电胶,之后对事先做好的凸点加压,同时固化导电胶,这就完成了芯片与基板的连接。导电胶由Pd-Ag与特殊的环氧树脂组成,固化后保持一定弹性,因此,即使承受一定的应力,也不易受损。表1示出了其材料结构与一些基本参数。

5.微小模塑型CSP

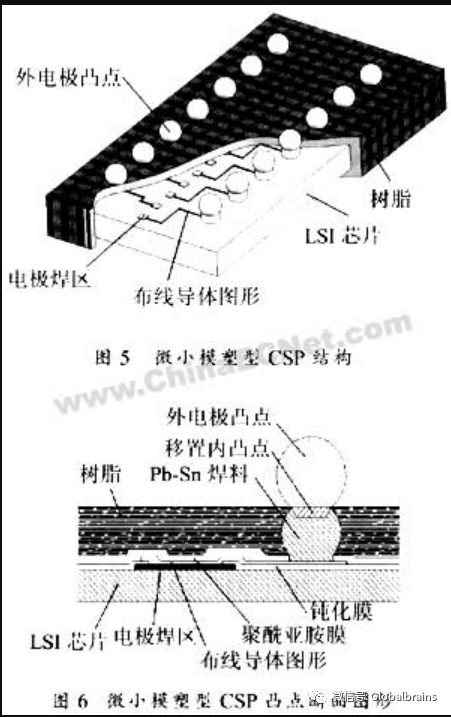

微小模塑型CSP是由日本三菱电机公司研制开发出来的一种新型封装形式。它主要由IC芯片、模塑的树脂和凸点等构成。芯片上的焊区通过在芯片上的金属布线与凸点实现互连,整个芯片浇铸在树脂上,只留下外部触点。这种结构可实现很高的引脚数,有利于提高芯片的电学性能、减少封装尺寸、提高可靠性,完全可以满足储存器、高频器件和逻辑器件的高I/O数需求。同时由于它无引线框架和焊丝等,体积特别小,提高了封装效率。基本结构如图5所示,凸点断面图形如图6所示。

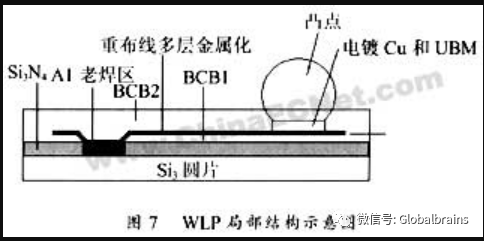

微小模塑型CSP的制作工艺:首先在LSI芯片上制作连接焊区和外引脚的金属布线图形,制出Pb-Sn焊料浸润性良好的底层金属,制出聚酰亚胺缓冲层,在聚酰亚胺开口区域采用蒸发光刻方法形成Pb-Sn层;然后,将上述经过再布线的芯片到装焊在易于移植金凸点的框架上,使之于芯片焊区一一对应,加热加压,Pb-Sn熔化后就使框架上的金属凸点(一般为Cu)移植到芯片上;最后,模塑封装,脱模去除毛刺,形成外电极焊球。(6)圆片级CSP。圆片级CSP封装(Wafer一Level Package)由ChipScale公司开发的此类封装见图5。它是在圆片前道工序完成后,直接对圆片利用半导体工艺进行后续组件封装,利用划片槽构造周边互连,再切割分离成单个器件。WLP主要包括两项关键技术即再分布技术和凸焊点制作技术。它有以下特点:①相当于裸片大小的小型组件(在最后工序切割分片);②以圆片为单位的加工成本(圆片成本率同步成本);③加工精度高(由于圆片的平坦性、精度的稳定性)。圆片级CSP的局部结构示意图如图7所示。

与其他各类CSP相比,圆片级CSP只是在IC工艺线上增加了重布线和凸点制作两部分,并使用了两层BCB和PI作为介质和保护层,所使用的工艺仍是传统的金属淀积、光刻、蚀刻技术,最后也无需模塑或底部下填充其他材料。圆片级CSP从晶圆片开始到做出器件,整个工艺流程一起完成,并可利用现有的标准SMT设备,生产计划和生产的组织可以做到最优化;硅加工工艺和封装测试可以在硅片生产线上进行而不必把晶圆送到别的地方去进行封装测试;测试可以在切割CSP封装产品之前一次完成,因而节省了测试的开支。总之,WLP成为未来CSP的主流已是大势所驱。

除以上列举的几类封装结构外,还有许多符合CSP定义的封装结构形式这里就不再赘述。

审核编辑:汤梓红

-

详解芯片尺寸封装(CSP)类型2023-12-22 710

-

未来推动芯片尺寸微缩的五种技术2014-01-04 0

-

关于读取芯片尺寸问题。2016-03-24 0

-

简述芯片封装技术2018-09-03 0

-

晶圆级芯片封装有什么优点?2019-09-18 0

-

莱迪思推出晶圆级芯片尺寸封装(WLCSP) MachXO2 PLD系列2011-09-09 2136

-

适用于DA4580蓝牙芯片的QFN40芯片尺寸及推荐PCB封装资料免费下载2021-02-02 1933

-

HFAN-08.0.1:了解粘合坐标和物理芯片尺寸2023-02-20 662

-

晶圆级芯片尺寸封装-AN104392023-03-03 246

-

倒装芯片尺寸级封装工艺流程与技术2023-05-04 2883

-

圆片级芯片尺寸封装工艺流程与技术2023-05-06 2082

-

HFAN-08.0.1: 了解粘合坐标和物理芯片尺寸2023-06-16 400

-

先进封装之面板芯片级封装(PLCSP)简介2023-06-19 1044

-

32位单片机晶圆级芯片尺寸封装(WLCSP)2023-09-19 289

-

32位单片机晶圆级芯片尺寸封装(WLCSP)2023-09-19 299

全部0条评论

快来发表一下你的评论吧 !