ESD的干扰模式有哪几种?ESD干扰机理分析

电子说

描述

1. ESD的干扰模式

ESD以共模干扰方式对控制器进行干扰,主要有以下几种形式:

- ESD放电中形成的场耦合,一般发生在接地点良好,但接地位置附近有敏感信号或走线的情况:

- ESD放电电流在接地阻抗路径中形成噪声电压Vnoise干扰敏感设备,一般发生在接地不良,接地阻抗较大的情况;

- ESD放电电流直接注入敏感信号中,一般发生在对pin进行ESD注入实验的情况。

2. 结构地分析

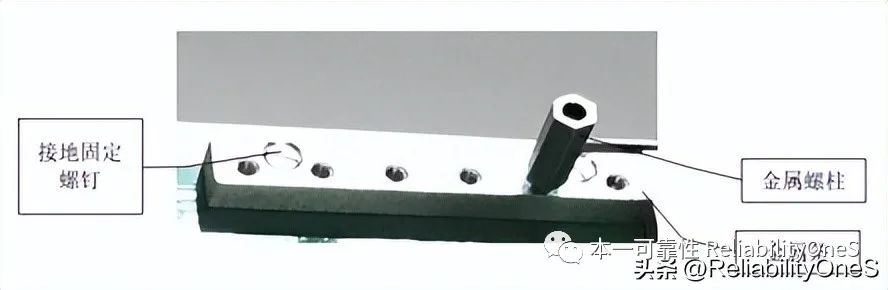

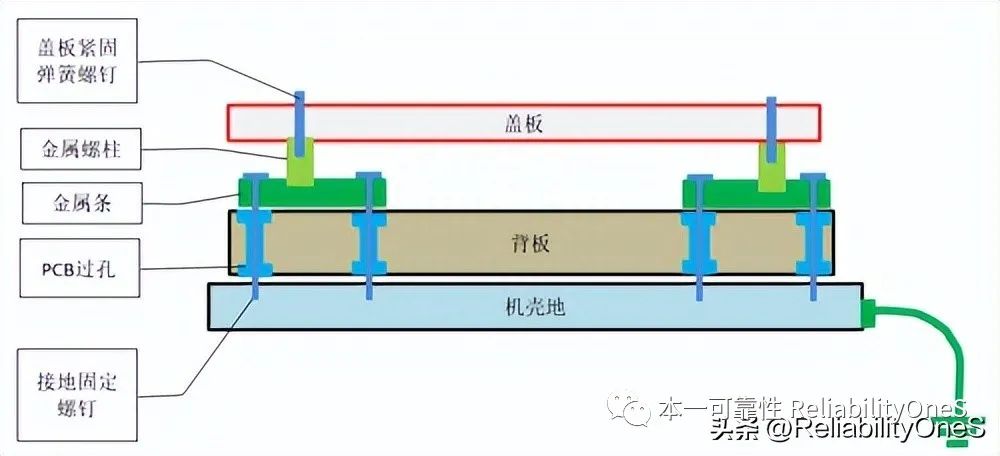

控制器盖板接地的结构层次:盖板紧固弹簧螺钉→金属螺柱→金属条→接地固定螺钉→机壳地。PCB过孔无接地铜盘,与金属条和机壳均无搭接。金属条与机壳的搭接仅仅通过螺纹进行,搭接不可靠,阻抗大,结构接地详见图5所示。

盖板接地点实物图

盖板接地结构示意图

3. 干扰路径与等效机理电路分析

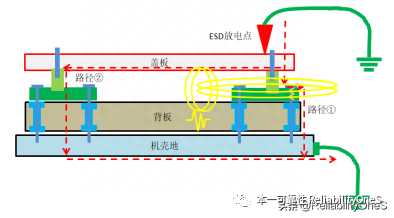

(1)盖板与机壳地间的接地良好工况

当盖板与机壳地间的接地良好时,阻抗足够低,与机壳形成等电位搭接,无压差。

ESD的主要放电路径为图6中的①和②,因①的接地物理路径较近,大部分干扰会从①路径中流到大地。流过路径①附近的电流形成的干扰场,会串扰周围的敏感信号或敏感走线。

图6 ESD放电路径示意图

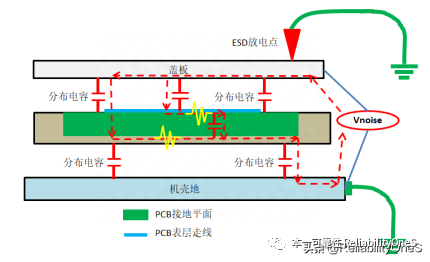

(2)盖板与机壳地间的接地不良工况

当盖板与机壳地间的接地搭接较差时(搭接阻抗较大),ESD放电电流会在搭接点处形成噪声电压Vnoise。

噪声电压通过盖板与PCB板件的分布电容,形成干扰电流流过PCB,使得敏感干信号受干扰,参见图7所示。

图7接地不良的ESD耦合机理示意图

4. 干扰噪声估算

通过接地阻抗测定与接地点变更ESD实验结果,结合ESD的干扰机理,可以确定控制器为ESD放电电流在接地阻抗路径中形成噪声电压Vnoise ,干扰了内部敏感信号。

(1)PCB与结构件间的分布电容估算

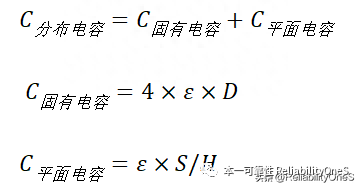

PCB板与盖板间的分布电容可用以下公式进行估算:

(2)盖板与机壳间搭接处的噪声电压估算

6KV接触放电的放电电流峰值实测约为24A左右,接触阻抗为0.3欧姆,电压约为7.2V。

注:盖板与机壳间的搭接阻抗为万用表测试结果,实际的ESD频段的搭接阻抗值要大于0.3Ω,本文暂以0.3Ω为例进行计算说明.

(3)流过背板的电流

I1=C2πfU=33pF*2*3.14*1.2GHz*7.2=0.25A。

注:为方便计算,ESD频段扩展到1.2GHz。

(4)流经背板PCB参考地平面的噪声电压

Vnoise=I1*Z=0.25A*3mΩ=0.75mV;

注:PCB的铺地平面阻抗一般为mΩ级别,结合背板的过孔数量,估算PCB铺地平面阻抗为3mΩ。

(5)流经背板PCB表层走线的噪声电压

I2= C2πfU=3pF23.141.2GHz7.2=0.025A(流过通讯指示灯走线的电流)

Vnoise=L*di/dt=300nH*0.025A/(0.8ns)=9.4V。

注:背板表层通讯指示灯为最长走线,长度为20cm左右,走线宽度为10mil,电感量为300nH左右。指示灯走线与盖板间的分布电容约为3pf。

5. 思考与启示

- ESD干扰以共模形式串入PCB线路或通过空间场耦合干扰敏感信号,需要解耦分析;

- 对于接地点可靠性的排查,可通过人为改变接地位置进行故障问题的分析;

- ESD抑制的一大手法是接地,要确保放电点与机壳地搭接的可靠性,保证搭接阻抗在ESD频段范围内足够小,不足以形成干扰电压;

- PCB敏感信号或与敏感信号相关的信号线,避免在表层长距离走线而引起的干扰,无法避免时,注意信号换板连接器附近的滤波处理;

- ESD敏感信号在设计前期需要进行ESD干扰评估,特别是噪声等级的评估,有利于抑制器件的选型,同时在PCB板进行干扰风险规避是成本最低,效果最好的方法;

- ESD的抑制手段多样化,除了接地对ESD干扰进行泄放外,还可通过滤波、屏蔽、瞬态抑制、隔离、放电敏感距离控制、采用绝缘类材料阻断放电等等手段进行抑制,结合设计需求落地;

-

ESD的保护机理和主要测试模式有哪些?2023-11-07 481

-

ESD传递模式有哪几种?如何提高ESD保护?2021-04-23 0

-

电梯的干扰表现形式有哪几种?2021-06-02 0

-

ESD事件保护的系统级设计方法有哪几种?2021-06-08 0

-

请问一下元器件失效机理有哪几种?2021-06-18 0

-

MBD有哪几种设计模式?2021-10-13 0

-

伺服电机模式有哪几种?2021-10-29 0

-

STM32的启动模式有哪几种?2021-11-23 0

-

IO口模式有哪几种?2021-11-25 0

-

bootloader的升级模式有哪几种?2021-11-26 0

-

ADC的转换模式有哪几种?2021-12-02 0

-

GPIO工作模式有哪几种?2022-02-11 0

-

手机中ESD和EMI干扰2009-11-20 887

-

ESD模型有哪几种你知道吗?2023-05-09 1216

-

ESD干扰机理分析2023-09-26 518

全部0条评论

快来发表一下你的评论吧 !