PCB电源完整性完整指南:从电路板到封装

描述

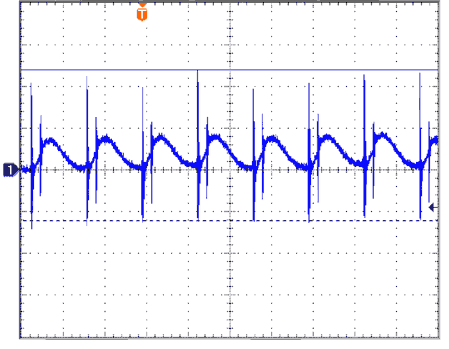

尽管看似简单,但PCB和高级封装中的功率传输仍然是设计人员面临的最大挑战之一,尤其是在数据中心、边缘计算、移动设备和电信/网络等环境中。在这些环境中,大量数据通过极高的数据速率通道传输,尽管我们非常关注信号完整性,但如果没有稳定的电源,这些系统都无法工作。电源完整性发生在元件级和PCB级,正如其他人在本博客中提到的那样,电源完整性问题会造成信号完整性问题(抖动、电源/接地反弹、EMI)。虽然大多数更简单的电源完整性指南往往只关注PCB级别,但PCB和封装必须协同工作才能为互连提供稳定的电源。本指南将尝试为PCB设计人员提供电源完整性的综合概念视图。虽然设计人员通常无法控制其封装,但他们可以采取措施确保其PCB和元件封装协同工作以提供稳定的电源。我将概述一些确保这些领域的电源完整性的主要方法,涵盖从叠层设计到最佳电容器选择的各个方面。什么决定了PCB中的电源完整性?电源完整性在交流和直流中都是一个概念;在直流情况下,我们关心铜线的尺寸是否合适以确保低直流压降。如果设计PCB时未考虑电源完整性,在电源轨上观察到的电压可能如下图所示。在I/O切换的阶段,从PCB的供电网络(PDN)拉出的电流脉冲会激发电源总线上的瞬变。逻辑电路重复切换示例如下所示。

- 它们在输出信号上显示为噪声(包括时序噪声和信号电平噪声),可能导致逻辑电平的误读

- 它们产生的辐射EMI可以从电路板上测量,通常是从边缘测量

|

元素 |

对电源完整性的影响 |

|

电源和接地层对 |

|

|

离散电容器 |

|

|

电容器封装和过孔电感 |

|

|

嵌入式电容 |

|

|

封装寄生效应 |

|

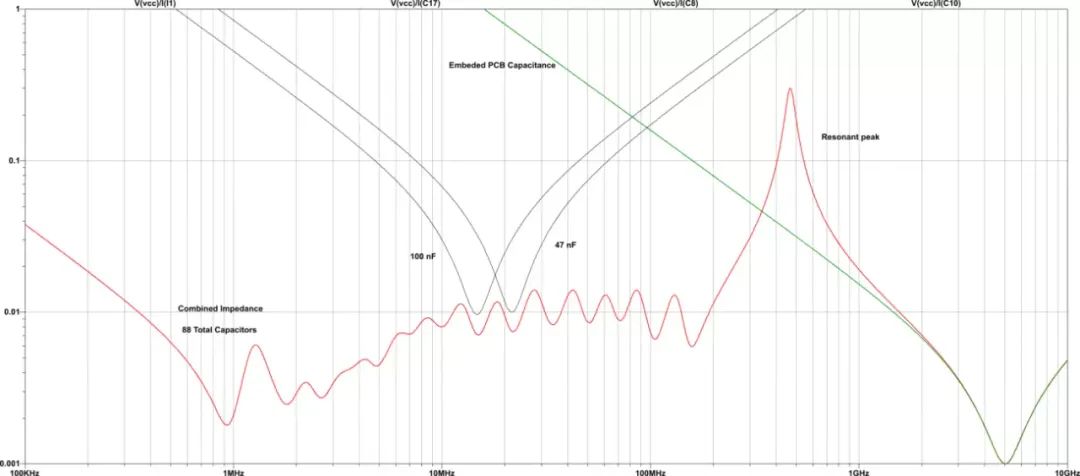

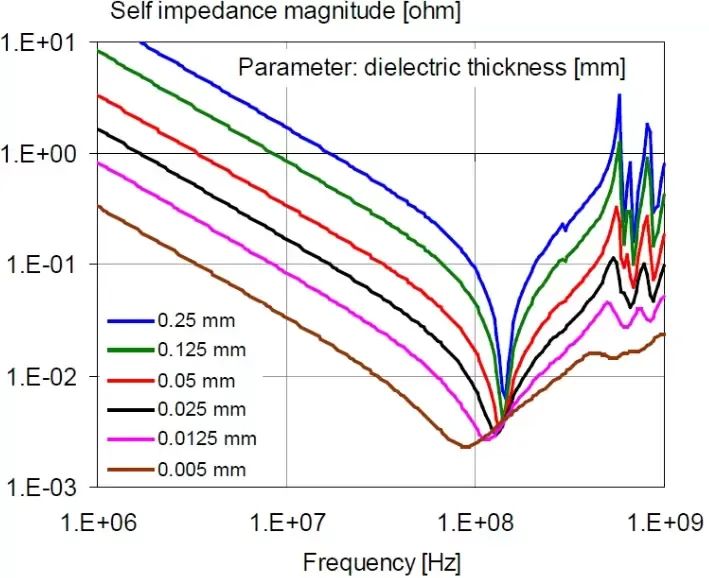

总的来说,这些元素将决定PDN的阻抗频谱。PDN的各种贡献因素如下图所示,这些贡献大致按频率范围划定。此处显示的阻抗谱由大量电容器构成,这是以快速边沿速率运行的、具有高I/O计数的数字处理器的典型特征。

PDN拓扑

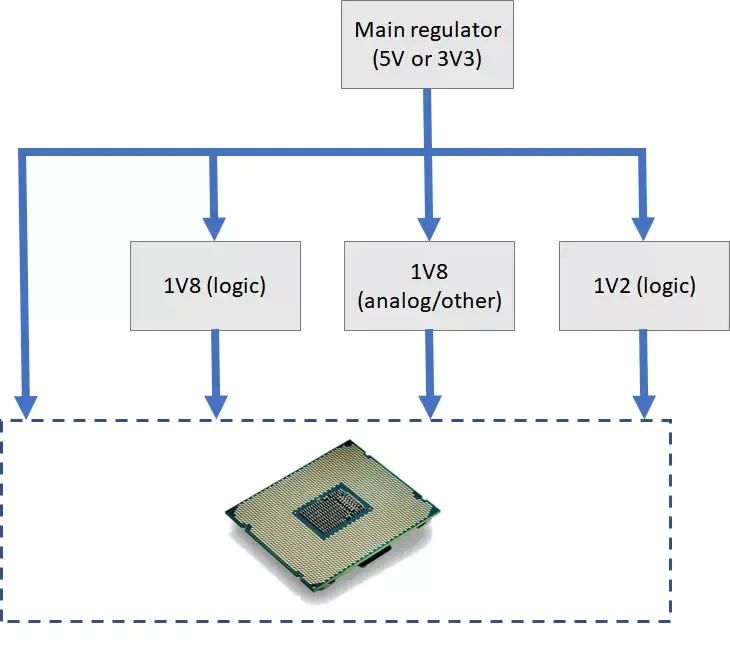

所有为高级处理器供电的PDN都是多端口网络。它们需要多重稳定电压,从高值到低逻辑电平。在高引脚数处理器上,电压从较高逻辑电平(5V0或3V3)下降到低至0V8是很常见的。

定义高级处理器PDN的电源树如下所示。该示例旨在说明如何构建不同的电源轨,这些轨道来自为整个系统供电的主电源或稳压器。

处理器的PDN拓扑示例需要四个电压逐渐降低的不同电源轨

处理器的PDN拓扑示例需要四个电压逐渐降低的不同电源轨

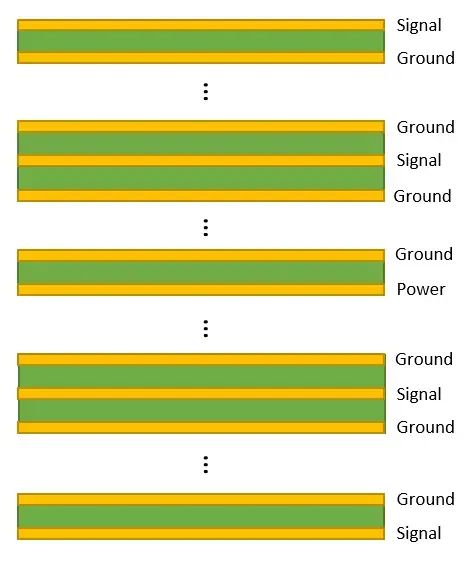

- 在中档频率下提供更高的电容,从而降低阻抗(高达1 GHz)

- 将与电源/接地层对相关的PDN谐振移至较低频率

- 抑制与电源/接地层对相关的GHz范围内的PDN谐振峰值

- 将与平面电容相关的PDN阻抗谷值(从0.1到1 GHz)移至较低频率

- 用于大型高速处理器的电压调节器模块(VRM)

- 原理图和PCB布局中的模拟

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- pcb

-

确保信号完整性的电路板设计准则2009-05-24 0

-

高速信号的电源完整性分析2012-08-02 0

-

PCB设计中的电源信号完整性的考虑2013-10-11 0

-

信号完整性与电源完整性的仿真分析与设计2015-01-07 0

-

看我在设计电路板时是如何确保信号完整性的2015-01-07 0

-

如何确保PCB设计信号完整性2018-07-31 0

-

PCB电路中的电源完整性设计2018-09-11 0

-

信号完整性 & 电源完整性 谁更重要呢?2019-06-17 0

-

PCB电路中的电源完整性信号的质量问题2021-12-28 0

-

什么是电源和信号完整性?2021-12-30 0

-

信号完整性(SI)和电源完整性(PI)的基本原理理解2021-12-30 0

-

高速PCB电路板的信号完整性设计2017-11-08 1063

-

PCB设计指南提高电路板信号完整性的方法2022-04-22 2250

全部0条评论

快来发表一下你的评论吧 !