如何计算芯片内部自研IP模块的FIT的数值

描述

Q1

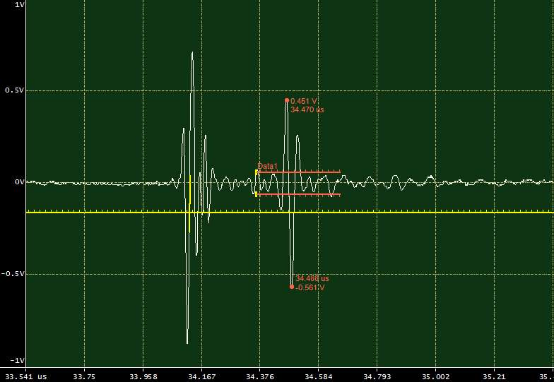

图中这个分层是哪里导致的?

A1

die attach,银浆分层,最好有个reference对比判断,看起来die attach的波幅太大了,找根因还是需要FA看看细节。

Q2

在芯片设计阶段,如何计算芯片内部自研IP模块的FIT的数值呢?

A2

在设计功能安全芯片的过程中计算硬件架构度量(SPFM,LFM,PMHF)中一般是根据IEC TR62380或是SN 29500等标准计算芯片总的failure rate,然后将failure rate分配到各功能模块,在配合各功能安全模块的诊断覆盖率计算芯片SPFM,LFM,PMHF。以确定芯片这几项指标是否达到对应ASIL等级要求,如果这几项指标不达标,说明芯片安全机制诊断覆盖率不够,芯片的架构设计需要继续优化。IEC TR62380是根据统计汇总出来的Mission profiles,建立一个由关于温度π(t),温差ΔT,芯片材料膨胀系数π(α)等因子组成的推测产品failure rate 的统计模型。

Q3

芯片裂纹、崩边的规定出自哪份jedec标准?

A3

JEDEC Standard No.22-B118A。

Q4

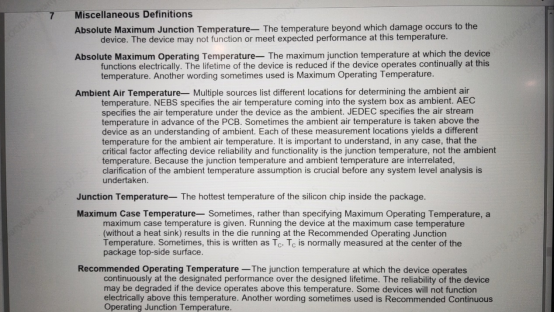

TJ-max(recommended) 和TJ-max(absolute)的区别是什么?

A4

TJ的解释。

Q5

怎么确定这两个温度呢,比如常规CMOS工艺,一般我们做可靠性都是Tj>125℃的。很多datasheet上只有一个TJ max是125℃,没有特别说是recommended还是absolute?

A5

absolute问fab和你们的DE;recommend要看你们怎么给客户规定了,也许产品能力有150℃,但data sheet只推荐125℃。

Q6

封装可靠性的TCT700,FT回测发现出现了两种失效,一种是内部数字电路逻辑失效了,另一种是电源的漏电变大了很多,这种怎么分析呀?

A6

看看是否有湿气进去造成漏电变大,做下SAT看看是否有分层造成逻辑失效,TCT评估封装的,主要和封装相关;可以烤一烤试试,或者清洁一下管脚,可能是接触电阻变大了。

Q7

为什么CUP芯片打线建议要用银合金,镀钯铜不建议用,是芯片pad架构跟常规芯片不一样吗?有没有知道详细些的?

A7

CUP芯片不允许有裂纹,合金线和金线软一点,作业性好一点;铜线力大,版图不合理的话焊球下方容易出现裂纹;芯片打线实际上是,共金工艺,使用了高温+超声波,达到融焊的效果,这样的话芯片受压力小,不容易破裂。所以对线材有要求,铜打线一般是压焊工艺,压力大,对于以前一些老工艺低成本的芯片可以用,但是芯片表面的PAD处理方式和金打线是不同的。不同的打线方式用不同的线材,这些芯片设计初期就要和晶圆厂沟通好,把后期封装打线方式都要考虑进去。

Q8

什么样的芯片出货使用卷带包装,什么样的该采用Tray盘出货,有没有什么规定的?

A8

QFP类的一般都是TRAY盘,SOP类的料管和卷带都有,DFN/QFN这类无外放引脚的看体积,卷带居多,5X5以上可以用TRAY盘,主要是太重,转塔式的测编吸不住。

Q9

现在一般的SMT,卷带上料和Tray盘上料是否都能支持的?Tray盘交货是否影响SMT的上料?

A9

对于SMT来说,卷带是效率最高的,能用卷带肯定优先用,实在没有才考虑其他方式。料管和TRAY盘设备方面都能支持,但要看工厂是否会配齐硬件。

Q10

消费类芯片工规的可靠性测试标准,HAST是必做项吗?

A10

HTOL、HAST目前都是必做项。

Q11

盛装芯片的tray盘,其表面阻抗范围是否有标准?

A11

10的9次方以下。

Q12

wafer超期需要做哪些验证?

A12

做MSL3看看有没有分层,也可以做快速ORT IR*3+UHAST48+TC100。

Q13

通常wafer在氮气柜中保存多久后,会认为是超期呢?

A13

general是3年的shelf life,自家产品可以和foundry再确认下。

Q14

关于ESD的验证,HBM、CDM、MM要怎么样去分解安排实验呢?

A14

JEDEC规范经过更新,已经明文说明MM模式已经能被CDM、HBM等覆盖,不需额外测MM。MM主要是在生产过程中的机械静电对芯片的直接放电伤害,中间没有电阻限流,所以通过电压值低于CDM、HBM。但是车规和其它特殊可靠性需求,部分客户还是有测MM的需求。

Q15

JEDEC中HBM和Latch up的判定条件仅仅是I/V的变化率吗?对功能测试有要求吗?

A15

Q16

对于已经塑封好的DFN产品,有什么方法可以使某一个Pin脚和中间的基岛相连接么?

A16

找季丰局部开盖,焊线连上,然后黑胶封上。

Q17

Thermal热点和OBIRCH热点分别适用哪种情况?缺陷漏电大于2mA是不是两种方式都能用?

A17

有compound用thermal,没有compound两种都可以。OBIRCH原理:激光束在IC表面扫描,激光束的部分能量被IC吸收转化为热量,造成被扫瞄区域温度变化,若IC金属互联机中存在缺陷或者空洞,这些区域附近的热量传导不同于其它的完整区域,则该区引起的温度变化会不同,从而造成金属电阻值改变。Thermal原理:利用InSb材质的探测器,接收失效点通电后产生的热辐射分布,藉此定位失效点位置。适应范围: 漏电,高阻抗,短路OBIRCH,Thermal都可以定位,其中带封装的样品/电容漏电短路/PCB板失效的使用Thermal定位,小电压漏电,小漏电优先使用OBIRCH定位。

Q18

封装铜线打线产品,线经约粗50um左右,大部分是裸铜线居多还是钯铜或者金钯铜线多?若是裸铜,原因是什么呢,没有Pd的话IMC不是会生长过快么?

A18

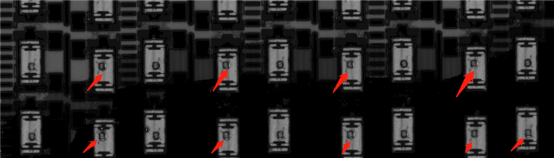

纯铜线只有价格优势的吧,镀金和钯主要还是为防止FAB氧化和一致性,提高焊接强度和CPK。镀钯应该是可以减缓IMC生长的,这点可以参考镀钯金线,因为金和铝更容易共金;不过使用纯铜线除了IMC还会有各种其他可靠性行问题,潮湿酸性环境也扛不住。铜铝imc只有在150度以上高温才会快速生长,这是我们1000小时HTOL后的IMC生产情况,只有薄薄一层,用的是金钯铜,参考如下:

Q19

先进制程中,这个操作电压下降,为何热载流子的光波长变得较长?这个怎么理解呢?

A19

这个应该这么理解,电压下降热载流子能量降低,光子能量(eV)*波长(nm)=1240;这个是光频率里面的,跟射频频率不同。

审核编辑:彭菁

-

手机厂商自研芯片或是下一个变革起点2017-05-27 0

-

Rokid自研芯片抢先看2020-06-05 0

-

苹果自研射频芯片?OPPO自研NPU芯片!芯片的国产替代需要跨越三个误区!2022-01-02 0

-

智绘微电子自研国产GPU芯片IDM929目前已完成设计2023-02-15 0

-

MPC5746B的FIT率如何计算?2023-04-06 0

-

求分享FS32K144HAT0VLH的SN29500数值标准FIT数据2023-04-10 0

-

轴流泵内部三维湍流场数值模拟2010-04-27 506

-

定子铁心风道板数值计算_徐国俊2017-01-01 466

-

用数值模拟仿真法计算电机内部流场分布2017-01-02 644

-

工程电磁场数值计算数值分析的数值基础2017-09-15 612

-

芯片IP是什么2021-12-13 20179

-

MATLAB中常用的数值计算和数值分析基础知识2023-07-07 1353

全部0条评论

快来发表一下你的评论吧 !