为什么时钟抖动技术可以降低EMI呢?

EMC/EMI设计

描述

时钟抖动技术适合于各种周期性的脉冲信号,典型的是电力电子设备中的PWM电压和数字电路中的时钟信号。这些周期性的脉冲信号是最强的干扰源,在进行电路设计时,需要特别考虑这些电路。

时钟抖动技术是近年来流行的一种降低周期性脉冲电路电磁干扰的技术。时钟抖动技术的原理从傅里叶变换。

由于周期性的脉冲信号经傅里叶变换后得到一系列离散的谱线,脉冲信号的能量集中在这些谱线的频率上,而非周期性脉冲的频谱则是连续的频谱,能量分布在所有频率上,某个特定频上的能量很小。

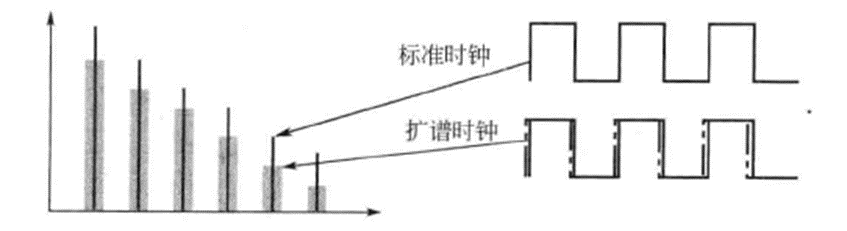

时钟抖动技术具体应用到时钟电路,就是让时钟的频率发生抖动。时钟时钟抖动的结果是时钟信号的谱线变宽,峰值降低,如图所示。

图 理想时钟信号和抖动时钟信号

图 时钟抖动的概念

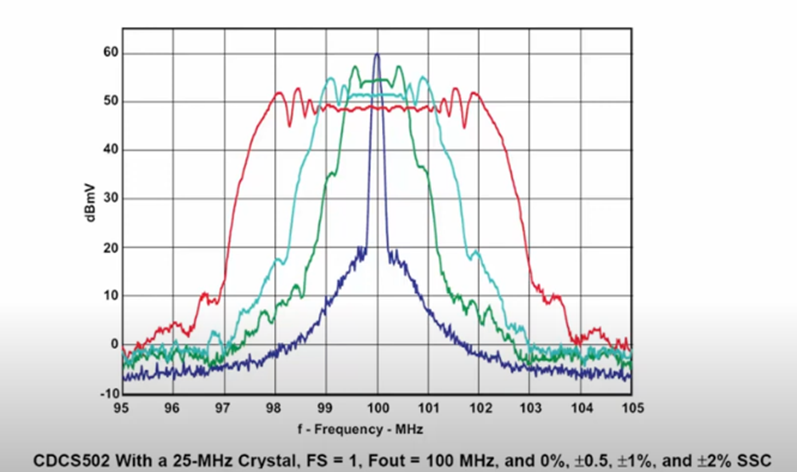

图 不同时钟抖动频率某一谐波频率附近的能量分布

为什么时钟抖动可以降低EMI的,我们可以这样理解这一概念,简单的说就是因为时钟抖动,将原本窄频的谐波发射能量打散,使得时钟信号的谱线变宽。

进行电磁兼容比如RE102测试时候,由于测试接收机带宽较窄的特点,使一部分能量落在接收带宽之外,从而使设备容易通过电磁兼容试验。

这项技术特别适合商业设备,因为商业设备出于成本的考虑,一般没有完善的屏蔽和滤波措施。军用设备需要通过的标准十分严格,扩潜时钟的作用不显著,主要依靠屏蔽和滤波。

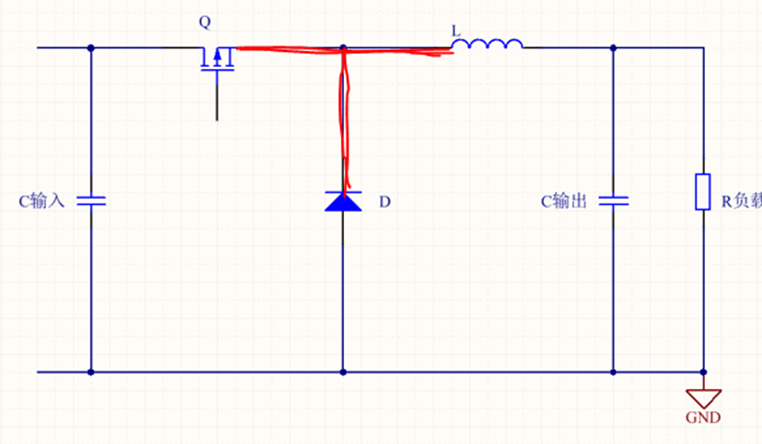

扩谱时钟的概念不仅应用在数字电路中,在其他一些脉冲电路中也可以应用,如在开关电源中用频率调制的PWM脉冲信号可以降低干扰发射。

我们以开关电源中的BUCK电路为例,当驱动Q1通断的PWM信号为扩谱时钟信号时,那么下图中红色共模电压区域的电压波形也会发生抖动,于是共模电压的谐波能量的谱线变宽,峰值降低,从而降低了开关电源每个谐波频率处的EMI。

图 开关电源BUCK电路

-

频率抖动改善EMI原理2013-02-01 0

-

请问时钟抖动如何处理?2018-11-12 0

-

有什么方法可以降低Linux的成本吗?2021-04-25 0

-

有什么方法可以降低LCD的噪声?2021-05-31 0

-

imx6q的GPU频率是否可以降低?2022-01-10 0

-

电源门控可以降低泄漏功耗吗2022-02-11 0

-

PowerXR EMI降低技术利用扩频时钟抖动2013-02-19 2517

-

时钟抖动的基础2017-04-01 852

-

通过频率抖动降低电源变换器设计中的干扰信号2019-04-08 1646

-

怎样降低PCB的EMI2019-08-20 3888

-

降低PCB设计EMI的方法2020-10-10 2725

-

MT-200:降低ADC时钟接口抖动2021-03-21 442

-

时钟抖动解秘—高速链路时钟抖动规范基础知识2022-11-07 329

-

使用DS1086作为微控制器时钟以降低EMI2023-03-01 635

-

面向验证工程师的PCIe扩频时钟(SSC)2023-05-26 5020

全部0条评论

快来发表一下你的评论吧 !