如何利用ADE Assembler检查电路中的floating gate

电子说

描述

如果你还在用“笨方法”一个节点一个节点地检查电路中是否有floating的gate,那么你真的该仔细阅读一下这次的内容,并尝试在项目中使用文中介绍的方法进行floating gate检查。

ADE Assembler介绍

ADE Assembler是一个交互式的、能同时进行多个仿真的集成环境,旨在将设计的所有部分结合在一起,以开始围绕制造的设计。

在这种环境中,用户可以合并设计的多个模块测试,包括变量、器件参数、工艺角、检查和断言以及它们的规范等,每个测试都可以有独立的设置内容。

ADE Assembler简单理解可以认为是ADE XL的一个升级版本,自然包含不少新功能,其中一项:circuit checks便是接下来要使用的功能。

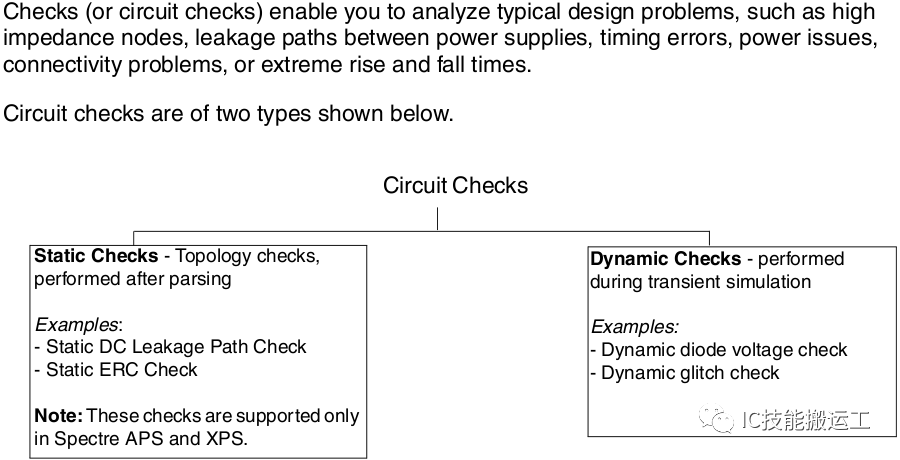

circuit check分成动态检查(dynamic check)和静态检查(static check)两种,静态检查利用拓扑结构实现,不需要运行瞬态仿真,动态检查需要运行瞬态仿真,接下来就需要利用动态检查实现电路中floating gate的检查。

为什么要检查floating gate 为什么要大费周章检查floating gate呢?原因很简单,电路中存在floating gate会产生很多不确定性影响。 最常见的是高阻节点处floating gate导致电路下电后漏电,有很多人通过电路下电后漏电情况间接判断电路中是否存在floating gate. 但是通过漏电间接检查电路中是否存在floating gate并不十分可靠,因为有些比较隐蔽的、可能存在漏电风险的高阻节点处floating gate通过这种方法可能检查不到,所以推荐使用下面介绍的方法。 使用ADE Assembler检查floating gate

注意:ADE Assembler是IC617及其之后版本的Cadence IC套件才有的工具,所以使用前需要先确认一下工具是否需要升级。

检查floating gate使用dynamic check,需要运行瞬态仿真,所以,检查结果体现的是在瞬态仿真过程中电路存在的floating gate, 通常会检查电路下电后是否存在floating gate,下面以此为例。

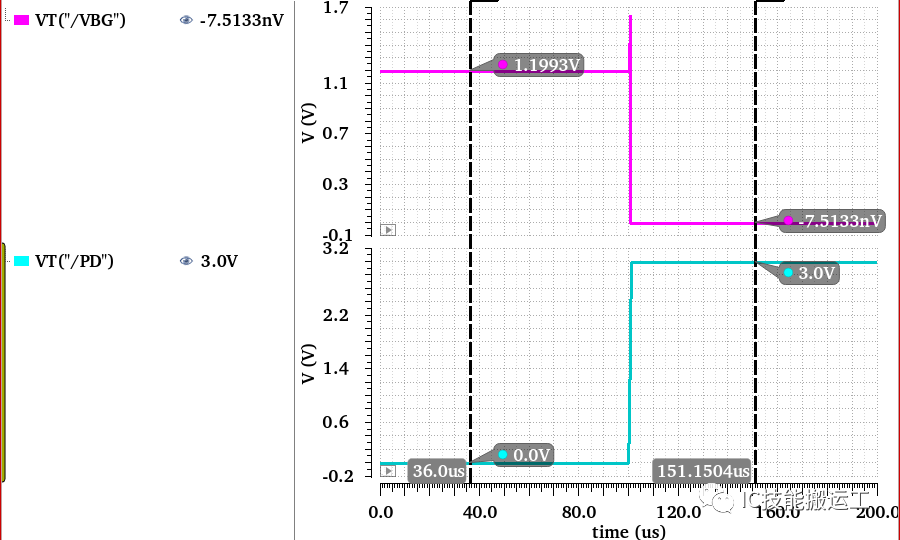

首先用ADE L仿真电路的下电过程,需要采用瞬态仿真,其它操作流程没有特别需要注意的地方,确认仿真成功运行之后,保存ADE L的设置,留作在ADE Assembler中使用。

以上是仿真带隙基准电路的下电过程,从仿真波形可以看出,电路正常工作一段时间之后被下电,包含了完整的工作过程和下电过程。

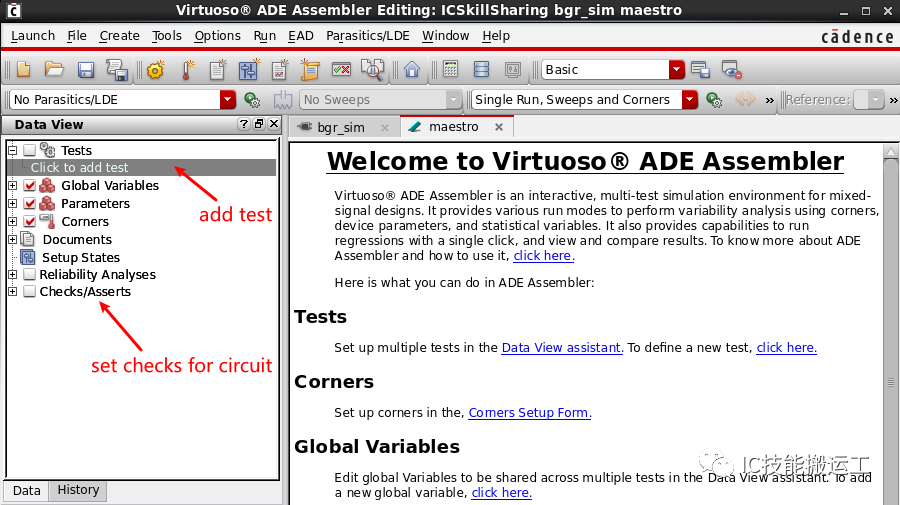

在原理图编辑界面,选择:Launch->ADE Assembler,根据实际情况选择「Create」或者「Open」选项,然后一路确认,即可启动ADE Assembler工具。

打开ADE Assembler界面如上图所示,基本与ADE XL一致,IC617和IC618界面也很相近,略有不同,但是不影响使用。

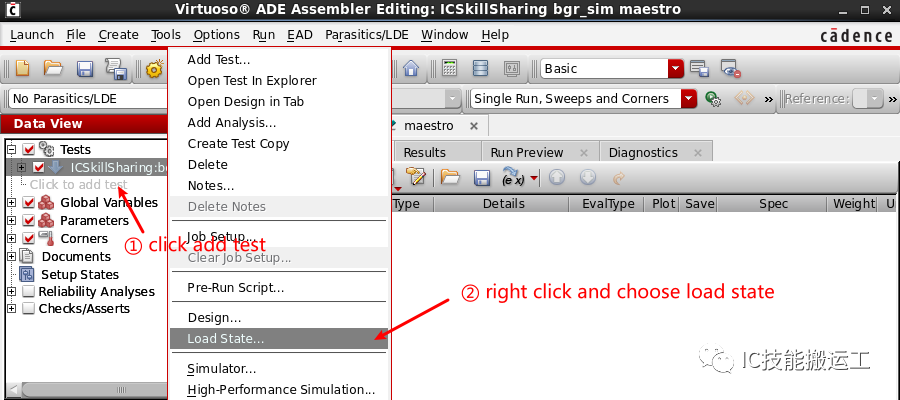

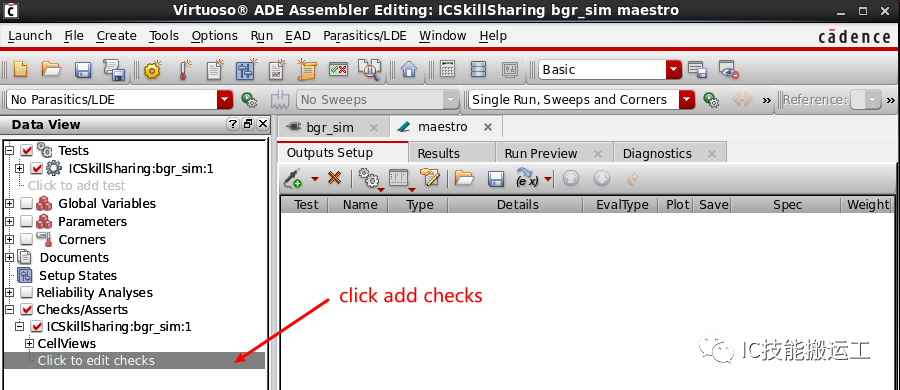

在左侧Data View的最下面,有一个Checks/Asserts项目,这就是电路检查项目,首先添加test设置,只需要load之前ADE L仿真保存的state即可。

接下来,勾选并展开Checks/Asserts选项,点击「Click to edit checks」,开始设置电路检查项目。

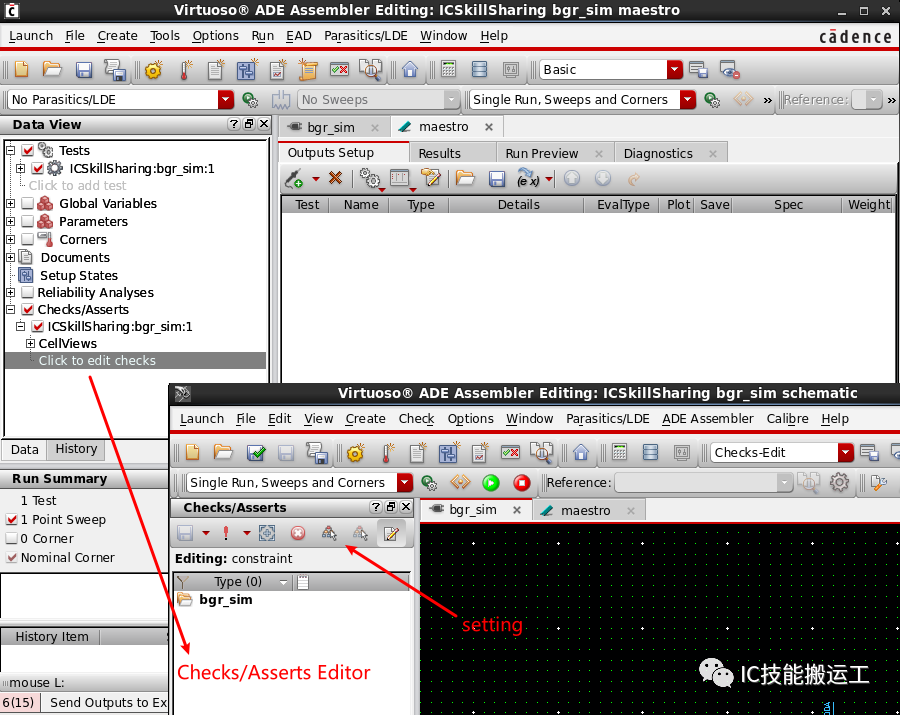

操作完成之后跳转到另一个窗口,并自动打开Checks/Asserts Editor,下面简单介绍一下该窗口的内容,部分截图来自Cadence手册。

上图中「setting」所指的区域包含对Checks的一些操作,比如:保存、删除、增加检查等。

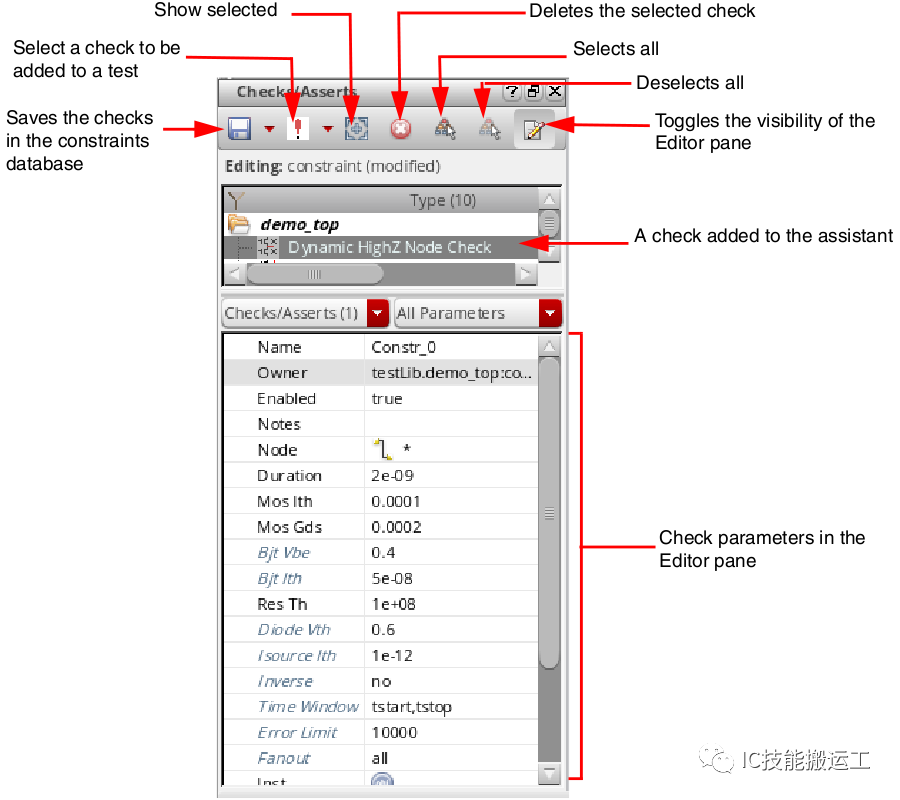

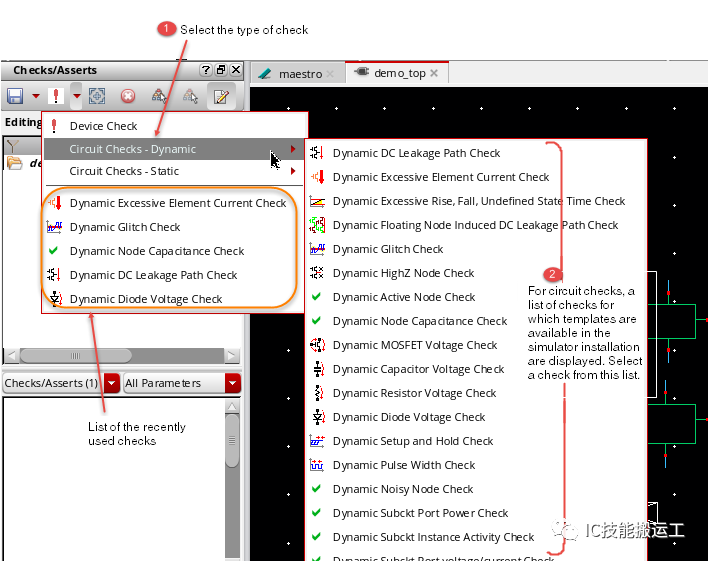

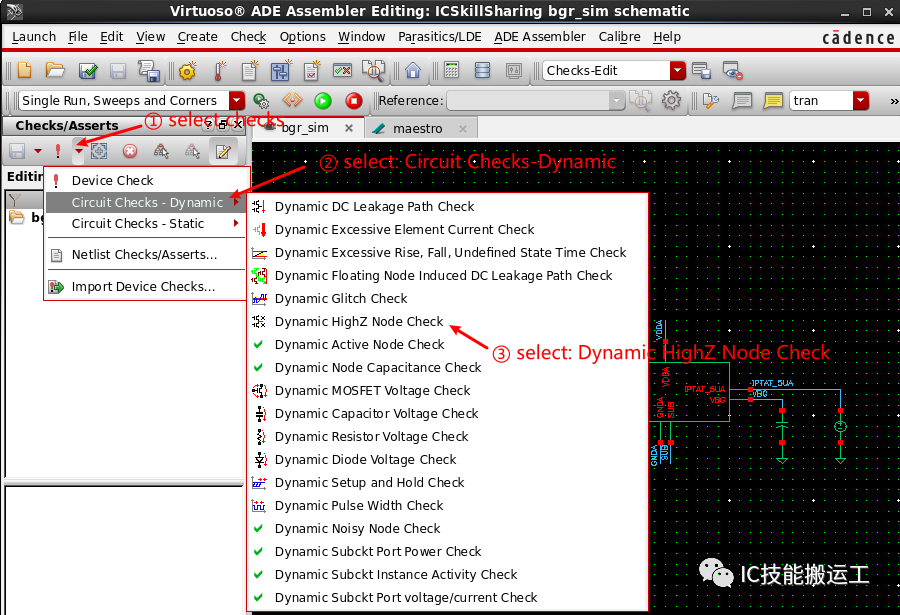

接下来点击上图中红色感叹号处的图表,弹出如下面所示的对话框,包含各种检查以及各种检查对应的具体细节。

依次选择:Circuit Checks-Dynamic->Dynamic HighZ Node Check,然后结束操作,可以看到左侧会多出一些信息。

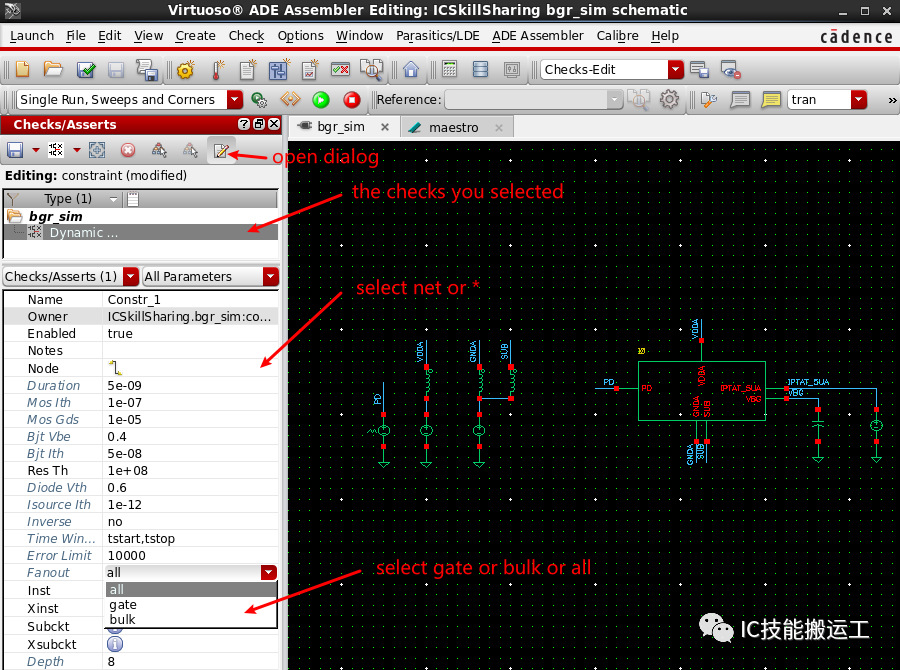

左侧信息栏内按照下图所示填写内容即可,主要注意两个地方,第一个是Node一栏,可以按照需要选择检查的信号,但是推荐检查所有信号,在里面填入「*」.

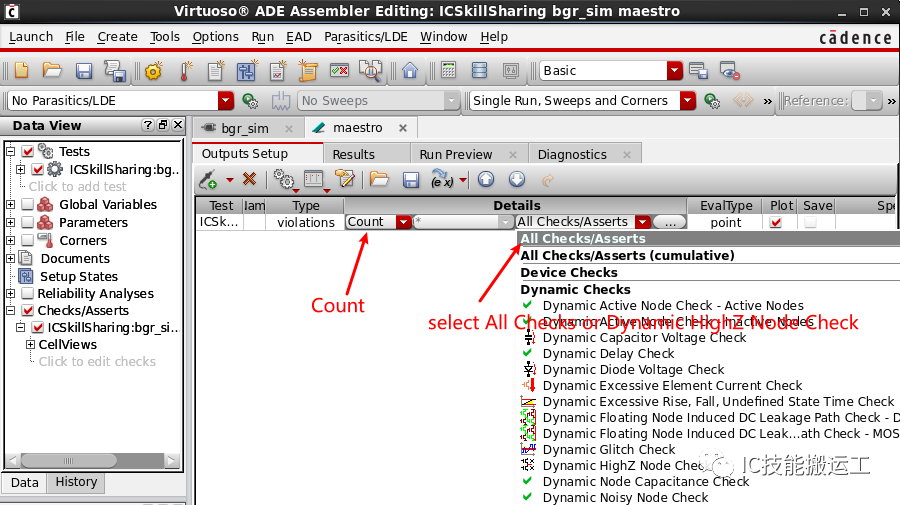

在Fanout一栏,根据检查类型选择gate或者bulk,即指定仿真器检查floating gate或者floating bulk,如果没有特别需要也可以选择all,最后保存设置,并返回最初的ADE Assembler界面。 接下来进行输出信息设置,在Output Setup界面,选择:Add new output->your test name->Violation Filter,添加违例设置。

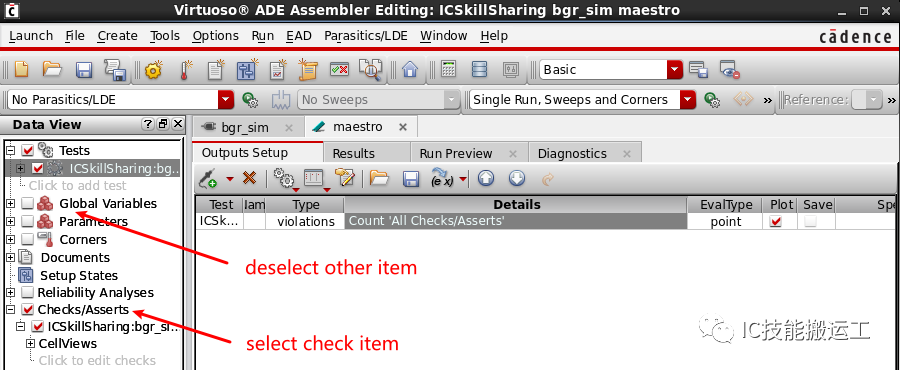

在Details一栏下面双击,会弹出三个可选框,具体内容有兴趣的同学可以查看一下Cadence手册,所有值保持默认即可,也可以根据具体检测内容灵活选择,小目同学的设置如上图所示。 完成上面的设置之后,运行仿真,在运行仿真前记得勾选左侧Checks/Asserts选择框,并将不必要的项目取消选择。

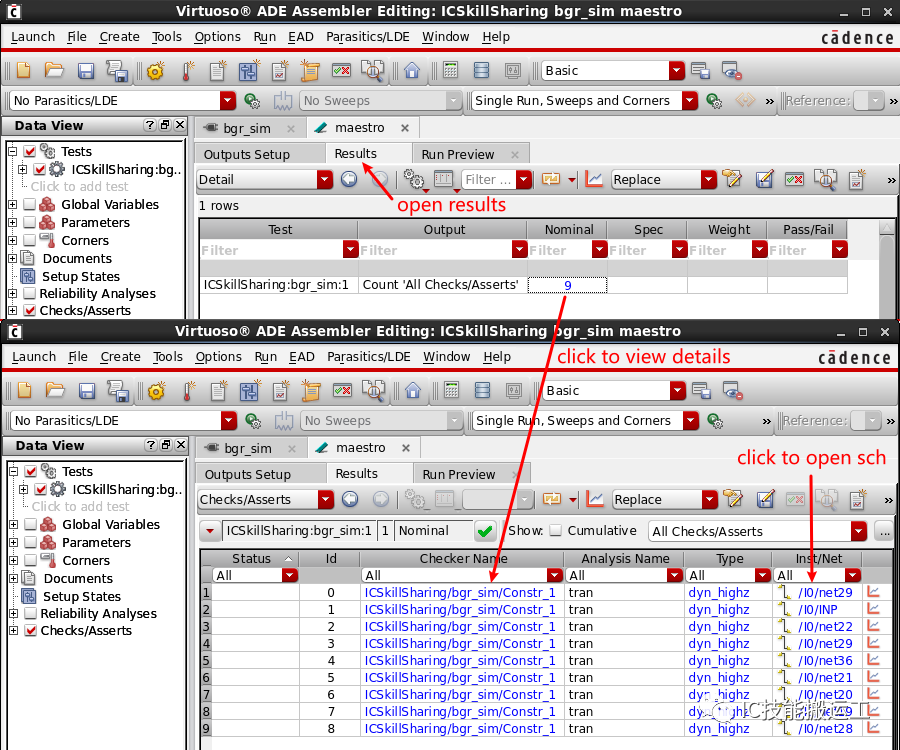

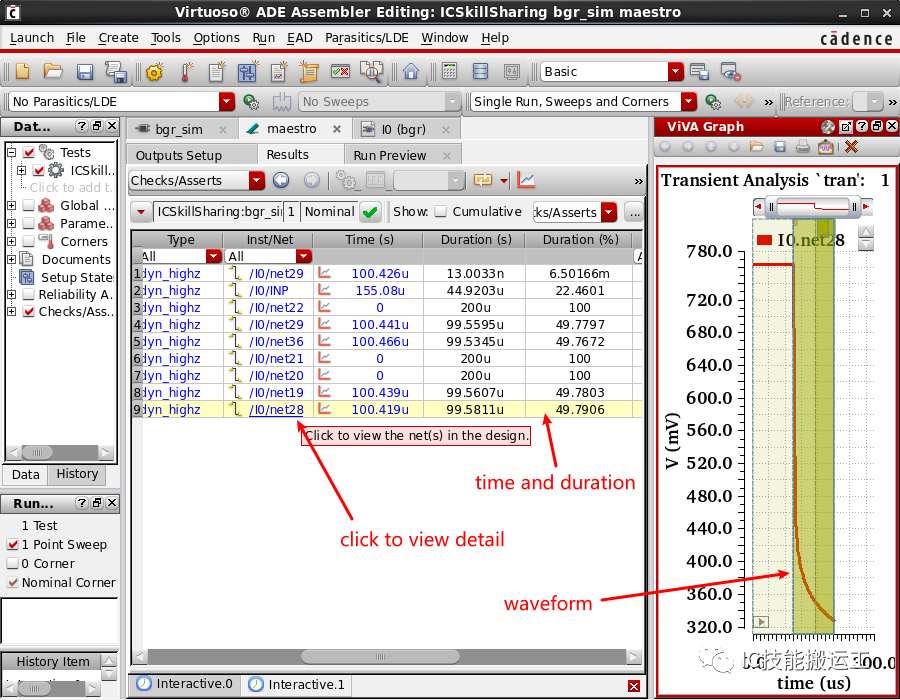

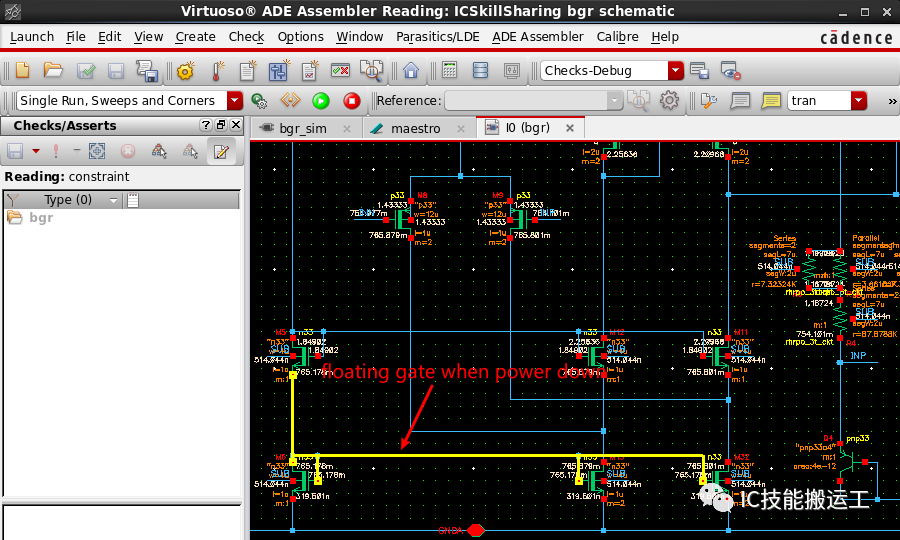

仿真完成之后,通过结果查看器检查电路中存在的违例,查看结果过程中,通过点击链接可以打开原理图直接查看违例情况以及对于的瞬态波形。

在检查设置时,Fanout一项小目同学选择gate,所以上面结果显示:被检查的电路存在9个floating gate的违例,我们可以通过点击查看具体违例产生的时间、对应的节点和电路波形。

根据结果确定电路中相应节点是否存在隐患,根据实际情况对电路进行修改,添加高阻节点放电通路等。

从结果来看,检查中报出的floating gate隐患主要是该电路中未添加gate的power down电路,所以导致电路下电后存在floating gate,该隐患可能导致电路下电后异常漏电。

审核编辑:汤梓红

-

无法为单个数据类型找到Assembler浮点库IEEE 7542018-12-06 0

-

MRS的汇编设置assembler和assembler-with-cpp有啥区别?怎么才能切换呢?2022-06-24 0

-

ADE7169应用电路,参考设计原理图2009-09-03 449

-

ADE7116/ADE7156/ADE7166/ADE7162009-09-11 533

-

ADE7755高精度电能计量电路2009-10-09 829

-

HV Floating MOS-Gate Driver IC2009-12-07 639

-

什么是BAS (Basic Assembler Progra2010-02-22 1210

-

ADE7854_ADE7858_ADE7868_ADE7878 pdf2012-03-13 1352

-

Mixing_C_and_Assembler_With_the_MSP4302016-02-16 332

-

ARMCompiler toolchain v5.02 for_using_the_assembler2017-10-30 653

-

ADS ARM Assembler Guide2017-10-31 752

-

Cadence小技巧:利用lib功能免除新ADE的设置2018-02-18 7745

-

ADE7116/ADE7166/ADE7169/ADE7566/ADE7569:带8052 MCU、RTC和LCD驱动器的单相电能测量IC数据表2021-05-22 481

-

EVALADE788A ADE7854A/ADE7858A/ADE7868A/ADE7878A评估板2021-05-28 459

-

如何利用ADE Assembler检查电路中的floating gate?2023-06-14 1264

全部0条评论

快来发表一下你的评论吧 !