ADC0809 的逻辑结构及引脚定义

描述

- ADC0809 的逻辑结构

ADC0809 是带有 8 位 A/D转换器、 8 路模拟开关以及微处理机兼容的控制逻辑的 CMOS组件。它是逐次逼近式 A/D转换器,是目前应用比较广泛的 A/D转换芯片之一,主要适用于对精度和采样速率要求不高的场合或一般的工业控制领域,可以和单片机直接相连。它具有 8 个通道的模拟量输入线, 可在程序控制下对任意通道进行 A/D转换得到 8位二进制数字量。

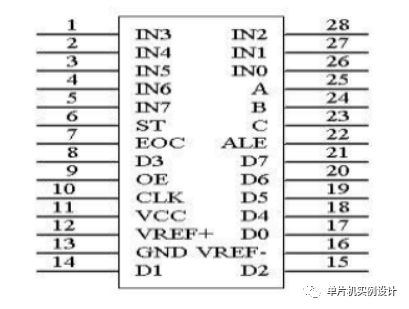

2.ADC0809引脚定义

ADC0809对输入模拟量要求:信号单极性, 电压范围是 0-5V,若信号太小,必须进行放大;输入的模拟量在转换过程中应该保持不变,如若模拟量变化太快,则需在输入前增加采样保持电路,即采集模拟输入电压在某一时刻的瞬时值,并在 A/D 转换期间保持输出电压不变,以供模数转换。

- 模拟信号输入 IN0~IN7(26-28、1-5 脚) :IN0-IN7 为八路模拟电压输入线,加在模拟开关上,通过 A、B、C三个地址译码来选通。

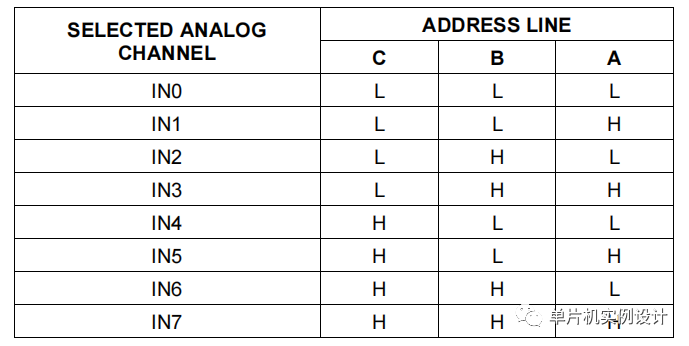

- 地址输入和控制线:地址输入和控制线共 4 条,其中 A、B和 C为地址输入线(23-25 脚),用于选择 IN0-IN7 上哪一路模拟电压送给比较器进行 A/D 转换。ALE(22脚)为地址锁存允许输入线,高电平有效。当 ALE线为高电平时,A、B和 C三条地址线上地址信号得以锁存,经译码器控制八路模拟开关通路工作,上升沿有效。通道选择表如下表所示。

3.数字量输出及控制线共 11 条:

- START(6脚) 为“启动脉冲”输入线, 上升沿清零,下降沿启动 ADC0809工作,最小脉冲宽度与 ALE信号相同。

- EOC(7脚) 为转换结束输出线, 该线高电平表示 A/D 转换已结束,数字量已锁入“三态输出锁存器” ,常用来作为中断请求信号。

- OE为“输出允许”线, 高电平有效。ADC0809接到此信号时,其三态输出端与 CPU数据总线接通,后者可将数据取走。

- D0-D7(17、14、15、18-20 脚)为数字量输出线, D7为最高位, D0为最低位。

4.电源线及其它共 5 条:CLOCK(10 脚)为时钟输入线,用于为 ADC0809

提供逐次比较所需,一般为 640kHz时钟脉冲。

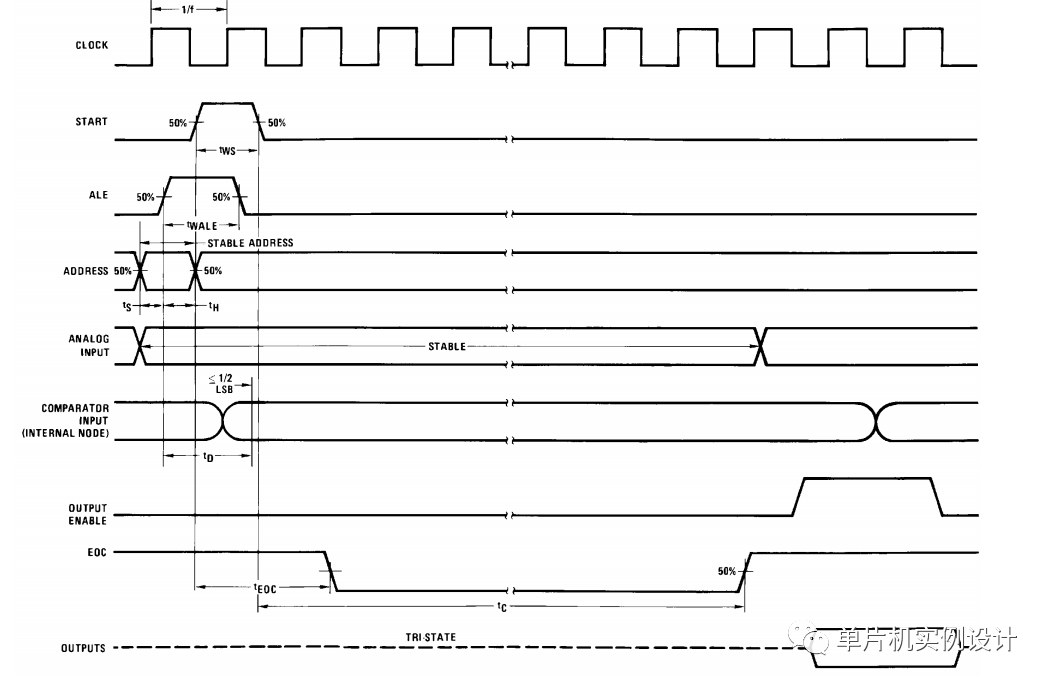

3.ADC0809控制时序

adc0809控制时序如图,adc0809驱动程序是基于以下时序图来编程;

ADC0809驱动程序:

(1)adc0809.h

#ifndef __0809_H__

#define __0809_H__

#include < reg52.h >

#define uint unsigned int

#define uchar unsigned char

extern uint num;

sbit OE = P1^0;

sbit EOC = P1^1;

sbit ST = P1^2;

sbit CLK = P1^3;

sbit dat = P3;

void Red_0809 ();

#endif

(2)adc0809.c

#include "0809.h"

void Red_0809 ()

{

ST = 0;

ST = 1;

ST = 0;

while(EOC == 0);

OE = 1;

num = dat;

OE = 0;

}

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADC0808_ADC0809英文资料ADC0809引脚图封装应用电路图2016-09-23 5060

-

A/D转换器芯片ADC0809的内部结构和信号引脚2018-07-19 0

-

ADC0809AD转换器应用技术资料推荐2021-04-15 0

-

怎样去使用ADC08092021-11-17 0

-

ADC0809是什么?ADC0809是如何工作的2022-01-25 0

-

adc0809芯片管脚图引脚图及内部功能图2007-12-19 8288

-

ADC0809接口电路2009-01-14 4607

-

adc0809是什么2011-05-25 3318

-

adc0809引脚图及功能详解,adc0809与51单片机连接电路分析2016-09-13 90862

-

adc0809中文资料下载 adc0809引脚图封装及应用电路2016-09-23 20058

-

ADC0809用法详解_引脚图及功能_工作原理_内部结构及应用电路2017-12-13 183444

-

模数转换器ADC0809引脚及内部框图_ADC0809数模转换与显示程序设计2018-01-05 25029

-

adc0809引脚图及功能2021-07-07 11809

-

ADC0809的使用2021-11-10 1508

-

ADC0809资料2022-06-28 591

全部0条评论

快来发表一下你的评论吧 !