数字芯片设计流程

EDA/IC设计

描述

芯片设计分为前端设计和后端设计,前端设计也称为逻辑设计,后端设计也称为物理设计。随着DFT技术的发展,有的公司将DFT归到前端设计,有的公司归到后端设计,有些情况下也将DFT归到中端设计。前后端并没有统一严格的界限,笔者愚见,个人认为涉及到工艺相关的设计就是后端设计。

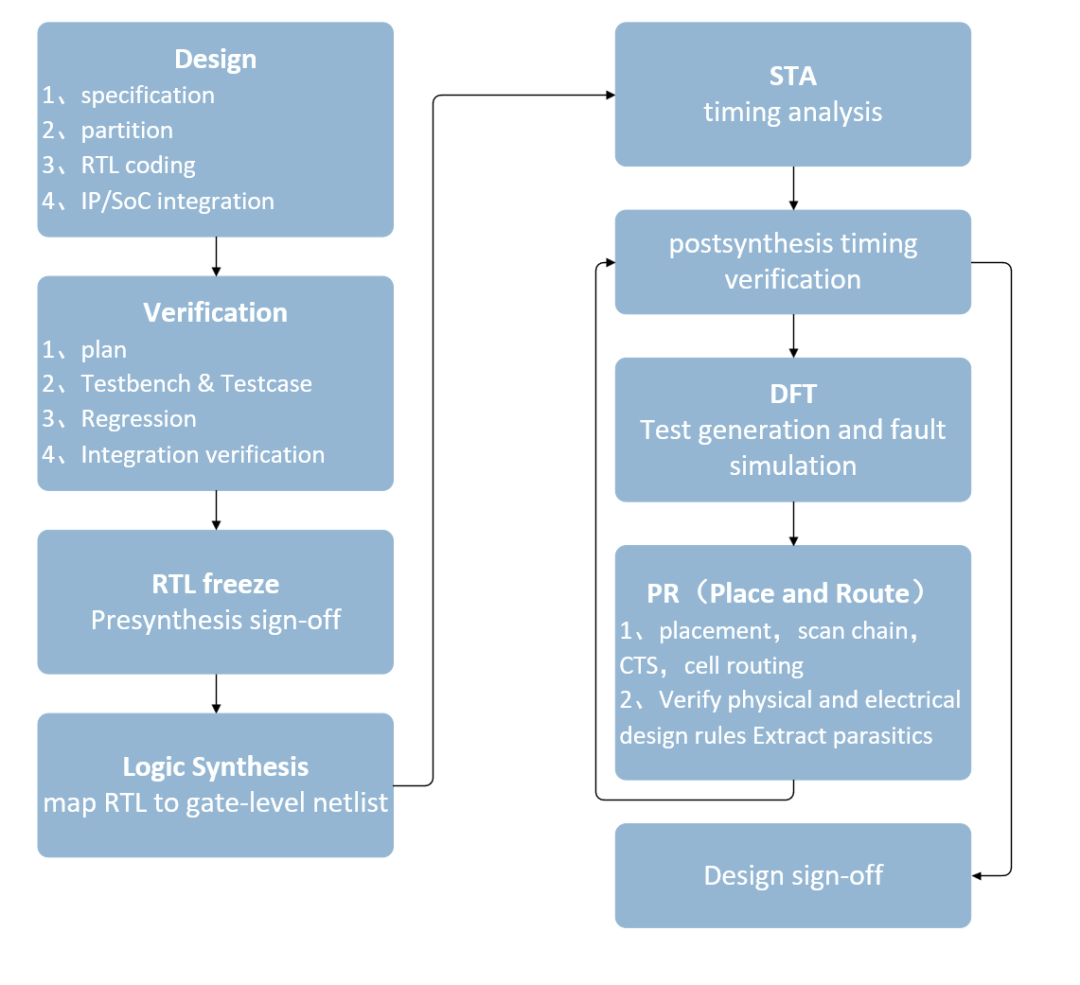

下图为数字IC设计的流程简图:

01前端设计部分

1、需求分析

产品要解决什么问题,预测未来3-5年的趋势和走向,确保芯片是有卖点和前瞻性的,面向未来。而后客户向Fabless公司提出设计要求,包括芯片功能和性能需求,让架构师可以细化。

2、架构设计

架构师将系统功能进行分解细化,形成Spec规范,将设计参数化、具体化。包括:

- 处理器架构的选择:ARM、RISC-V等;

- 总线接口的选择:AHB、AXI、APB等;

- 软硬件功能的划分:硬件速度快、性能高,但灵活性较差;软件速度慢、性能低,但灵活性好、开发周期短。

- 性能参数:引脚分配、电压频率、工艺选择、功耗和温度范围

3、RTL Coding

使用硬件描述语言将模块功能以代码的形式实现或者用图形输入工具来实现电路(Cadence的composer)

4、功能仿真验证(前仿真)

功能仿真:对RTL及的代码进行设计验证,检验设计功能的正确性,看是否满足Spec中的所有需求。

仿真工具有Modelsim、VCS等。

5、逻辑综合(Synthesis)

基于特定的工艺库,设计电路的面积、时序等目标参数的约束条件,将设计的RTL级代码映射为门级网表(netlist)。逻辑综合需要基于特定的综合库,对于不同的库,门电路标准单元的面积、时序等参数是不一样的。

逻辑综合工具有Synopsys的Design Compiler

6、静态时序分析(STA,Static Timing Analysis)

在时序上对电路进行验证,检查电路是否存在建立时间(Setup time)和保持时间(Hold time)的违例(violation)。

STA工具有Synopsys的Prime Time。

7、形式验证(Formality)

从功能上对综合后的网表进行验证,将综合后的网表与验证后的HDL设计进行对比,看两者在功能上是否等价,保证逻辑综合过程中没有改变HDL描述的电路功能。

形式验证工具有Synopsys的Formality

02DFT(中端)

可测性设计(DFT,Design For Test)是IC设计中的重要一步。通常对于逻辑电路采用扫描链(Scan Chain)的可测试结构,增加电路内部结构的可控性和可观测性。一般在逻辑综合或物理综合后进行扫描电路的插入和优化。此外还有MBIST、ATPG等技术。DFT相关内容会在同专栏文章《可测性设计》中详细介绍。

03后端

1、布局规划(Placement)

放置芯片中的宏单元模块,在总体上确认各种功能电路的摆放位置,如IP、RAM、I/O引脚等模块的位置,能影响芯片的最终面积。现在的EDA工具广泛支持物理综合,将布局优化和逻辑综合统一起来,引入真实的连线信息,减少了时序收敛需要的迭代次数。

工具有IC Compiler

2、时钟树综合(CTS,clock tree synthesis)

构造芯片内部全局或局部平衡的时钟链的过程称为时钟树综合,目的是使时钟从同一个时钟源到达各个寄存器时,延时差异最小。

3、布线(Route)

将前端提供的网表实现成版图,包括各种标准单元之间的走线。布线工具通常将布线分为两个阶段:全局布线和详细布线。在布局之后,通过全局布线决定布局的质量以及提供大致的延时信息。得到的时序信息被反标(Back Annotation)到设计网表上,用于STA,只有时序满足了才会进行详细布线,详细布线完成后可以得到精确的时序信息。

4、寄生参数提取(Parasitic Extraction)

由于导线本身存在的电阻,相邻导线之间的互感、耦合电容在芯片内部会产生信号噪声、串扰和反射。提取寄生参数进行再次分析验证,分析信号完整性问题。

5、后仿真(Post-layout Simulation)

后仿真也叫门级仿真、时序仿真、带反标的仿真,需要利用在布局布线后获得的精确延迟参数和网表进行仿真,验证网表的功能和时序是否正确。后仿真一般使用标准延时(SDF,Standard Delay Format)文件来输入延时信息。

6、物理版图验证

对布线完成的版图进行功能和时序上的验证:

- LVS:版图和逻辑综合后的门级电路图进行对比验证

- DRC:设计规则检查,检查连线间距、连线宽度

- ERC:电气规则检查,检查短路开路

完成以上设计之后就可以Sign-off、交付到芯片代工厂(Foundry)Tape out了。实际上的后端流程还包括电路功耗分析。物理版图以GDS II 的文件格式交给芯片代工厂在晶圆硅片上做出实际的电路,再进行封装和测试,最后得到芯片。

在实际的IC设计中,不同的EDA厂商通常会结合自己的EDA工具特点提供设计流程,但大体上都是一致的。随着工艺尺寸的不断减小,新的设计流程也将随着新的EDA工具而出现,用于解决新的问题。

-

数字芯片设计流程2020-02-12 0

-

数字IC的设计流程有哪些2021-10-20 0

-

数字芯片的设计流程思路和技术说明2020-06-09 870

-

数字IC设计流程2020-12-09 6540

-

数字集成电路芯片的设计流程详解2021-06-06 20485

-

Cadence推出创新产品 颠覆未来芯片的设计工具2021-09-02 4608

-

数字芯片设计流程之verilog设计2021-11-05 513

-

数字IC设计之“数字SOC全流程漫谈从0到1”2021-11-05 663

-

新思科技DesignDash解决方案推进数字芯片设计流程2022-06-23 957

-

数字芯片验证流程2022-07-25 5427

-

数字芯片设计流程分析之模拟IC2023-03-01 1852

-

数字芯片的原理 数字芯片的设计流程2023-06-02 2392

-

EDA硬核科普|异构验证:整合三大数字芯片验证工具,显著缩短芯片开发周期2023-04-25 890

全部0条评论

快来发表一下你的评论吧 !