Mojo v3 FPGA板与16x2 LCD模块是如何进行连接的呢?

可编程逻辑

描述

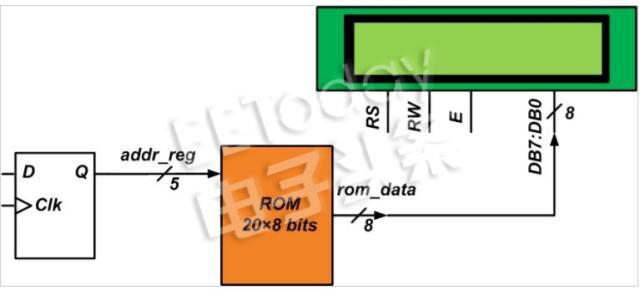

在本教程中,我们将使用Verilog HDL设计一个数字电路,该电路与基于HD44780 LCD控制器/驱动芯片的通用LCD模块连接。Mojo V3 FPGA板将用于实现设计。本文中使用的LCD模块是1602A显示器。

HD44780兼容LCD模块

之前我们讨论了使用HD44780 LCD控制器/驱动芯片的LCD模块的详细信息。这些LCD模块的引脚排列如图1所示。

图1.图片由AAC提供

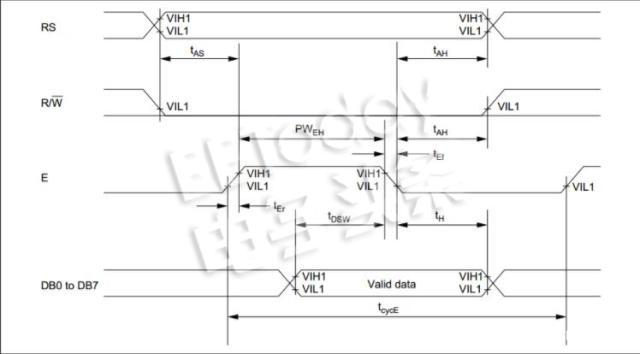

如你所见,有三个控制引脚(RS、R / W和E)以及八个数据引脚(DB7至DB0)。对于写操作,我们需要对这些引脚施加适当的电压,如下面图2的时序图所示。

图2.图片由HITACHI提供

上述时序图的不同延迟值如下表所示:

表1.由HITACHI提供

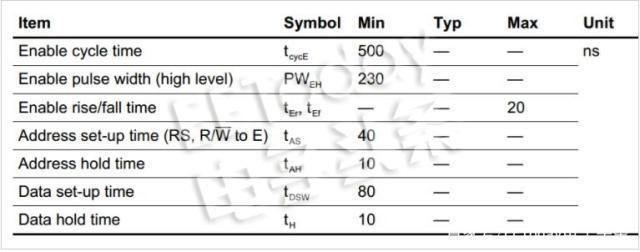

有几条指令可用于配置LCD模块。下面列出了一些重要说明。

表2

表2

路径1

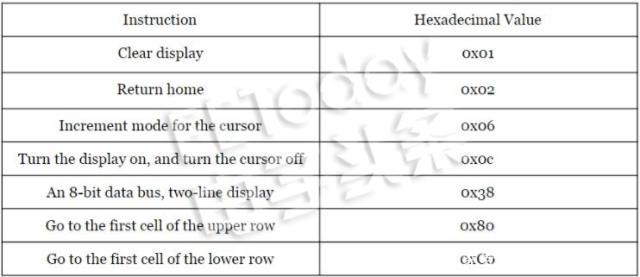

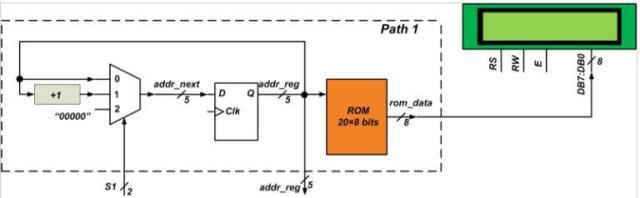

我们想在液晶显示屏上显示“HELLO WORLD!”信息。让我们来看看数字系统需要与LCD模块通信的构建模块。我们需要一个ROM来存储消息字符的ASCII码。如图3所示,ROM的输出将连接到LCD模块的8个数据引脚。

图3

图3

“HELLO WORLD!”消息有12个字符,我们可以使用128位ROM来存储消息。但是,让我们考虑为消息提供一个168位的ROM,这样我们就可以显示长达16个字符的消息(LCD第一行的长度)。如果我们的消息最长为16个字符,你可能想知道为什么上图显示的是一个208位ROM。这些额外的四个字节将用于存储与允许我们配置模块相关的LCD指令相关的数据。例如,如表2中所列,我们可以将十六进制值0x38应用于LCD数据引脚,以指定LCD模块应以8位长度接收/发数据。就像字符代码一样,命令的十六进制值应用于数据引脚,因此,我们可以将这两个命令存储在同一个ROM中。

在本文中,我们将使用四个命令(0x38、0x06、0x0C和0x01)来配置LCD。你可以在表2中找到这些命令的简要说明。因此,我们有一个208位ROM,其中前四个字节是0x38、0x06、0x0C和0x01。接下来的16个字节存储消息的ASCII码。考虑到图2的时序图,我们观察到应用于DB7-DB0的数据在一定时间内不应发生变化,以便LCD能够成功读取数据。因此,如图3所示,我们需要一组D型触发器(DFF)来保持ROM地址(DB7-DB0)在一段时间内保持恒定。LCD读取数据后,我们需要将地址值增加1,将下一个字符/命令应用到LCD。因此,如图4所示,应在DFF之前放置多路复用器和增量器。

图4

使用多路复用器的选择输入,我们可以指定地址值应该保持不变(S1=0)还是增加(S1=1)。多路复用器有第三个选项,允许我们将地址值重置为00000。这也可以通过重置DFF来实现。我们将所有这些块称为路径1,如图所示。正如本文后面所讨论的,我们将使用S 1 信号来控制路径1 块内的电路。该地址寄存器信号将被用来监视路径1的状态。值得一提的是,虽然上图只显示了一个DFF,但实际上有五个DFF(因为20字节ROM需要一个5位地址总线)。

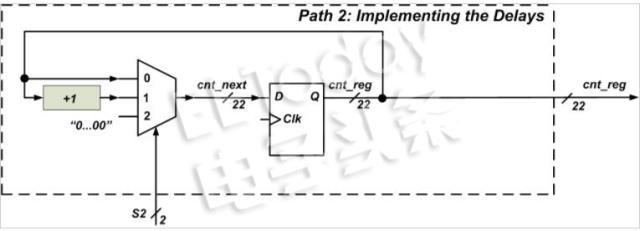

实现延迟

如上所述,应用于LCD控制输入的波形应遵循图2的时序图。在RW和RS引脚改变状态后,我们必须等待t AS,然后再将E引脚设置为逻辑高电平。然后,E上的从高到低的转换开始写操作。但是,在E的下降沿之前(t DSW)和之后(t H)的一段时间内,数据应该保持不变。因此,为了成功地与LCD通信,我们必须实现延迟TAS、T DSW和t h。这可以通过计数器实现。由于我们有时需要暂停计数器或重置它,我们将在计数器的DFF之前放置一个多路复用器。如下图5所示。

图5

通过这种方式,我们可以使用S2输入来控制计数器,而cnt_reg输出将给出计数器的状态,这表示经过的时间。根据时序图,我们需要三个不同的时间延迟:tAS=40ns,tDSW=80ns,tH=10ns。注意到Mojo V3板的时钟频率为50 MHz(时钟周期为20 ns),我们可以计算每个时间延迟所需的计数。

然而,事实证明我的16x2 LCD需要更长的延迟才能运行。这可能是因为我使用相对较长的电线和面包板来测试我的设计。在本文中,我将实现tAS=10ms和tH=3 ms。我会将E信号保持高电平58ms(PWEH=58 ms)。我的设计应该可以使用更短的延迟。你可以进行一些实验并根据你的设计调整这些数字。计数器需要多少位?选择延迟后,总延迟将为10+58+3ms=71 ms。考虑到Mojo的时钟周期(20 ns),从0到3549999可以实现71 ms的延迟。因此,如图5所示,我们需要一个22位计数器。

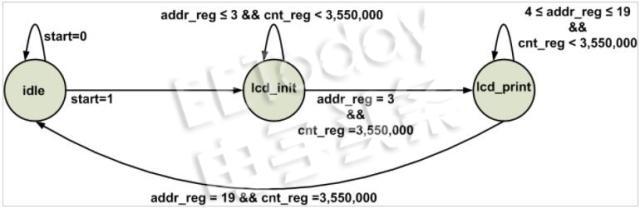

控制路径

我们需要的最后一个构建块是一个 适当控制路径1和路径2块的单元,以便为LCD模块生成所需的波形。这可以通过有限状态机(FSM)实现,它可以接收addr_reg和cnt_reg信号(路径1和路径2的状态)并生成适当的s1和s2信号。该FSM的初始设计如图6所示。

图6

请注意,该图仅显示状态转换(未显示FSM的输出)。有三种状态:在空闲 状态期间,信号获得其初始值。所述lcd_init状态应用于液晶配置命令;这就是状态转换条件为addr_reg = 3 && cnt_reg = 3550000的原因。换句话说,我们有四个命令,并且当所述第四命令(addr_reg = 3)被施加到LCD 71毫秒(cnt_reg = 3550000)时,我们应该将消息数据发送到LCD lcd_print状态。当我们到达ROM的末尾(addr_reg = 19)时,我们应该等待71 ms(cnt_reg = 3550000),然后转换到空闲状态。项目的困难部分几乎完成了。现在,我们只需要设计FSM并编写其Verilog代码。

结论

对于FPGA,我们通常必须在设计的最低层次上查看问题。我们所拥有的是逻辑门和一些基本构建模块,如加法器和比较器。虽然这使FPGA设计变得困难,但FPGA确实提供了几个优点。在本文中,我们研究了将FPGA与通用16x2 LCD模块连接的构建模块。需要ROM、一些DFF和多路复用器来实现FPGA到LCD接口。此外,我们需要一个FSM来控制这些构建块。

-

使用16x2 LCD键盘屏蔽的按钮2022-11-09 202

-

连接一个16x2字符LCD2022-11-17 286

-

在树莓派上装LCD 16x2显示屏2016-01-15 0

-

16x2 LCD PIONEER套件屏蔽2019-01-16 0

-

请问是否有人在Spartan 3a开发板上看到或写过任何verilog写入16x2 LCD?2019-06-28 0

-

串行显示LCD 16x2监视器2022-08-19 0

-

NodeMCU 16X2 LCD代码问题如何解决?2023-06-09 0

-

VU表lcd 16x2开源分享2022-07-20 310

-

将16x2 LCD与ARM7-LPC2148连接并显示文字2022-10-28 1507

-

如何将16x2 LCD与Atmega16 AVR连接并显示简单的欢迎消息2022-11-11 2730

-

如何连接和使用16x2 I2C LCD的教程2022-11-22 273

-

Casil LED背光16x2 LCD显示模块项目2022-12-01 214

-

在Arduino上使用16x2 LCD2022-12-12 347

-

如何将16x2 LCD与Raspberry pi4连接2023-06-19 240

-

如何连接16x2 LCD显示器2023-07-12 237

全部0条评论

快来发表一下你的评论吧 !