模拟IC入门:MOS器件物理基础知识

模拟技术

描述

在学习MOS特性前,需要对器件物理中的一些基础特性进行了解:

扩散运动 :由热运动引起的随机运动,一般由高浓度向低浓度转移,直到均匀分布。

漂移运动 :电场作用下载流子的单向运动。

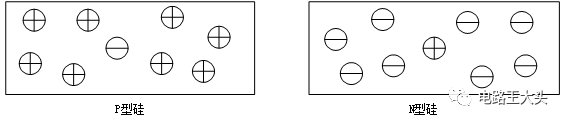

PN结概念(以硅载体为例):

- P型硅中多子为空穴,少子为电子;N型硅中多子为电子,少子为空穴;

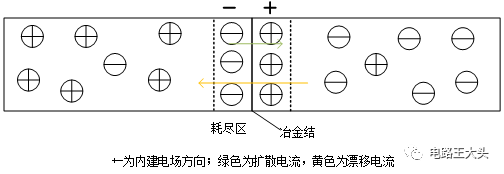

- P型硅和N型硅相互接触形成一个结,由扩散运动(P型硅中的空穴转移到N型硅中,这部分空穴对于N型硅而言是过量少子;同理N型硅中的电子转移到P型硅中,这部分电子对于P型硅而言是过量少子)导致的过量少子会形成一个电势差,并产生电场。

- 由于电场的存在,载流子会发生漂移运动,P型硅中的空穴被吸引到电位为负的P结处,N型硅中的电子被吸引到电位为正的N结处。这样,当漂移电流和扩散电流大小相等,方向相反时就建立了平衡的PN结。此时的PN结电压称为内建电势差,或接触电压。

- 由于内在电场,进入该区域的载流子必然会加速通过,所以该区域内电子和空穴都很稀少,又称耗尽层、势垒区、空间电荷区、阻挡层。

MOS简介

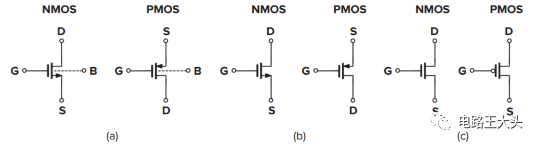

1、常见MOS符号

区分PMOS和NMOS:小箭头方向表示电流方向(也是PN结方向),PMOS是电流流进器件,NMOS是电流流出器件。

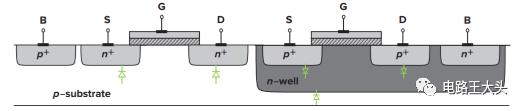

2、常见MOS剖面结构

上图是NMOS(左)和PMOS(右)的剖面结构,低压的MOS一般是一个四端器件,常规的CMOS工艺都是制作在P-substrate上,且器件是对称的,源漏可以互换。(隔离管和中高压管结构特殊,之后会做介绍)

对于上图可以看出衬底B的电位对器件特性有很大影响,正常使用时,必须保证源/漏结的二极管反偏,所以NMOS的衬底必须接低电位,PMOS的衬底B必须接高电位,否则都会有对衬底的漏电。

Q&A:为什么CMOS工艺中的基底大多都是P型,而不是N型?

- 设计角度:(设计简单)

在N沟道中参与导电的是电子,而在P沟道中参与导电的是空穴,在单位电场强度下电子的迁移率远远大于空穴的迁移率,即N沟道的导电性能要比P沟道的导电性能好。因此N沟道场效应管的导通速度或工作频率要远远高于P沟道场效应管。

另外如果基底是P型,为保证源/漏结反偏,P-sub只用接到GND就可以,而如果基底是N型,N-sub必须接到系统的最高电位,而在SOC中常会用到不同的源,1.8V、3.3V、5V等,无法保证某些情况下最高的源被使用到,会比较麻烦。

- 工艺角度:(成本便宜)

P型半导体是在单晶硅(或锗)中参入微量的三价元素,如:硼、铟、镓或铝等;N型半导体是在单晶硅(或锗)中参入微量的五价元素,如:磷、锑、砷等。P型半导体与N型半导体,在材料成本方面应该差别不是很大,但要把它做成一个电子产品,在生产工艺方面会存在很大的差异。

例如,用本征锗材料制作PNP晶体管相对于用本征锗材料制作NPN晶体管容易很多,因为铟与锗比较容易结合(扩散);同样,用本征硅材料制作NPN晶体管,相对于用本征硅材料制作PNP管要容易很多。

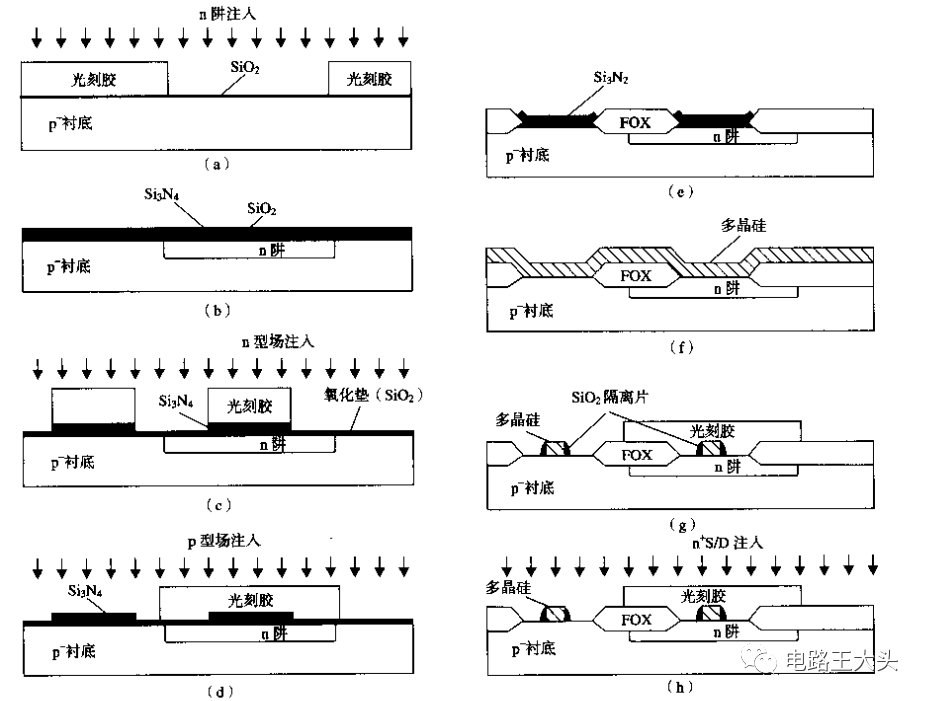

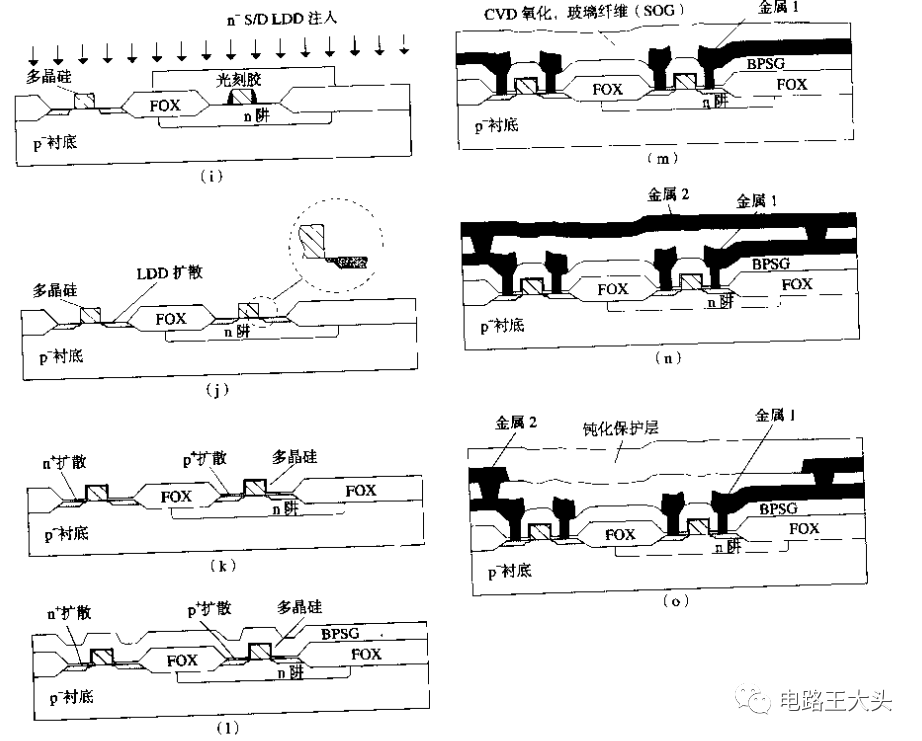

MOS工艺制程

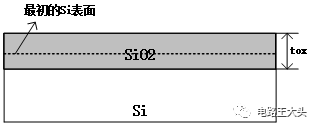

1)氧化

在硅晶圆的表面氧化生长一层SiO2 ;氧化物的厚度用tox表示; SiO2是绝缘层,起隔离保护作用;SiO2有56%生长在表面,44%生长在表面之下;

2)扩散

一种杂质原子由材料表面向材料内部运动的过程。一般在指定区域内扩散,以达到改变材料导电类型和电学性质的目的。

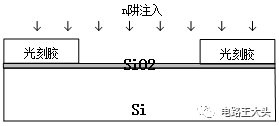

3)离子注入

是特殊掺杂物的离子由电场加速至很高的速度并注入半导体材料中的工艺。与扩散一样,目的都是让杂质掺进半导体材料内。

注入后去除光刻胶再高温氧化和扩散,使注入离子进入P-sub形成n阱。

4)光刻

光刻的基本单元是光刻胶材料和光掩模;光刻胶材料分为正性和负性两种,正性光刻胶紫外光无法穿透,用来制作有图形存在区域的掩模版,紫外线下曝光的区域会被去除;负性光刻胶紫外光可以穿透,用来制作无图形存在区域的掩模版,紫外线下未曝光的区域会被去除;

5)沉积

可以在硅片上生长各种导电薄膜层、半导体薄膜和绝缘薄膜层。

6)刻蚀

刻蚀是出去被暴露材料(未保护)的工艺。刻蚀存在不完整性,会在侧边有侧凹效应。

-

PLC入门必看基础知识2021-09-09 0

-

模拟电路基础知识教程2009-12-04 0

-

模拟电路入门基础知识2019-06-06 0

-

HIFI耳机基础知识入门2010-02-02 2971

-

MOS器件物理基础2011-11-25 611

-

ADC入门_基础知识2016-03-11 974

-

模拟电子基础知识复习2016-09-20 1069

-

什么是DCS系统?DCS系统基础知识入门2018-12-02 43611

-

光无源器件基础知识2021-06-08 752

-

MOS管的基础知识2022-07-22 1734

-

关于mos管的基础知识2023-01-29 3834

-

MOS管的基础知识介绍2023-05-18 2086

-

关于MOS管的基础知识2023-05-23 1014

-

MOS管基础知识:轻松理解MOS管工作原理2023-06-13 786

-

电子元器件的基础知识2023-12-04 2941

全部0条评论

快来发表一下你的评论吧 !