CMOS模拟集成电路-比较器设计

电子说

描述

一.开环比较器

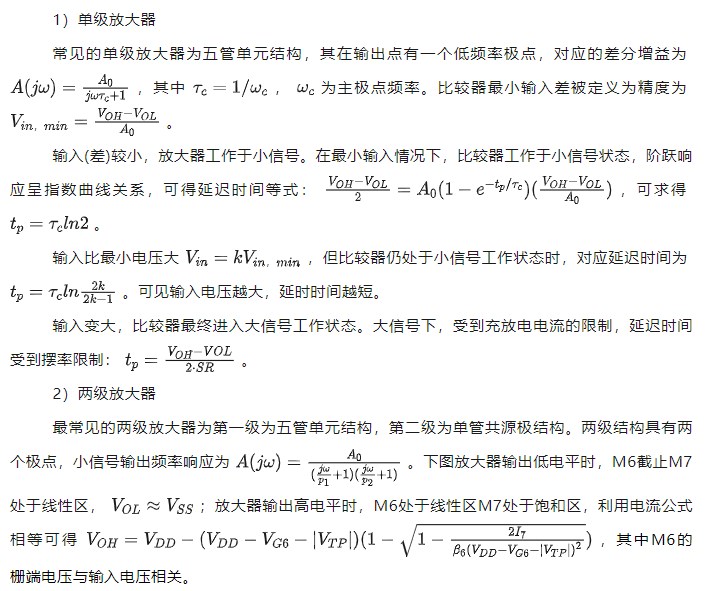

开环比较器基于未补偿的放大器,可以使用单级或者多级结构。根据输入信号的大小,开环放大器工作于小信号状态和大信号状态(摆率限制),其对应的延迟时间计算也是不同。

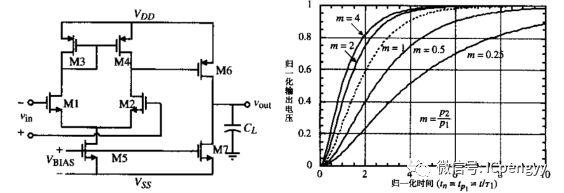

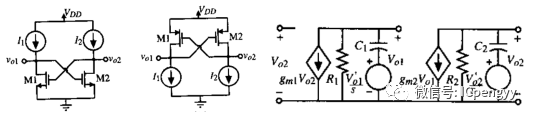

输出级改为ClassAB结构,提供大的充放电电流能力。常见的结构如上,左边称作推挽输出结构,其实业就是对称式OTA。最简单的ClassAB输出级结构为反向器,因此也可以在输出级后级联反向器实现对负载电容的大电流驱动能力。

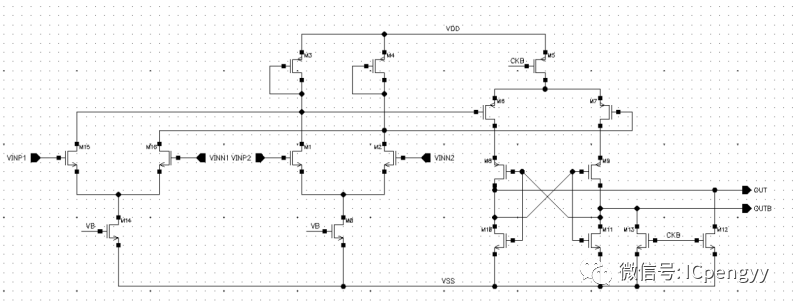

二.再生比较器

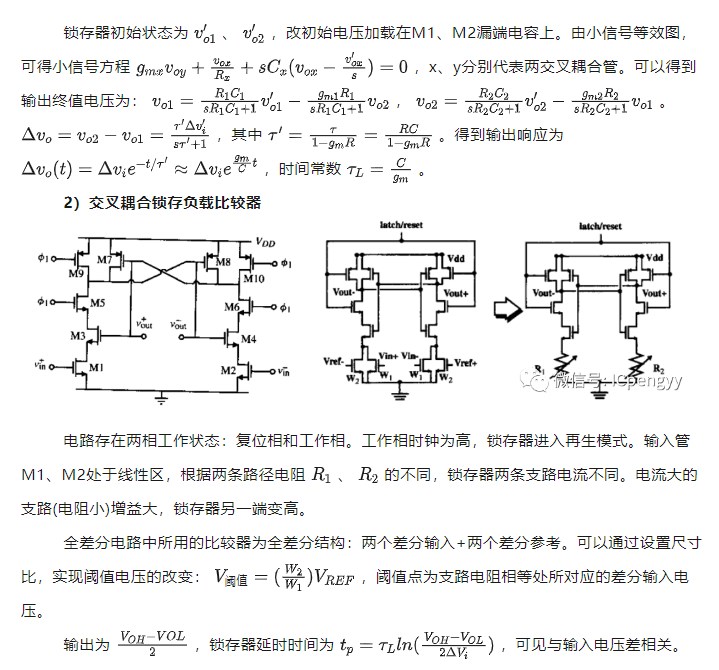

再生比较器利用交叉耦合的MOS管组成的锁存器,通过正反馈实现两信号的比较。

1)交叉耦合锁存器

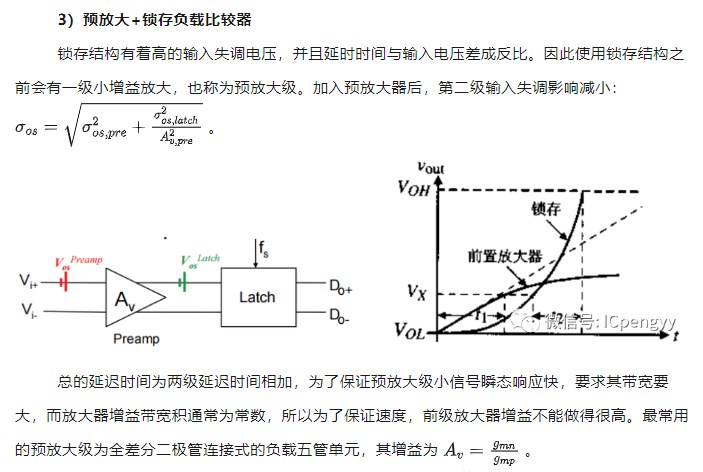

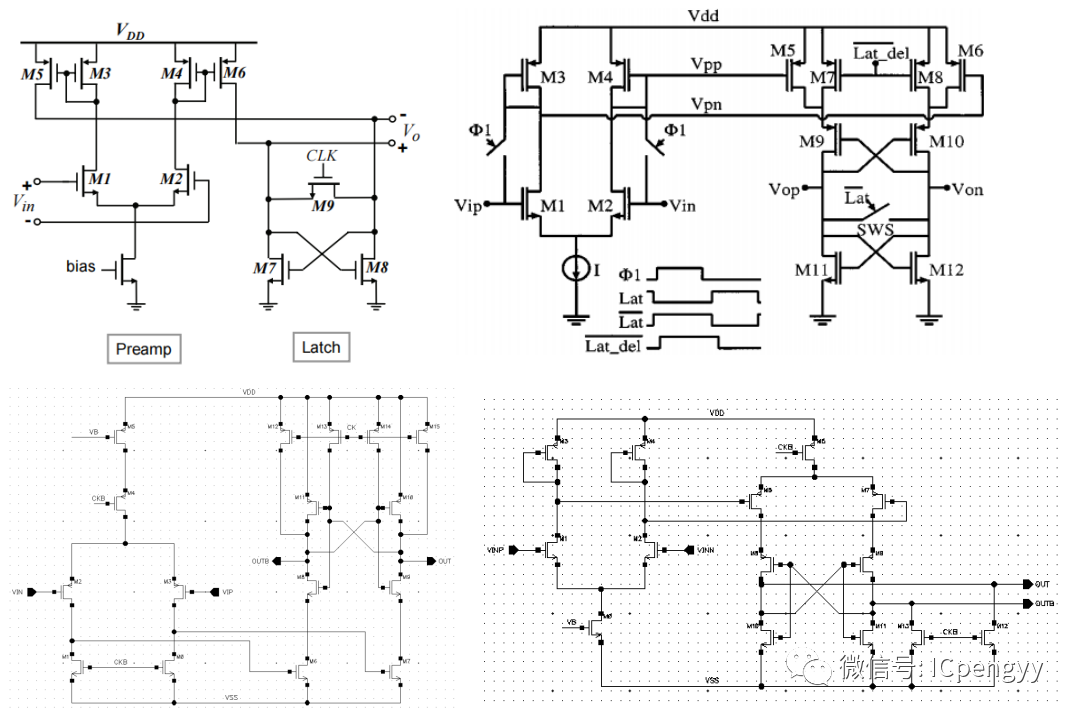

三.比较器输入失调仿真

对于开环比较器,其为差分输入单端输出结构,电路本身就是不对称的,本身存在系统性失调。而对于再生比较器,其结构为全差分结构,电路本身是对称的,其只有随机性失调。

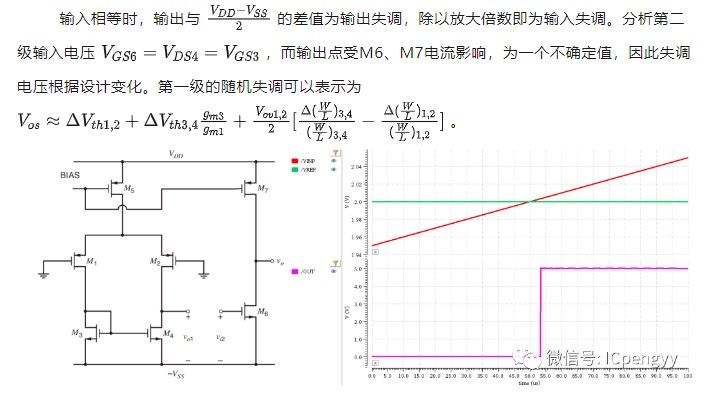

1)两级放大器系统性失调

2)开环比较器失调仿真

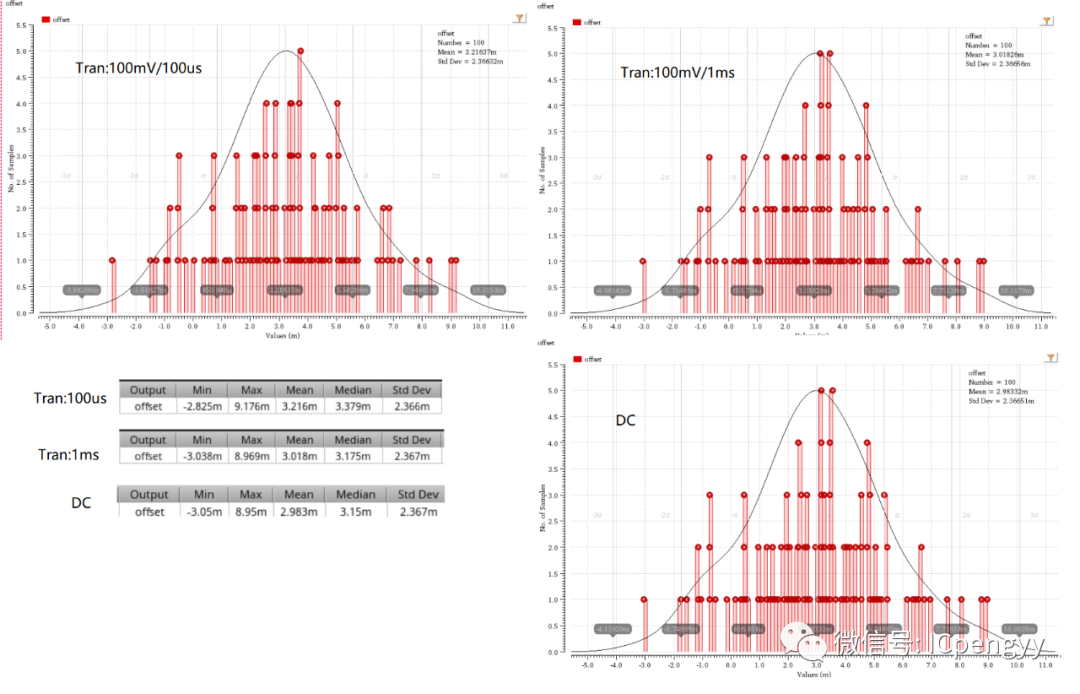

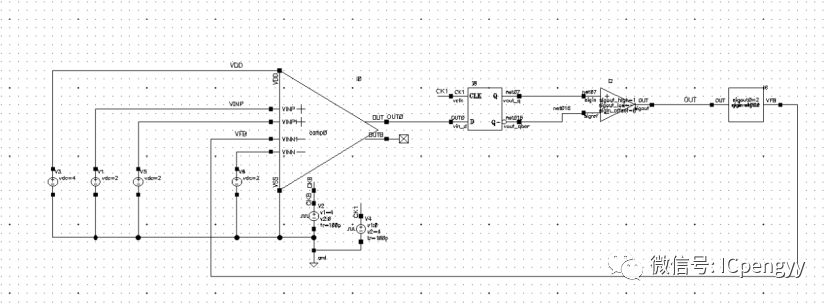

开环放大器仿真失调的方法比较简单,可以采用扫DC的方式或Tran仿真中给正输入端加入斜率很小的斜坡。

DC仿真和Tran仿真可以仿真出系统失调引起的输入失调电压、此外如果Tran仿真会引入比较器延时误差,因此斜率较小的要求是必须的。

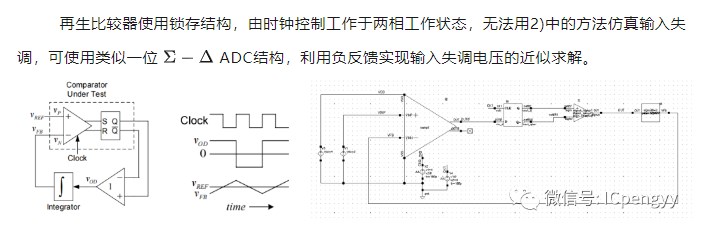

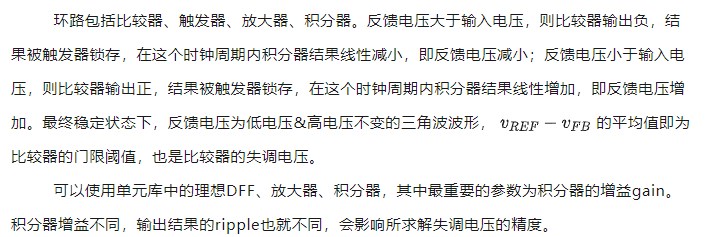

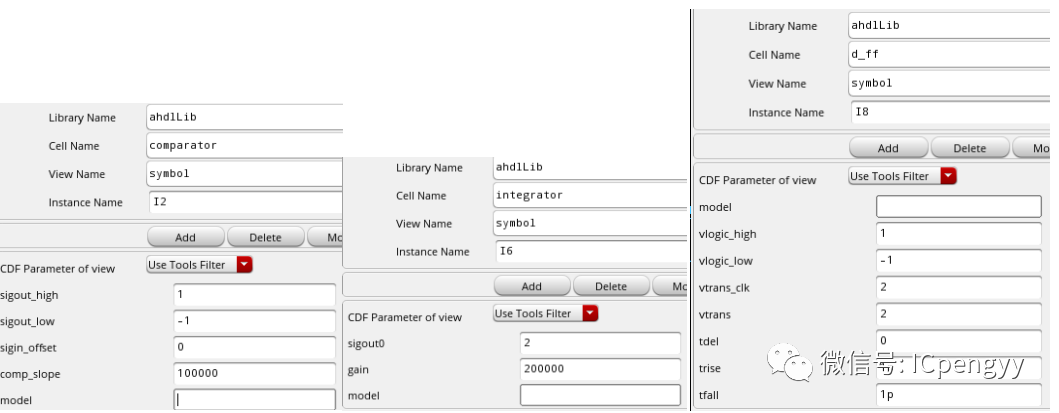

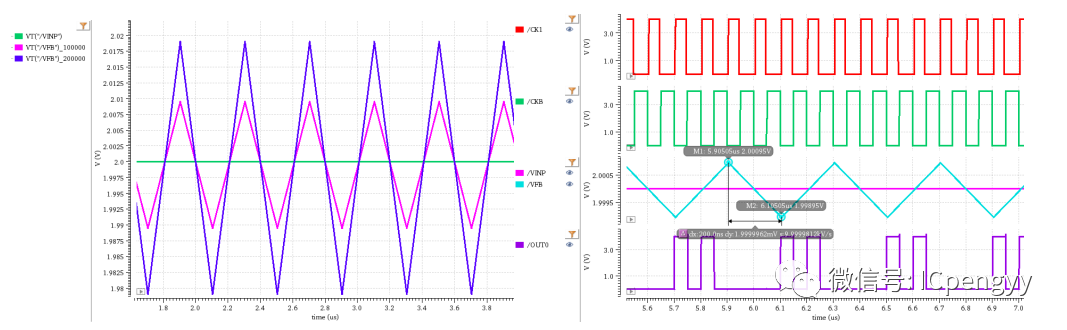

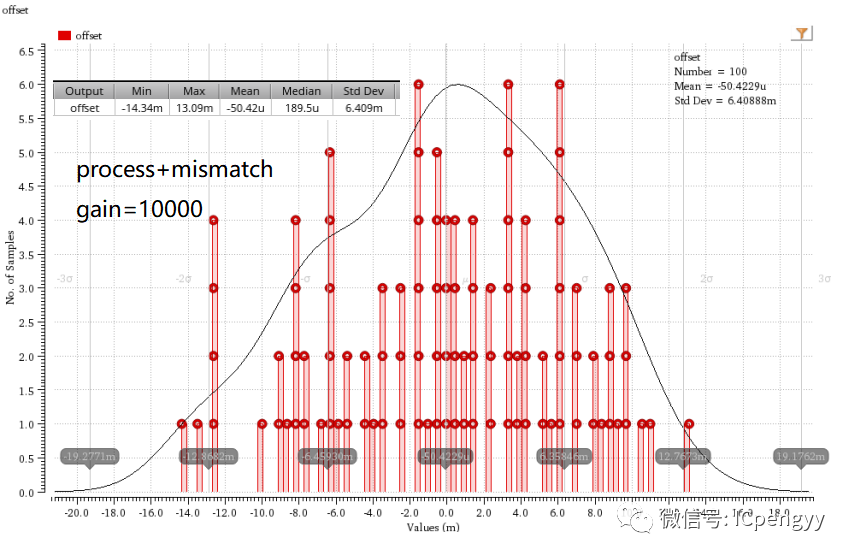

3)再生比较器失调仿真

DFF的时钟与比较器的工作时钟也要合理设置,保证比较器比较相结束前DFF完成采样。

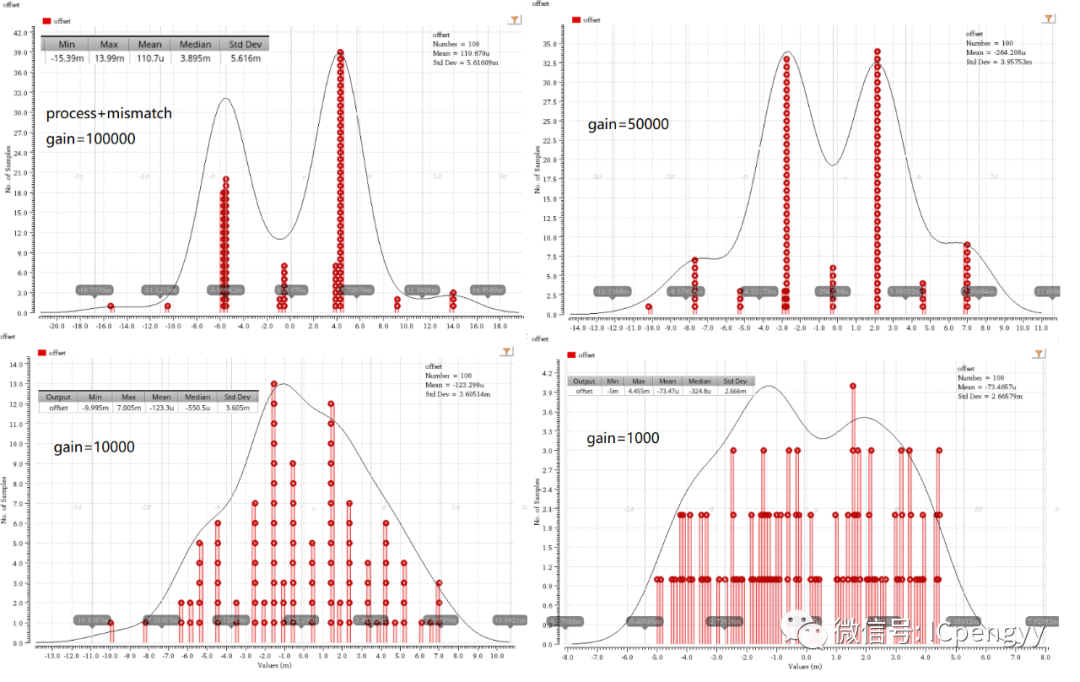

积分器增益设得太大或太小都会时失调电压统计规律不为高斯分布关系。原因时该反馈环路会有一个最小误差限制,该限制与环路增益相关,即也与积分器增益相关。

积分器增益越大,误差越小,蒙特卡洛仿真结果也就会有更多随机输出值,也就越准确。

对于ADC中常用的全差分比较器(四端输入)也可以使用类似的环路仿真方法近似求解输入失调电压。相同设置下,四输入比较器的失调电压接近两输入比较器失调电压的两倍。

四.其他

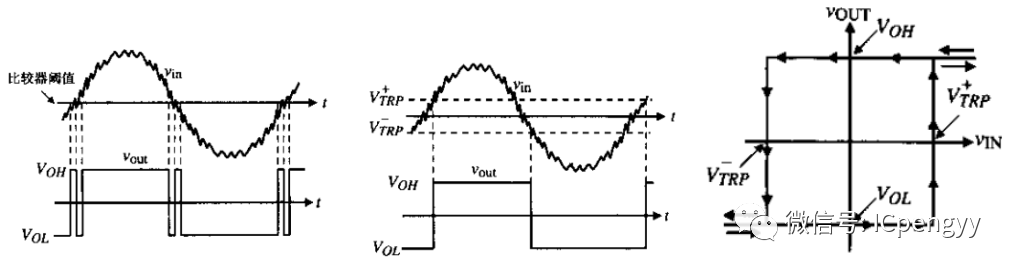

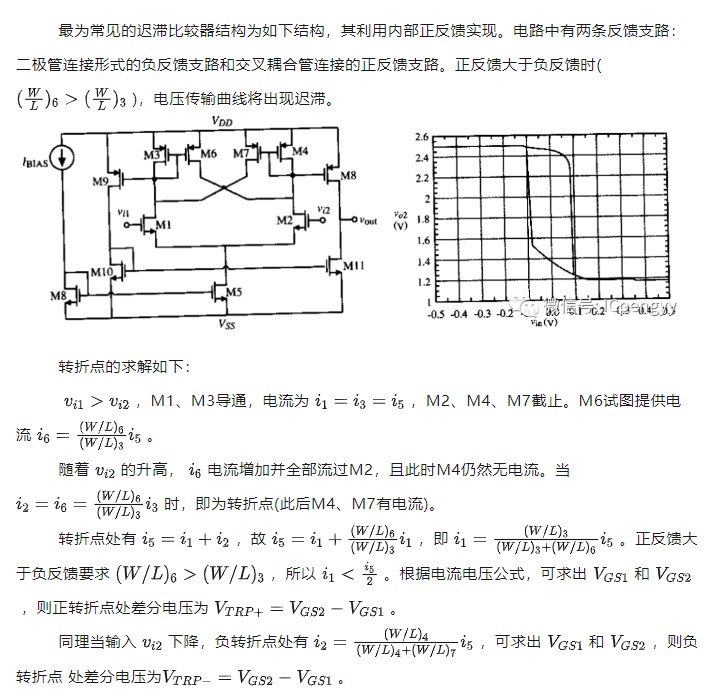

1)迟滞比较器

在噪声环境下,迟滞比较器因为具有不同的上升下降阈值电压,当迟滞电压差大于噪声电压,比较器输出就不会因为噪声的缘故出现毛刺。

2)失调消除

为了降低比较器失调,可利用单独的时钟相位实现失调消除。常用的方法为输出失调存储技术和 输入失调存储技术 。

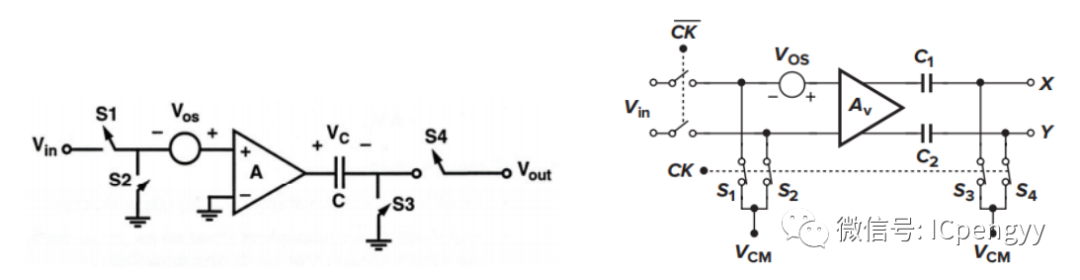

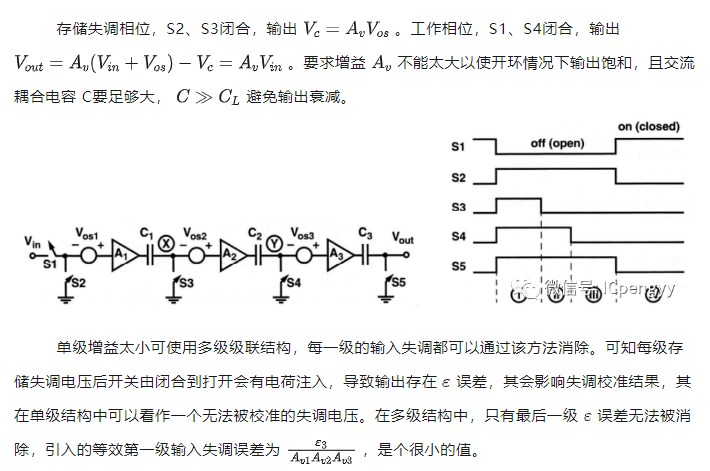

①输出失调存储技术

输出失调存储技术通过设置差分输入为零来测量失调,并将结果存储在与输出端串联的电容上。

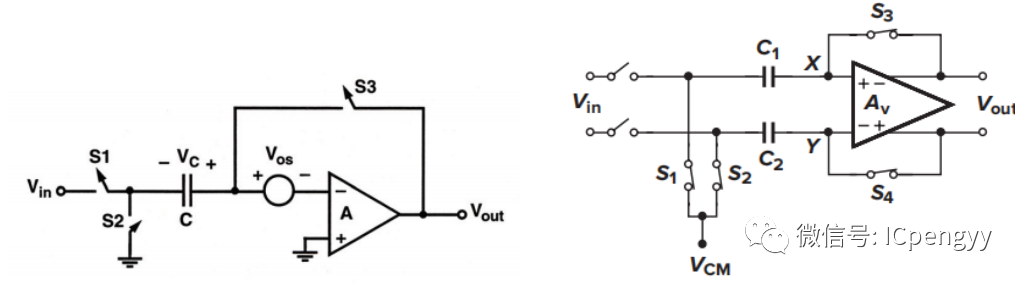

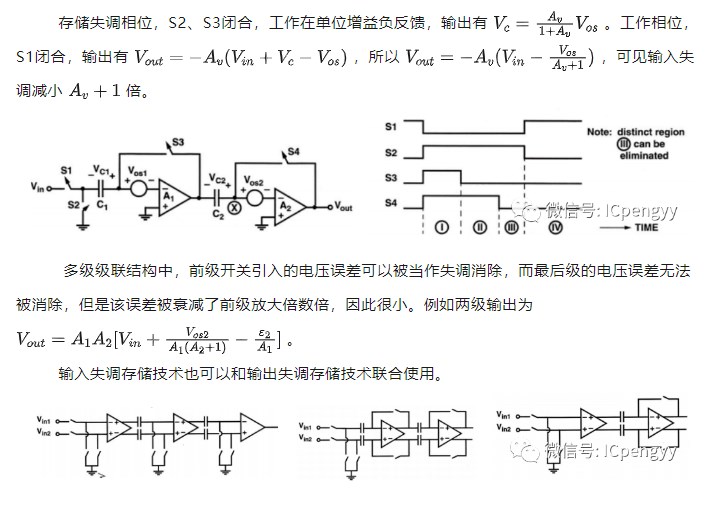

②输入失调存储技术

输入失调存储技术在输入端串联电容,利用单位增益负反馈实现失调电压存储。

-

什么是模拟集成电路?2011-11-14 0

-

模拟CMOS集成电路设计2016-05-15 0

-

基于Cadence与Mentor的CMOS模拟集成电路版图该如何去设计?2021-06-22 0

-

分享一份CMOS模拟集成电路设计手册2021-06-22 0

-

怎样去设计一种CMOS模拟集成电路2021-11-10 0

-

模拟集成电路原理与应用2008-08-28 1154

-

模拟集成电路基础与应用2008-11-02 935

-

模拟集成电路,模拟集成电路是什么意思2010-03-09 1811

-

模拟集成电路_模拟集成电路图书2011-10-28 2064

-

CMOS模拟集成电路设计.2版-艾伦2015-09-17 720

-

CMOS模拟集成电路的应用2016-01-11 751

-

CMOS模拟集成电路设计2018-03-26 1062

-

CMOS模拟集成电路设计与仿真(基本版)2021-05-31 1398

-

CMOS模拟集成电路设计(第3版)2021-12-06 5466

-

CMOS模拟集成电路EDA设计技术part12022-06-27 594

全部0条评论

快来发表一下你的评论吧 !