什么是AXI?AXI如何工作?

描述

UG761中文文档简介

Xilinx 从 Spartan-6 和 Virtex-6 器件开始采用高级可扩展接口 (AXI) 协议作为知识产权 (IP) 内核。Xilinx 继续将 AXI 协议用于针对 7 系列和 Zynq-7000 All Programmable SoC 器件的 IP。

本文件旨在

• 介绍 AXI 协议的关键概念

• 概述您可以使用哪些 Xilinx 工具来创建基于 AXI 的 IP

• 解释赛灵思采用了 AXI 的哪些特性

• 就如何将现有设计移植到 AXI 提供指导

什么是 AXI?

AXI 是 ARM AMBA 的一部分, AMBA 是 1996 年首次推出的微控制器总线系列。2003 年发布的AMBA 3.0 首次包含了第一版 AXI。2010 年发布的 AMBA 4.0 包含第二版 AXI,即 AXI4。

AXI4 接口有三种类型:

• AXI4-满足高性能内存映射要求。

• AXI4-Lite 用于简单、低吞吐量的内存映射通信(例如,控制寄存器和状态寄存器之间的通信)。

• AXI4-Stream-用于高速数据流。

赛灵思在 ISE 设计套件 12.3 版中引入了这些接口。

AXI 如何工作

AXI 规范描述了单个 AXI 主站和单个 AXI 从站之间的接口,代表了相 互 交 换 信息的 IP 内核。

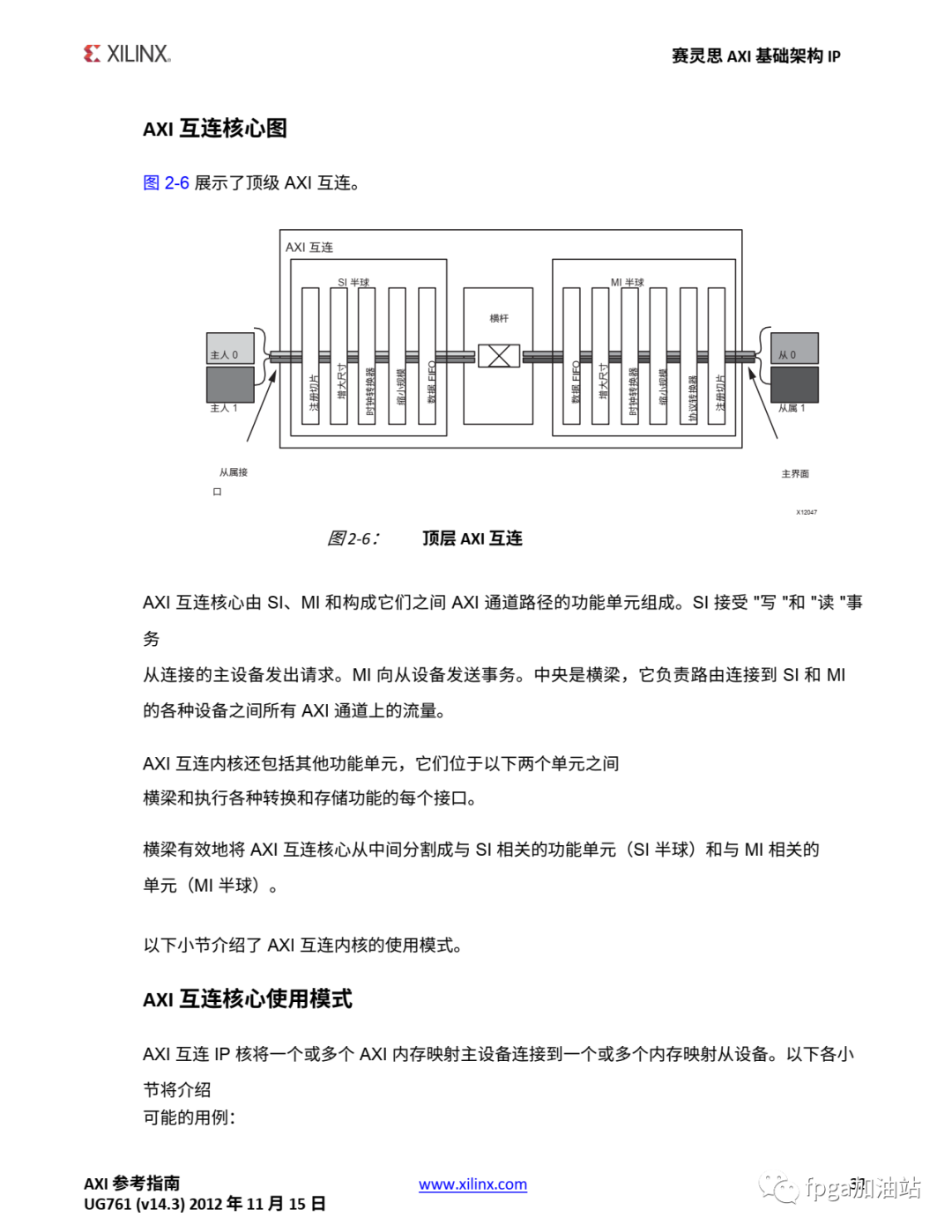

内存映射的 AXI 主站和从站可通过一种称为互连块的结构连接在一起。赛灵思 AXI 互连 IP 包含符合 AXI 标准的主站和从站接口,可用于在一个或多个 AXI 主站和从站之间路由事务。AXI 互连 IP 在第 17 页的 Xilinx AXI 互连核心 IP 中进行了描述。

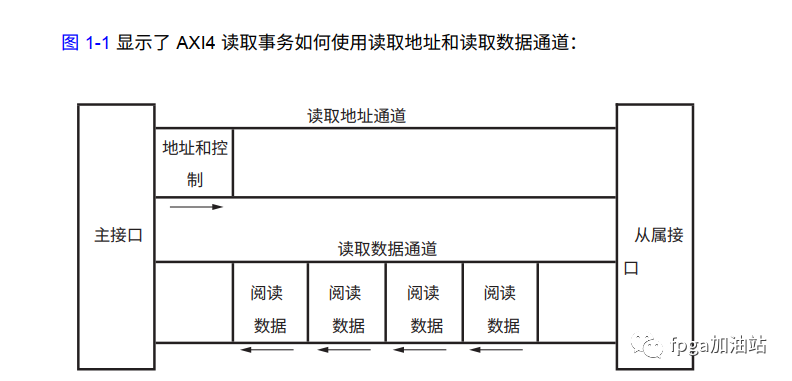

AXI4 和 AXI4-Lite 接口都由五个不同的通道组成:

• 读取地址通道

• 写入地址通道

• 读取数据通道

• 写入数据通道

• 写响应通道

数据可以同时在主站和从站之间双向移动,数据传输量也可以不同。AXI4 的限制是一次突发事务最多可传输 256 个数据。AXI4-Lite 每个事务只允许一次数据传输。

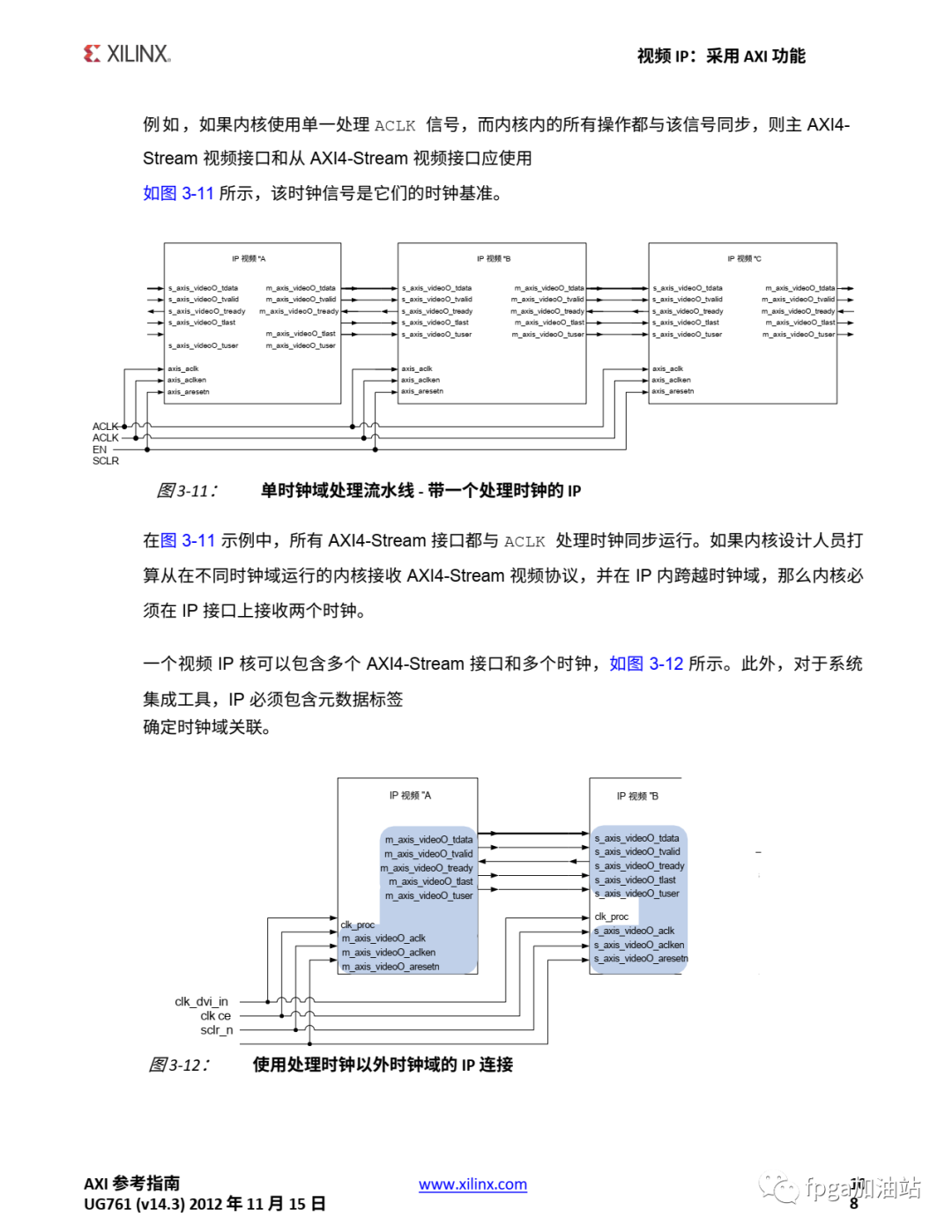

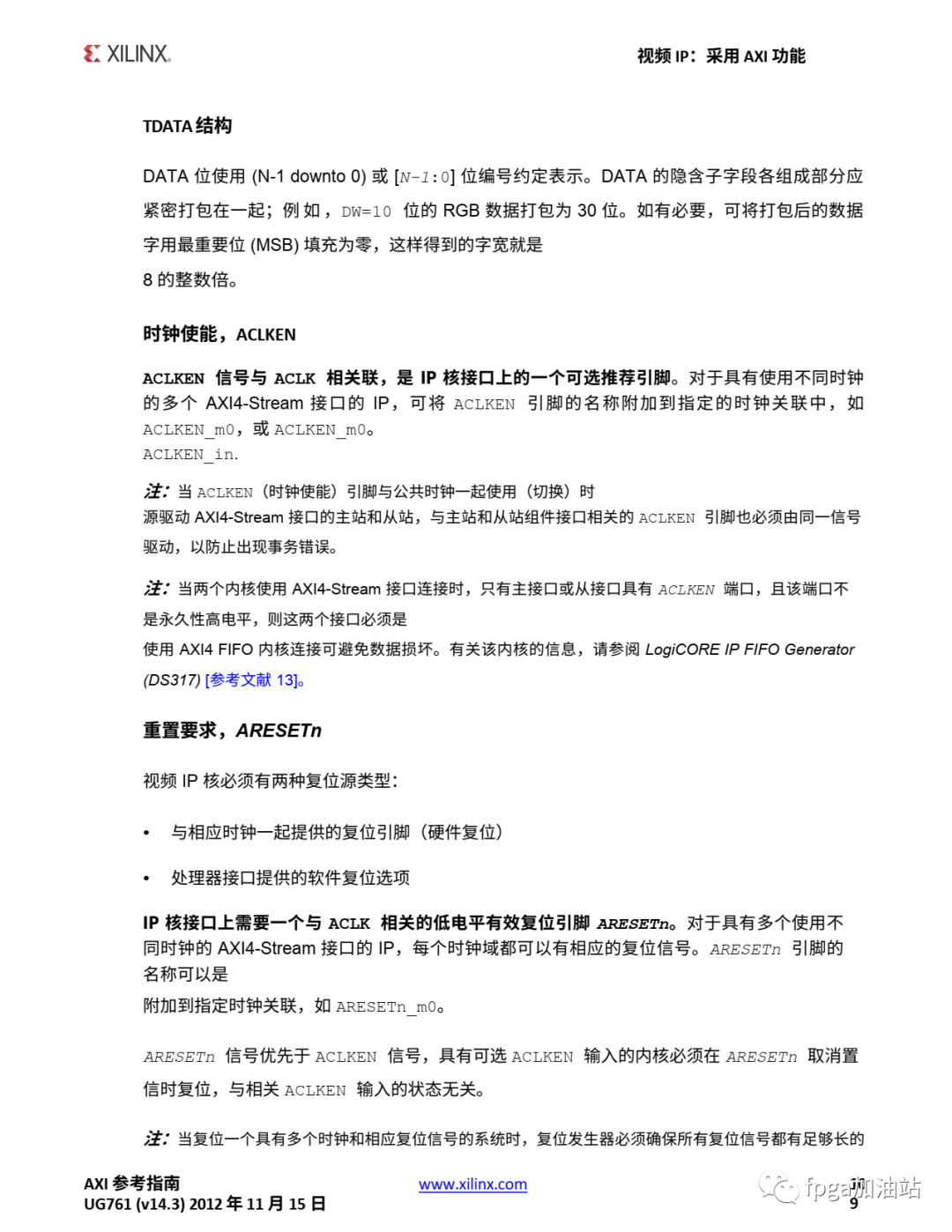

部分翻译截图(上下滑动查看)

审核编辑:汤梓红

-

AXI参考指南(英文资料)2012-12-23 1038

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 4430

-

AXI VIP设计示例 AXI接口传输分析2022-07-08 1343

-

AXI接口简介_AXI IP核的创建流程及读写逻辑分析2018-06-29 15234

-

何谓 AXI?关于AXI3/AXI4的相关基础知识2020-09-27 5967

-

你必须了解的AXI总线详解2020-10-09 6594

-

ZYNQ中DMA与AXI4总线2020-11-02 3948

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 6122

-

AXI通道定义及AXI总线信号描述2022-08-04 9864

-

AXI3与AXI4写响应的依赖区别2023-03-30 734

-

AXI总线工作流程2023-05-25 629

-

AXI VIP当作master时如何使用?2023-07-27 956

-

AXI VIP当作master时如何使用2023-07-27 692

-

AXI传输数据的过程2023-10-31 472

-

XILINX FPGA IP之AXI Traffic Generator2023-11-23 840

全部0条评论

快来发表一下你的评论吧 !