什么是 LLVM C/C++ 编译器?

描述

RISC-V 是一种模块化指令集架构 (ISA),具有强大的定制能力,在实现创新和差异化的同时而不会出现碎片化现象。在已批准/标准的 ISA 扩展(如整数指令或浮点指令)的基础模块之上,设计人员可以通过添加自定义指令而实现纯粹的设计自由!

通过添加自定义指令而实现更好的性能,更小的内存占用或者更低的功率,意味着软件(最终应用程序)要针对特定的 RISC-V ISA 进行编译。软件开发工具包(SDK)必须清楚地了解 RISC-V 处理器实现了哪些 ISA 模块,这样才能自动利用这些模块。这些指令包括标准指令和定制指令。

但是如何为特定的 RISC-V ISA 获取最佳的 SDK 呢?这里不得不提到 SDK 的重要组成部分--C/C++ 编译器。编译器必须尽可能能够自动、明智地使用这些自定义指令。

什么是 LLVM C/C++ 编译器?

LLVM(低级虚拟机)是一套编译器和工具,如汇编器、链接器或调试器。我们可以把重点放在编译器上。

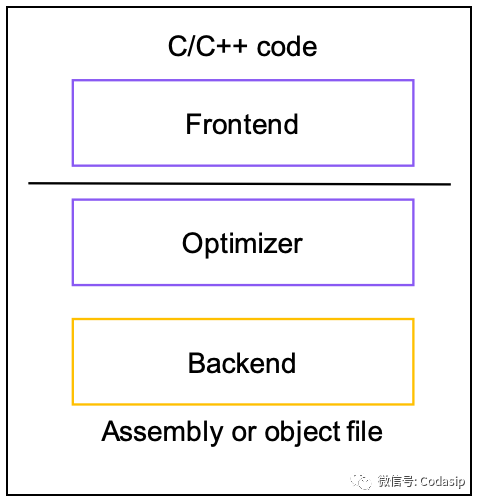

与其他编译器一样,LLVM 编译器可分为三个部分:前端、优化器(也称中端)和后端,如下图所示。每一层都有不同的用途。

LLVM 编译器前端

前端将 C 或 C++ 源代码作为文本文件输入。前端会对其进行解析,并创建一个中间表达(IR)。IR 以机器格式表示输入内容。

LLVM 编译器优化器

优化器接收 IR,主要针对独立的优化(如循环展开或常量/变量传播),并生成经过优化的 IR。

LLVM 编译器后端

后端接收优化后的 IR,并执行与目标相关的优化、寄存器分配、堆栈操作等。最后生成处理器的汇编代码。

对于可重定位目标性而言,后端是最重要的部分,因为它必须了解目标架构、指令等信息。而 Codasip 的解决方案生成的正是编译器后端。

重定向 LLVM C/C++ 编译器

对于这个问题,Codasip 的做法如下:

以CodAL作为处理器描述的单一来源

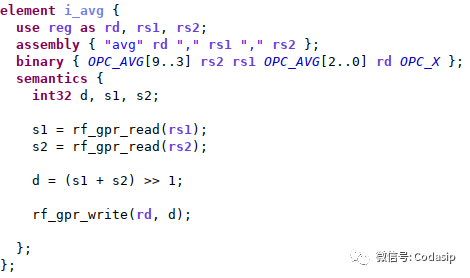

RISC-V ISA(包括自定义指令)是通过 CodAL 语言(一种基于 C 语言的处理器高级描述语言)捕获的。该语言捕获了所有重要信息,包括指令的文本形式、二进制编码以及更重要的指令行为。CodAL 描述还包含以下信息:不同类型的危险是如何递交的(它会影响指令调度)、指令是如何执行的(单周期、多周期)、处理器的应用二进制接口(例如,哪些寄存器用于堆栈)或其他微体系结构描述等。此外它还包含其它 C/C++ 编译器功能(例如窥孔优化-peephole optimizations)的说明。

下面的示例显示了一条表示两个数字平均值的简单指令。

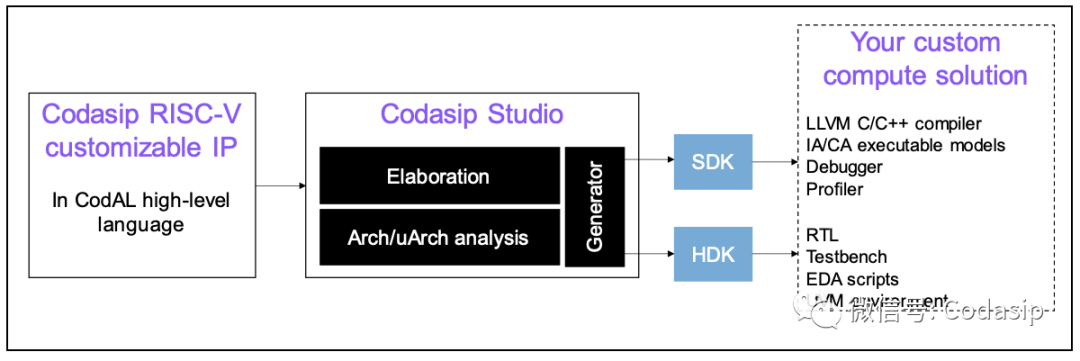

根据这一描述可以生成一系列工具。从下图中可以看到,生成的输出之一是 LLVM C/C++ 编译器。

C/C++ 编译器生成器会解析所有已描述的指令和微架构描述。然后提取指令语义、ABI 或时序,为前端和优化器生成新的后端和配置文件。换句话说,前端和优化器经过预编译和配置,可以快速探索设计空间。而后端则需要编译。生成的后端可以接收到 RISC-V 处理器的每一条指令,且上述指令可以由生成的 C/C++ 编译器自动使用,也可以通过自动生成的内建函数或内联汇编使用。

最独特的是,生成的后端向设计人员开放。如果设计人员想要添加新的 LLVM optimization pass,假设已经用 C++ 编写了一个optimization pass,那么就可以随时添加新的pass。

Codasip同时还改进了 vanilla LLVM。通过添加针对性能提升(例如改进的跳转线程、超级块调度或循环折叠/扁平化)、代码缩减(例如改进的-msave-restore、改进的多输出指令支持或机器大纲器)或 DSP 功能(例如零开销循环、双堆栈架构支持或带后增量/前增量的加载/存储)的高级optimization pass。

此时我们了解一下生成的 C/C++ 编译器在基准测试中的表现如何,并重点关注编译器的两个方面:性能和代码量。

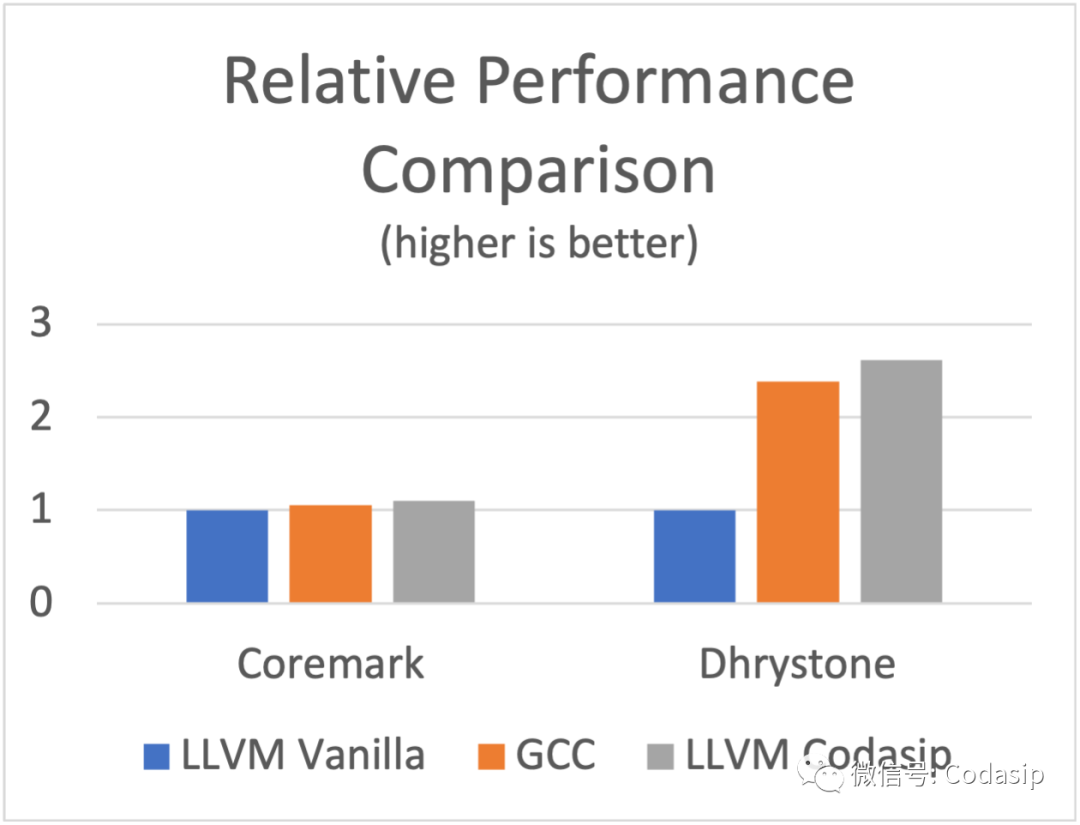

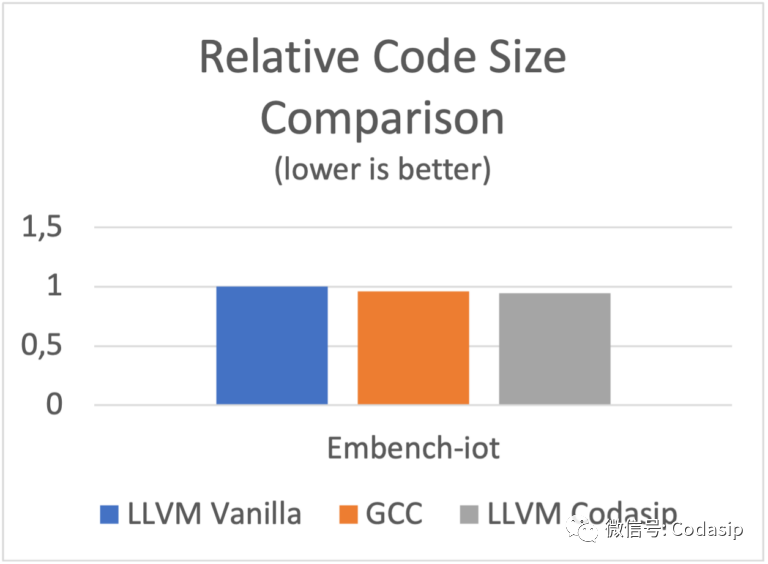

Coremark 和 Dhrystone 用于测量性能,Embench-iot 用于测量代码大小。我们比较了三种编译器: GCC、Vanilla LLVM 和 Codasip LLVM。比较是相对于其他编译器进行的,Vanilla LLVM 是参考编译器(即在图表中得分 1)。RISC-V ISA 配置为 RV32IMCB。

测试性能结果

性能比较显示了 Codasip LLVM 的改进,以及它如何优于其他编译器。请注意,所有编译器都使用了类似的优化标志。自定义指令可以明显改善结果。

代码大小结果

代码大小比较也显示了 Codasip LLVM 的优势,尽管差距并不大。在此,自定义指令也能明显改善结果。对于如何缩减RISC-V的代码大小,大家可通过IP&SoC杂志7/8月版的电子书查阅Codasip的迷你技术白皮书,链接如下:https://ipsoc.yunzhan365.com/books/stka/mobile/index.html

创新自动化助理 RISC-V的飞速发展

RISC-V ISA 仍在不断发展,行业急需一些方法来轻松探索不同指令及其对软件的影响(包括性能、代码大小或功耗等方面)。自动化是非常可取的,因为自动化流程可以快速高效地探索设计空间。或者说,如果设计人员想要创新或与众不同,那么他们就需要能够实现创新或与众不同的工具和语言,协助其达到目的。

而Codasip Studio 正是实现这一目标的有效方法。Codasip的处理器设计自动化工具集能从单一的真实源自动生成所有需要的部件。生成的 LLVM C/C++ 编译器可以自动使用新指令(也就是说,除非您愿意,否则无需更改 C/C++ 代码)。此外它在性能和代码大小方面的表现也非常出色。Codasip Studio 可以自动生成可执行模型、RTL 或验证工具,以完善 IP 工具包,并在最终产品中部署创新的 RISC-V 架构。

审核编辑:彭菁

-

请问对RX23T似乎不能对c++进行编译,是编译器版本问题吗?2018-07-23 0

-

C++笔记010:C++对C的扩展——register关键字增强2018-08-11 0

-

LLVM编译器编译过程2019-04-28 0

-

GPIO_PIN_RESET与C++编译器不兼容是什么原因导致的2022-12-19 0

-

S32DS C编译器/标准S32DS C++编译器-优化,,(-O3) 和 (-Os) 的MCU功能和性能是否完全相同?2023-04-06 0

-

MCUXPRESSO编译器C++有问题怎么处理?2023-04-20 0

-

LLVM clang 公开 -std=c++232023-05-27 0

-

如何为Arm编译C和c++代码2023-08-02 0

-

ARM编译器ARM C和C++库和浮点支持用户指南2023-08-10 0

-

Arm C/C++编译器开发人员和参考指南2023-08-10 0

-

Arm C/C++编译器22.1版开发人员和参考指南2023-08-11 0

-

主流的C语言编译器详细介绍2019-09-05 1205

-

基于C++编译器的节点融合优化方法2021-06-15 740

-

阿里云基础软件C/C++编译器的工作现状及挑战2021-06-23 2677

-

C/C++编译器的缺省字节对齐方式2023-04-15 755

全部0条评论

快来发表一下你的评论吧 !