怎样通过FPGA软件去读取USB2.0模块的数据

描述

首先来说一下USB这个大家都知道的东西吧:

USB通用串行总线,是应用在计算机领域的接口技术。USB接口具有传输速度快,可以广泛地应用在各类的高速数据传输当中,相比于大家熟悉的串口数据传输要快出不知道多少倍了。

我们最常见的当属USB2.0和USB3.0,这两个之间可以通用,但是也有区别:

1.USB3.0的速率是5Gbps,而USB2.0的速率是480Mbps。

2.从USB外观上来看,USB2.0通常是白色或黑色,而USB3.0则改为蓝色接口。

3.从USB插口引脚上来看,USB2.0采用4针脚设计,而USB3.0则采取9针脚设计,相比而言USB3.0功能更强大。

总结来说就是USB2.0很通用,因为很多电脑上可能没有USB3.0的接口,但是一定有USB2.0的接口,而且USB2.0的传输速度也能满足一般条件下的高速数据传输。

1.先附上所设计的实物图(想要电路pcb文件咨询博主),然后针对实物图一点点展开:

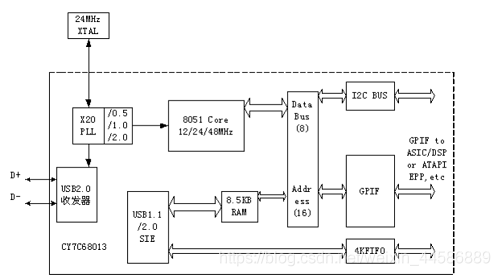

所选用的芯片是Cypress 公司的EZ-USB FX2 是世界上第一款集成USB2.0 的微处理器,它集成了USB2.0 收发器、SIE(串行接口引擎)、增强的8051 微控制器和可编程的外围接口。FX2 这种独创性结构可使数据传输率达到480MBit/s。在FX2中,智能SIE 可以硬件处理许多USB1.1 和USB2.0 协议,从而减少了开发时间

和确保了USB 的兼容性。该器件具有如下特性:

(1)内嵌480MBit/s 的收发器,锁相环PLL,串行接口引擎SIE集成了整个USB 2.0 协议的物理层。

(2)内嵌可工作在48MHz 的增强型8051,该8051 控制器具有以下特征:

具有256Byte 的寄存器空间,两个串口,三个定时器,两个数据指

针。

四个机器周期(工作在48MHz 下时为83.3ns)即组成一个指令周

期。

特殊功能寄存器(包括I/O 口控制寄存器)可高速访问。

应用USB 向量中断,具有极短的ISR 响应时间。

只用作USB 事务管理,控制,不参与数据传输,较好地解决了

USB 高速模式的带宽问题。

(3) “软配置”——USB 固件可由USB 总线下载,片上不需集成ROM。

(4) 拥有四个FIFO 接口,可工作在内部或外部时钟下。端点和FIFO 接口

的应用使外部逻辑和USB 总线可高速连接。

(5) 一种单片USB 2.0 外设解决方案,不需要外部的协议物理层,FX2 把所有的功能集成在一个芯片上。

然后下面这幅图片是FX2 控制器的内部结构图(参照了小梅哥的图片,在此安利一波小梅哥的FPGA,真的很好)。

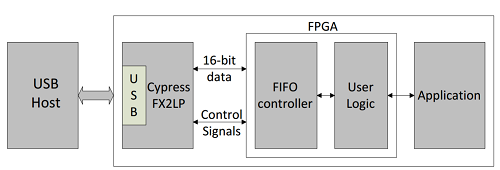

对于FX2 来说,可以通过两个不同的模式将 FX2 连接至 FPGA。这两个模式分别为通用可编程接口( GPIF)模式和从设备 FIFO 模式。

(1)GPIF 模式:在该模式下, FX2 作为外部系统的主设备使用,它所生成的所有控制信号用于对外部系统进行读和写操作。当外部系统不能作为 FX2 的主设备(例如,图像传感器与 FX2 相连接的 USB 摄像机应用)时,通常优先使用 GPIF 模式。在这种情况下,接口实现的复杂操作将由 FX2 执行。

(2)从设备 FIFO 模式(通常所用的模式,注重了解):在该模式下,连接至 FX2 的外部系统能够生成读和写控制信号,因此,它能作为FX2 的主设备使用。在基于FPGA 的应用中,FX2 一般被配置为从设备 FIFO 模式。下图为FX2 使用从设备FIFO 接口与外部FPGA 连接时的系统框图。

简单地说,在从设备FIFO模式下,FX2 中的8051 固件只是配置Slave FIFO 相关的寄存器。配置完成之后FPGA就可以按照Slave FIFO 的时序与主机进行通讯,通讯过程中不需要8051 固件。就相当于FPGA控制一个外设(比如就像控制一个串口一样简单)

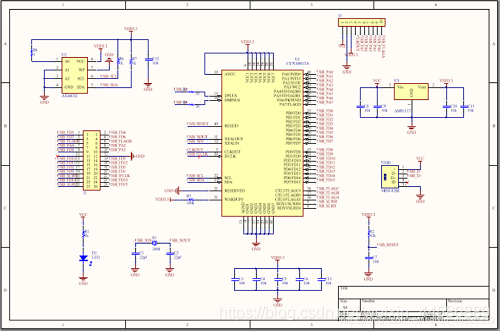

通讯原理搞明白之后就是根据引脚设计电路,原理图如下图所示:

2.下面就介绍如何具体控制USB2.0模块了:

Cypress 提供了一个基本的开发工具包,供用户开发USB 应用,名为ySuiteUSB3.4,网上关于USB2.0开发的资料也有很多,包括安装 FX2 的开发软件以及安装USB2.0模块的驱动程序,并且很重要的是在使用FPGA 控制USB2.0模块之前要对 USB2.0 芯片烧写固件(不同的应用模式下,所烧写的固件是不一样的)。想要资料可以咨询博主。

在配置完成之后可以通过官方网站提供的例程和上位机软件,使用FX2 芯片上的8051 完成数据在OUT 和 IN 端点间的搬运工作,在整个数据传输的过程中不需要有外部的设备(FPGA和STM32等控制器),通过USB2.0模块内部就可以完成数据的传输。但是实际工程中往往是将下位机采集到的数据通过USB2.0模块传输到上位机中,所以只通过USB2.0模块自身的数据回环实验是没有多大意义的,所以接下来就介绍如何通过FPGA来控制数据的传输。

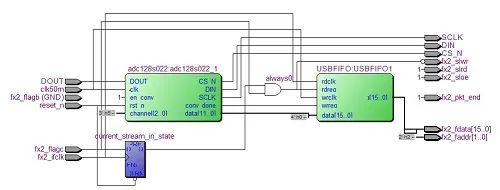

测试USB2.0模块辅助了AD模块(点击这里),将AD模块采集回来的数据通过FPGA送到USB2.0模块上,然后USB2.0模块将数据传输到电脑上,完成数据的高速采集,如下图所示是程序的RTL视图,从RTL视图可以直观地看到USB2.0模块的使用方法:

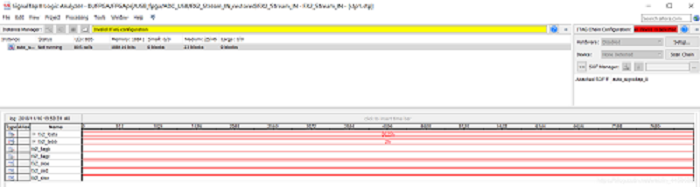

其中关于读取USB2.0模块的数据可以直接通过FPGA软件中的Signal Tap II逻辑分析仪来进行抓取,如图所示:

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:怎样通过FPGA软件去读取USB2.0模块的数据

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- F

-

基于FPGA的USB2.0设计2017-12-07 0

-

USB模块,USB2.0模块,USB数据采集模块,USB开发板2018-10-15 0

-

请问怎样去设计一种USB2.0控制器?2021-04-28 0

-

请问怎样去设计一种USB2.0虚拟逻辑分析仪?2021-05-08 0

-

请问怎样去设计一种USB2.0高速主机适配卡?2021-05-28 0

-

请问怎样去设计一种USB2.0数据传输系统?2021-06-03 0

-

labview难以高速接收USB2.0数据2021-06-25 0

-

怎样通过FPGA软件去读取USB2.0模块的数据呢2021-11-08 0

-

完整的USB2.0 OTG控制器硬件信号是怎样的呢2022-03-10 0

-

想问一下怎么用FPGA去驱动这个芯片来完成USB2.0协议?2023-03-21 0

-

基于FPGA的RTL级USB2.0协议层设计与实现2009-12-14 708

-

基于USB2.0与FPGA技术的高速数据采集系统的设计2009-04-22 1371

-

基于FPGA的USB2.0控制器设计2009-06-20 1520

全部0条评论

快来发表一下你的评论吧 !