SystemVerilog中的联合(union)介绍

描述

基本联合

在 SystemVerilog 中,联合只是信号,可通过不同名称和纵横比来加以引用。

其工作方式为通过 typedef 来声明联合,并提供不同标识符用于引用此联合。这些标识符称为“字段”。

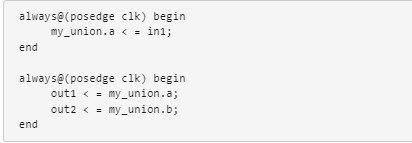

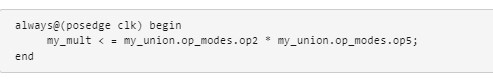

例如:

以上代码创建了一种新类型,名为“union_type”。

此类型的位宽为 4 位,可作为“a”或“b”来引用。

此外,代码最后一行创建了一个新信号,名称为“my_union”且类型为“union_type”。

其使用语法为“

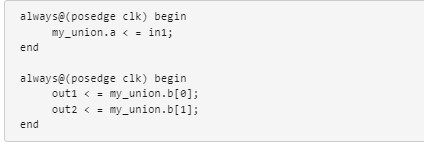

例如:

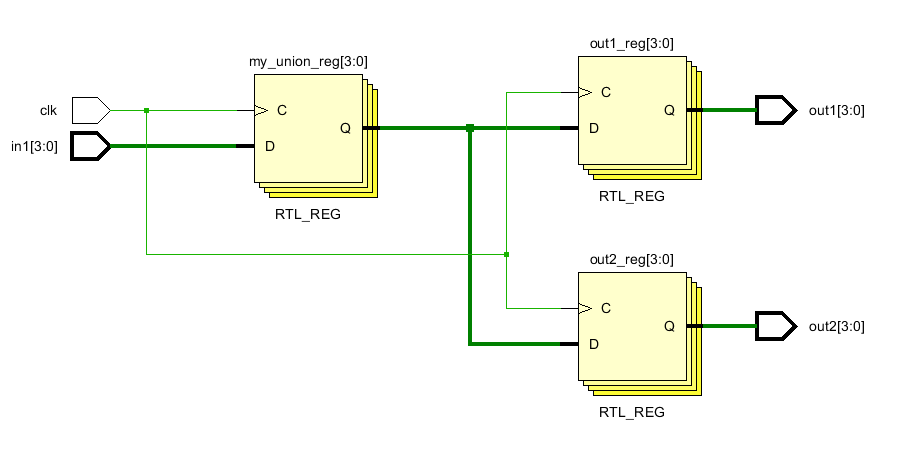

在 Vivado 中运行此代码时,原理图如下所示:

图 1:基本联合

请注意,my_union 位宽仍仅为 4 位,而以“a”或“b”来引用它的两项分配均采用相同逻辑。针对 my_union 的分配使用的是“a”,而此联合的读取结果针对 out1 和 out2 则分别使用“a”和“b”。

联合分两种类型:打包 (packed) 和解包 (unpacked)。在上述示例中,我们指定的是打包联合。默认情况下,如果不指定类型,编译器将假定它采用解包联合。

打包联合与解包联合的差别在于,在打包联合中,其中所有标识符都必须采用打包类型,并且大小必须相同。

在上述示例中,“a”和“b”位宽均为 4 位。但如果其中之一为 4 位,而另一个为 2 位,则该工具中将生成错误。而在解包联合中,标识符可采用解包类型并且大小无需相同。

因此,在上述 4 位和 2 位联合示例中,删除“packed”语句将使该工具能够对 RTL 进行完整审查。

总而言之,打包联合在综合工具中所受支持更为广泛,并且更便于概念化。对于本文中的前几个联合示例,我们使用的是打包联合,但从此处开始直至文末,我们将展示解包联合示例。

含多维字段的联合

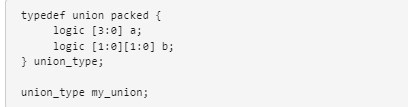

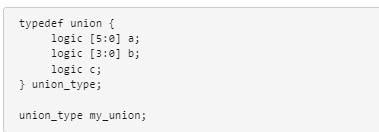

上述示例只是简单演示了联合的作用。让我们来看下较为复杂的联合示例:

同上,首先对联合进行声明,并创建类型为“union_type”的信号。差别在于,字段“a”位宽为 4 位,另一个字段“b”位宽同样为 4 位,但后者排列为 2 个 2 位矢量。由于这两个字段大小相同,并且字段“b”使用的是打包类型,因此这是一个合法的打包联合。

其结构如下所示:

图 2:含多维阵列的联合

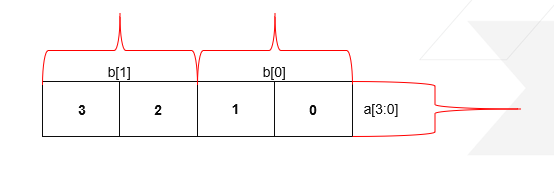

为此结构分配的 RTL 如下所示:

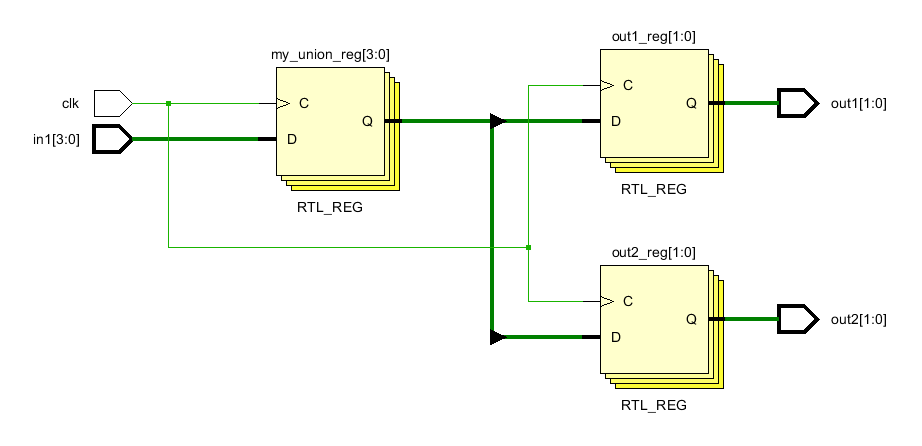

原理图如下所示:

图 3:多维联合的原理图

含结构的联合

联合还可配合结构一起使用。就像所有打包联合一样,结构大小必须与联合中的任何其他类型的大小相同。

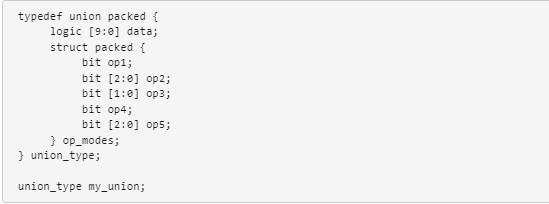

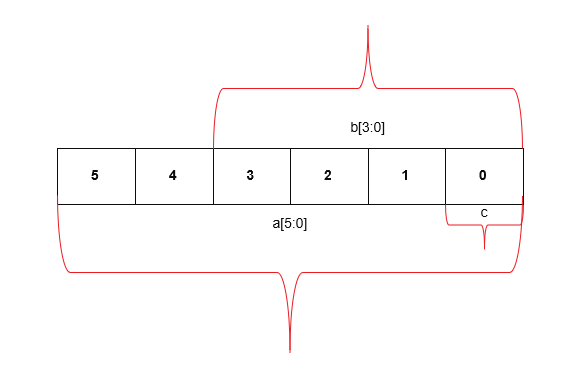

例如:

此 RTL 介绍的联合包含 2 个位宽均为 10 位的字段。第一个字段为名为“data”且位宽为 10 位的矢量。第二个字段采用包含 5 个字段的结构,这些字段的大小总和同样为 10 位。

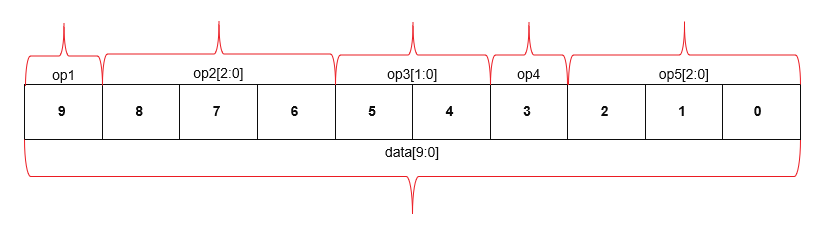

为此创建的结构如下所示:

图 4:含结构的联合

由于当前联合中包含结构,因此其正确的引用方式是引用联合中的结构:

解包联合

如果联合中的字段大小不同,或者如果联合中的字段本身使用的类型为解包类型,那么此类联合需声明为解包联合。

对于前一种情况,如果指定的联合包含不同大小的字段,那么该联合本身大小将设置为最大字段的大小。 示例 RTL:

这样即可创建如下所示结构:

图 5:含不同大小字段的解包联合

含结构的解包联合

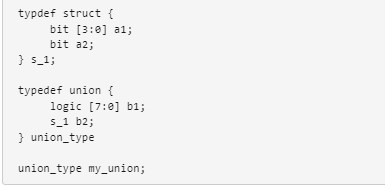

与打包联合相同,解包联合同样可以使用结构。

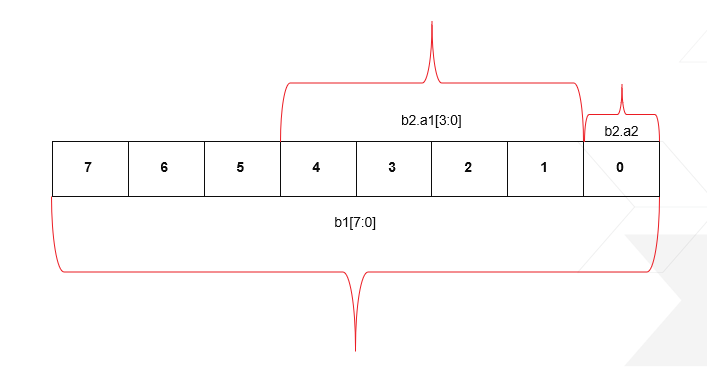

以上示例将创建一个含两个字段的联合。其中一个字段为位宽 8 位的矢量“b1”,另一个字段为位宽 5 位的结构,此结构由一个位宽 4 位的矢量 a1 和一个位宽 1 位的矢量 a2 组成。

此联合将作为位宽 8 位的矢量来创建,如下所示:

图 6:含结构的解包联合

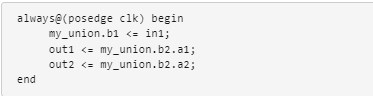

同上,由于联合中包含结构,因此需按如下方式来引用信号:

审核编辑:刘清

-

联合体union在labview如何建立2017-08-09 0

-

联合体问题2018-01-04 0

-

如何定义了这个联合体?2019-07-12 0

-

C语言union用于打包和拆包数据2020-09-28 0

-

请问UNION与UNION ALL的区别是什么?2020-11-17 0

-

结构体struct和联合体union的区别?2023-10-11 0

-

基于SystemVerilog语言的验证方法学介绍2011-05-09 857

-

SystemVerilog语言介绍汇总2021-10-11 2090

-

单片机编程之联合体(union)的妙用2021-11-13 550

-

union 的概念及在嵌入式编程中的应用2022-02-07 271

-

Xilinx SystemVerilog中的基本联合体2022-02-19 1011

-

Systemverilog中的union2022-11-09 621

-

SystemVerilog中的Packed Union2022-11-12 816

-

关键字union的基本定义和使用2023-04-15 1939

-

union和union all有什么区别2023-12-06 453

全部0条评论

快来发表一下你的评论吧 !