从零开始反相器的verilog设计

电子说

描述

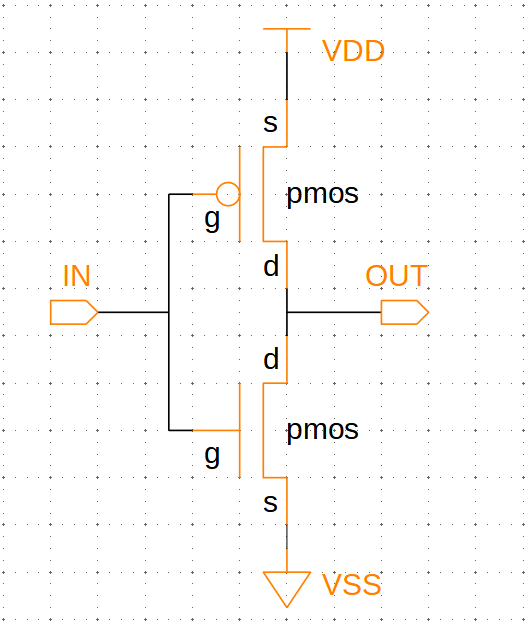

反相器的晶体管级电路

反相器,是数字集成电路最基本的电路之一。由一个pmos和一个nmos组成,输入信号IN接到pmos和nmos的栅极,输出信号OUT由漏极引出,如下图。

假设VDD=3.3V,VSS=0V,mos管的开启电压Vt=0.7V:

- 当IN=3.3V时,

- nmos的栅源电压Vgs>Vt,nmos导通,导通后漏源间的电阻Rds变得很小(比如0.1Ω),所以nmos漏极电压Vds就被拉到接近地。

- pmos的Vgs=0V,小于开启电压Vt,pmos关断,所以pmos的漏极电压由nmos决定。

- 综上,OUT≈0V。

- 当IN=0V时,

- nmos的Vgs=0V,nmos关断,输出由pmos决定。

- pmos的Vgs=-3.3V,大于开启电压Vt,pmos导通,Rds变得很小,pmos的输出被拉到接近VDD。

- 综上,OUT≈3.3V。

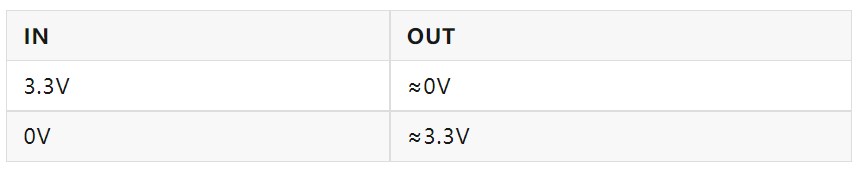

我们把输入输出关系整理如下表:

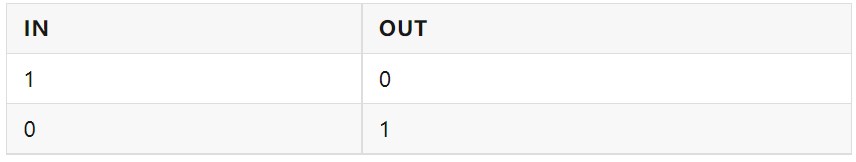

反相器的数字逻辑关系

数字集成电路不太关心电源和地的具体电压值,只关心输入输出逻辑关系。通用把接近VDD的电压称为高电平,用数字1表示,而接近VSS的电压称为低电平,用数字0来表示。

所以,反相器的输入输出电压关系用逻辑电平可表示为:

反相器的数学表示法

20世纪初,英国科学家香农指出,布尔代数(一种用来推理的数学)可以用来描述电路:布尔代数的运算法则正好与组合逻辑电路里的“与”、“或”和“非”相同。

交集(与):OUT = IN1 · IN2

并集(或):OUT = IN1 + IN2

差集(反相):OUT =

所以,非逻辑就对应反相器。

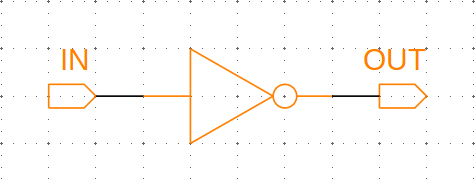

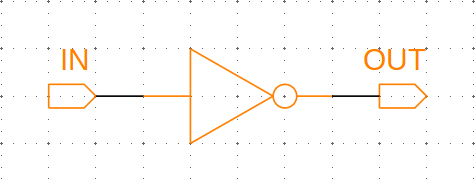

反相器的电路符号

在画反相器的门级电路符号时可以抽象成下面的符号。输出端的圆圈表示逻辑上相反。

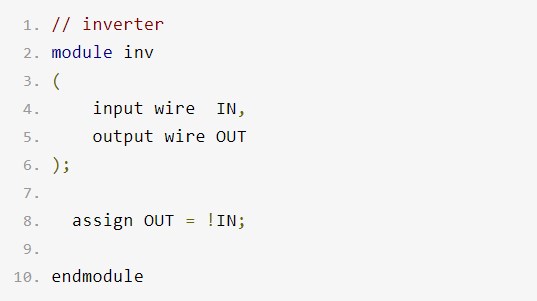

verilog描述

verilog,全称Verilog HDL,一种硬件描述语言,由美国gateway公司1983年创立。因为verilog从C语言里借鉴了一些语法规则,看起来与C语言有点像,所以在工程中得到广泛地推广和应用,因此成为了IEEE标准,IEEE1364。

我们来用verilog描述这个反相器电路的形为(也称为形为级描述):

第1行:注释

第2行:定义一个电路模块,电路模块的名字是inv

第4~5行:定义这个电路模块的输入和输出端口

第8行:描述了输出和输入之间的逻辑关系

第10行:结束这个电路模块的定义和描述

把这段verilog代码变成电路

用verilog写出来的这段代码,只是描述了电路模块端口和内部的逻辑。然后,使用逻辑综合工具,把verilog映射成由若干个提前设计好的基本单元电路(即工厂提供的标准单元库)连线而成的复杂电路。这种自动化的设计方法不再需要像模拟电路一样手工设计晶体管级的电路了,不仅大大加快了设计效率,也使得设计超大规模集成电路成为可能。

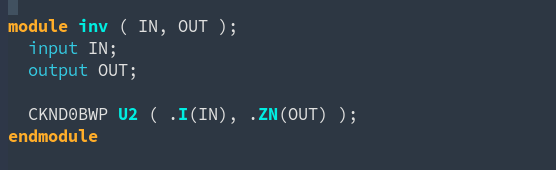

我们把上面的verilog用综合工具(比如synopsys dc)综合一下,得到下面的网表:

可以看到,综合工具把verilog描述的逻辑表达式自动替换成了由标准单元组成的电路了。(注:这里端口的定义格式稍有不一样,是采用的verilog95的风格。)

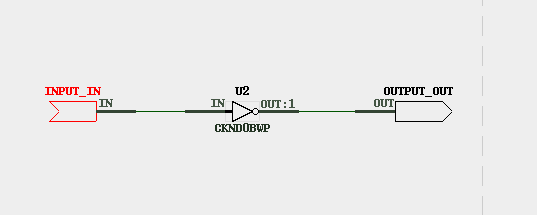

我们可以用网表查看工具自动绘制出门级电路图:

总结

本文从数字集成电路设计角度阐述了反相器的原理、数字逻辑表示方法、verilog语言的描述、再到把verilog代码转换回电路的方法和过程。后面会继续用这种思维带领大家学习和设计数字集成电路中的常用电路。

-

反相器构成的振荡器该如何分析?2024-01-26 0

-

从零开始学CPLD和Verilog HDL编程技术教程免费下载2012-02-06 0

-

《从零开始学电路基础》(从零开始学电子技术丛书)2012-06-05 0

-

labview从零开始2012-07-10 0

-

[从零开始学CPLD和Verilog HDL编程技术]高清版2012-08-15 0

-

《从零开始学系列电子书籍》大集合【值得收藏】!!!2012-08-15 0

-

反相器选型2016-04-28 0

-

[从零开始学CPLD和Verilog.HDL编程技术].李建清.2018-04-20 0

-

《从零开始学电子》丛书全套网盘分享2020-06-28 0

-

设计反相器如何解决PEX的问题?2021-06-24 0

-

反相器的输出不对!2023-08-24 0

-

反相器,反相器是什么意思2010-03-08 10888

-

cmos反相器设计电路图2018-03-27 79333

-

MOS反相器和CMOS反相器的详细资料说明2020-03-20 3193

-

从一个反相器开始说时序2023-06-27 1237

全部0条评论

快来发表一下你的评论吧 !