基于Verilog的经典数字电路设计(3)选择器

电子说

1.2w人已加入

描述

引言

在数字信号的传输过程中,有时需要从一组输入数据中选出某一个来,比如输入有 “A、B、C、D” 四个数据,那么我们想要哪个字母输出,就可以设置哪个字母输出,这里的设置,即所谓的 “选择开关” ;又或者,你可以理解为多个通道输入到单个通道的输出;于是,数据选择器(Data Selector)或多路开关(Multiplexer)的逻辑电路便应运而生。

一、2 选 1 数据选择器的 Verilog 代码实现和 RTL 电路实现

module Multiplexer(

input wire a, // 输入数据信号

input wire b, // 输入数据信号

input wire sel, // 输入控制信号

output result // 输出数据信号_已选择

);

assign result = sel ? a : b;

endmodule

这是 2 选 1 数据选择器的设计代码,非常简单明了,主要是输入数据 a 和 b,然后通过 sel 信号来选择输出是 a 还是 b。倘若 sel 拉高,即为 “1” 的时候,那么就输出 “a”,反之,倘若 sel 拉低,即为 “0” 的时候,那么就输出 “b”。

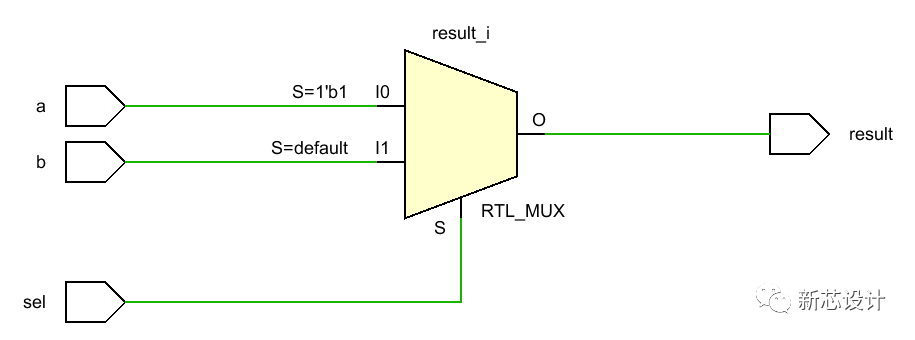

这是一个数据选择器设计,该设计是一个直接用组合逻辑语句或者也可以说是连续赋值语句 assign 的方式描述的电路,其 RTL 电路图如下所示:

2 选 1 数据选择器的 RTL 电路图

二、4 选 1 数据选择器的 Verilog 代码实现和 RTL 电路实现

module Multiplexer(

input wire a, // 输入数据信号

input wire b, // 输入数据信号

input wire c, // 输入数据信号

input wire d, // 输入数据信号

input wire [1:0] sel, // 输入控制信号

output reg result // 输出数据信号_已选择

);

always @(sel, a, b, c, d)

case (sel)

2'b00: result <= a;

2'b01: result <= b;

2'b10: result <= c;

2'b11: result <= d;

endcase

endmodule

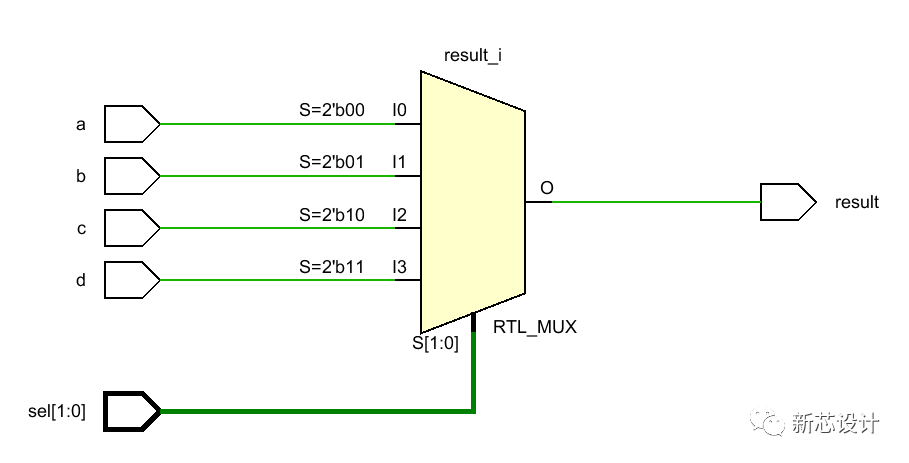

这是一个 4 选 1 数据选择器,基于查找表 LUT(Look Up Table)(查找表在 FPGA 中非常重要,软件思维可以理解为 “索引”,它是 FPGA 芯片架构的重要组成部分,合理利用查找表,能够使你的 FPGA 硬件工程达到一定程度的优化设计)的方式实现的一个电路,其 RTL 电路图如下所示:

4 选 1 数据选择器的 RTL 电路图

总结

数据选择器在实际生活中应用广泛。比如,在实际中对选手进行挑选,比如在歌手舞台对 “小洪” 编号为 “a”,对 “小华” 编号为 “b”,然后 “sel” 选择信号就交给 “裁判”,倘若 “小洪” 唱歌功底胜出,那么输出 “a”,反之输出 “b”,是不是很形象呢?!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

华为《高速数字电路设计教材》2014-09-01 0

-

招聘:数字电路设计师2015-02-27 0

-

数字电路设计与Verilog HDL2015-07-16 0

-

数字电路-数字时钟电路设计2016-12-06 0

-

数字电路设计的基本方法有哪些2019-02-27 0

-

数字电路经典2019-06-15 0

-

基于FPGA的多路选择器设计(附代码)2023-03-01 0

-

基于LabVIEW的数字电路设计和仿真2010-03-30 919

-

高速数字电路设计2007-10-16 2757

-

数字电路设计2009-08-26 2679

-

数字电路中的FPGA和verilog教程2016-01-18 589

-

数字电路设计方案中DSP与FPGA的比较与选择2017-01-18 903

-

FPGA CPLD数字电路设计经验分享.2021-09-18 956

-

数字电路设计的基本流程2022-07-10 6507

全部0条评论

快来发表一下你的评论吧 !