SoC(System on chip)与NoC(network-on-chip)

描述

SoC(System on-chip)与NoC(network-on-chip)

NoC是相对于SoC的新一代片上互连技术,要深入了解NoC必须深刻认识SoC,故本文组织结构为:

l SoC架构

l SoC的局限性

l SoC设计流程

l NoC架构

l NOC架构优势

l NoC 和 SoC 的区别

一.SoC基本架构

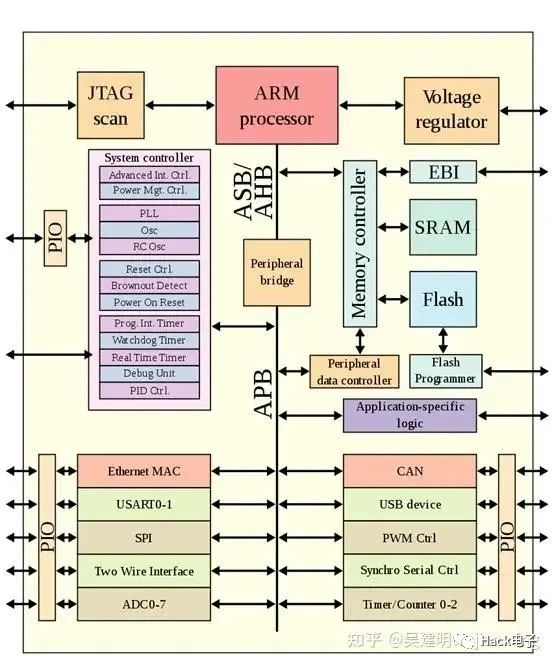

典型的系统级芯片结构包括以下部分:

·至少一个微控制器(MCU)或微处理器(MPU)或数字信号处理器(DSP),但是也可以有多个处理器内核;

·存储器可以是RAM、ROM、EEPROM和闪存中的一种或多种;

·用于提供时间脉冲信号的振荡器和锁相环电路;

·由计数器和计时器、电源电路组成的外设;

·不同标准的连线接口,如USB、火线、以太网、通用异步收发和序列周边接口等;

·用于在数字信号和模拟信号之间转换的ADC/DAC;

·电压调理电路及稳压器。

片上系统通讯架构(System on chip, SoC)SoC整体架构图如下:

二.SoC的局限性

目前,SoC通讯架构的设计相对比较成熟。大部分芯片公司芯片制造都采用SoC架构。然而,随着商业应用开始不断追求指令运行并存性和预测性,芯片中集成的核数目将不断增多,基于总线架构的SoC将逐渐难以不断增长的计算需求。其主要表现为:

1、可扩展性差。SoC系统设计是从系统需求分析开始,确定硬件系统中的模块。为了使系统能够正确工作,SoC中各物理模块在芯片上的位置是相对固定的。一旦在物理设计完毕后,要进行修改,实际上就有可能是一次重新设计的过程。另一方面,基于总线架构的SoC,由于总线架构固有的仲裁通信机制,即同一时刻只能有一对处理器核心进行通信,限制了可以在其上扩展的处理器核心的数量。

2、平均通信效率低。SoC中采用基于独占机制的总线架构,其各个功能模块只有在获得总线控制权后才能和系统中其他模块进行通信。从整体来看,一个模块取得总线仲裁权进行通信时,系统中的其他模块必须等待,直到总线空闲。

3、单一时钟同步问题。总线结构要求全局同步,然而随着工艺特征尺寸越来越小,工作频率迅速上升,达到10GHz以后,连线延时造成的影响将严重到无法设计全局时钟树的程度,而且由于时钟网络庞大,其功耗将占据芯片总功耗的大部分。

三.SoC设计流程

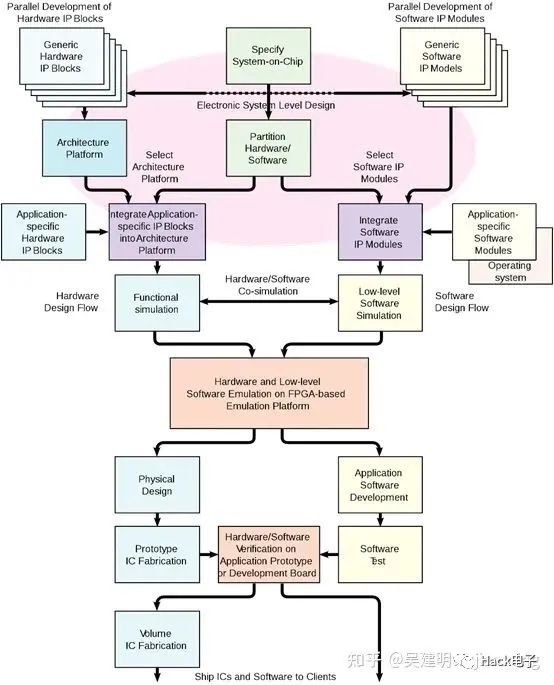

一个完整的系统级芯片由硬件和软件两部分组成,其中软件用于控制硬件部分的微控制器、微处理器或数字信号处理器内核,以及外部设备和接口。系统级芯片的设计流程主要是其硬件和软件的协同设计。

由于系统级芯片的集成度越来越高,设计工程师必须尽可能采取可复用的设计思路。大部分现今SoC都使用预定义的IP核(包括软核、硬核和固核),以可复用设计的方式来完成快速设计。在软件开发方面,协议栈是一个重要的概念,它用来驱动USB等行业标准接口。在硬件设计方面,设计人员通常使用EDA工具将已经设计好(或者购买)的IP核连接在一起,在一个集成开发环境(IDE)下集成各种子功能模块。

下图不是系统级芯片的设计流程示意图。

芯片设计在被送到晶圆厂进行流片生产之前,设计人员会采取不同方式对其逻辑功能进行验证。仿真与验证是SoC设计流程中最复杂,最耗时的环节,约占整个芯片开发周期的50%~80% ,采用先进的设计与仿真验证方法已成为SoC设计成功的关键。

四、NoC架构

Noc的发展是以SoC为基础。SoC通常是指在单一芯片上实现的数字计算机系统,通过总线完成其中各模块之间的交互,但随着半导体工艺和需求的快速发展,总线的宽度已经成为SoC发展的瓶颈,大大限制了SoC内部通信的速度。90年代NoC技术的提出也是因为借鉴了并行计算机的互联网络和以太网络的分层思想,二者的相同点有:支持包交换、路由协议、任务调度、可扩展等。NoC更关注交换电路和缓存器的面积占用,在设计时主要考量的方面也是这些。

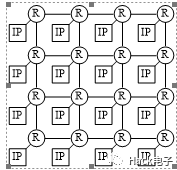

NoC将宏观网络的通讯措施应用于芯片上,每个核当做一个独立的单元,IP核经过网络接口与特定的路由器相连。将IP核之间的通信转换为路由器与路由器的通信。通常情况下的NoC架构如下图所示:

R为路由节点,IP为计算节点。

传统的NoC架构主要由路由器节点、IP核、资源网络接口、通道组成。

1、资源节点:主要包含计算节点和存储节点。计算节点包含处理器即IP核(CPU、DSP等),存储节点包含ROM、RAM、DRAM、SDRAM等

2、通信节点:即路由节点或路由器,主要负责完成IP核之间的数据通信任务。NoC中资源节点产生一个数据包后,会通过特定的接口发送到源路由器中,源路由器会读取数据包的头微片中的地址信息,通过特定的路由算法计算出最佳路由路径,从而树立可靠的传输到目的节点,最终由目的IP核接收此信息。

3、资源网络接口:其功能就是作为通信节点与功能节点之间的接口。主要功能有完成数据包的封装与解封装,在源节点的资源网络接口中将原地址信息以及目的地址信息等封装到数据包的头微片中;在目的节点的资源网络接口中将原地址信息以及目的地址信息等删除。

4、通道:实质为双向金属链路,用以保证节点间的数据传输。分为内部通道和外部通道,内部通道为资源节点和通信节点之间的金属链路,外部通道指通信节点之间的金属链路。

五.NOC架构优势

1、良好的可扩展能力。一方面,相比于SoC架构,不在受限于总线架构,可以扩展任意数量的计算节点。另一方面,需要对系统功能进行扩展时,只需要将设计好的功能模块通过资源网络接口植入网络,无需重新设计网络整体架构。

2、较高的通信效率。一方面NoC将IP核之间的数据传输演变成为路由器之间的数据转发,IP核节约了一部分的计算资源。另一方面避免了总线架构同一时刻只能有一对通信节点进行通信的问题,可以实现同一时刻多对节点通信。

3、功耗。NoC中采用全局异步局部同步的时钟机制,其功耗开销远低于SoC。NoC中局部模块运用同步时钟域,而全局上采用异步时钟,降低了由于全局时钟同步所带来的动态开销,同时,NoC中的时钟树设计复杂度也低于SoC。

4、数据传输可靠性。随着集成电路特征尺寸的不断减小,电路规模的不断增大,互连线的宽度和间距也在不断地减小,线间耦合电容相应增大,长的全局并行总线会引起较大的串扰噪声,从而影响信号的完整性以及信号传输的正确性。同时,互连线上的延迟将成为影响信号延迟的主要因素,总线结构全局互连线上的延迟将大于一个时钟周期,从而使得时钟的偏移很难管理。

六.NoC 和 SoC 的区别

SoC:System on Chip,中文称为片上系统,主要是针对 ASIC 或者 chip 来讲的。在 ASIC 设计的早期,由于制造工艺和性能等的约束,大部分芯片都单纯地实现某个特定功能,如处理器内核、总线、内存控制器、蓝牙等都由各自独立的芯片分别实现,处理器之间的通信也以多颗芯片互连的方式实现。

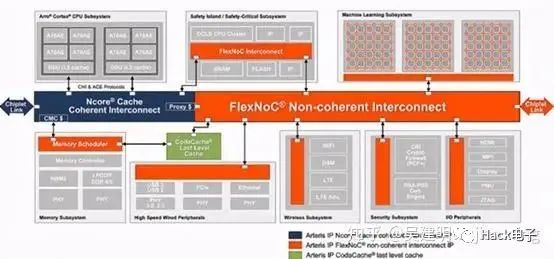

随着制造工艺的提升,以及设计能力的增强,单颗 ASIC 的功能越来越全面和强大,在一颗芯片内完全可以实现诸如处理器内核、总线、内存控制器、蓝牙等所有的功能。同时,ASIC 规模增大导致设计愈来愈复杂,因此,以 IP 核互连为核心的设计方法学应用而生。

这样,就出现了在一颗芯片里集成了大量的处理器内核、总线、控制器等 IP,而处理器内核数量也由曾经的单核增大到多核、众核。在这种情况下,设计方法学完全不同于以往 ASIC 的设计方法学,因此,诞生了 SoC 的概念,以和 ASIC 进行区别。不严格地说,一颗 SoC 可以实现以前多颗 ASIC 构成的系统。

NoC:Network on Chip,中文称之为片上网络。随着 SoC 技术的发展,芯片内部的 IP 核越来越多,有可能在一颗芯片中集成了数以百记的处理器内核(包括同构处理器内核和异构处理器内核)、数以千计控制器 IP 核等等,那么这种情况下 IP 核之间的互联就成为 SoC 性能一个重要组成部分。

而 NoC 技术的诞生就是为了能够让 IP 核之间的通信能够实现高效、高吞吐量、低功耗的目的。因此 NoC 技术主要研究对象就是各种互连方法、互连结构,以及 IP 核互联网络中路由算法。NoC 技术目前还处于学术研究阶段,大部分学术论文里都是仿真结果,工业界也有应用实例,但是比较少。

-

2.4-GHz Bluetooth® low energy System-on-Chip(蓝牙4.0)2011-02-13 0

-

CHIP1是如何知道扫描发生的?2018-12-29 0

-

SOC(system-on-a-chip) Verficat2009-07-10 376

-

System-on-a-Chip Design2009-07-27 548

-

A True System-on-Chip solution2009-11-14 451

-

基于电路交换的NoC路由器设计与实现2009-12-14 421

-

CC2511F16,pdf(Low-Power SoC (System-on-Chip))2010-07-02 418

-

CC2431,pdf(System-on-Chip for2010-07-06 614

-

基于FPGA的NoC验证平台的构建2011-01-04 583

-

什么是Chip2010-02-22 2309

-

CC253x System-on-Chip Solution for 2.4-GHz2013-09-04 592

-

走近SoC 预告篇2022-02-07 166

-

从SoC到NoC:芯片架构的演进与变革2023-05-11 8028

-

传智驿芯联手Arteris,利用创新NoC技术驾驭复杂SoC设计2023-09-18 357

全部0条评论

快来发表一下你的评论吧 !