IC设计:clock-gating综合实现方案

EDA/IC设计

描述

1、Clock-gating 说明

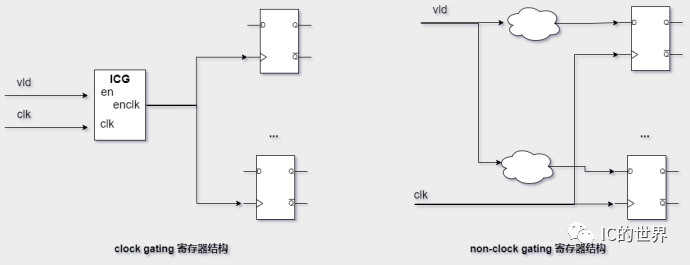

在ASIC设计中,项目会期望设计将代码写成clk-gating风格,以便于DC综合时将寄存器综合成clk-gating结构,其目的是为了降低翻转功耗。因为当控制信号(vld_in)无效时,使用了clk-gating后的寄存器,其CK(clk)端口一直为0,因此不存在翻转,能够有效降低寄存器的翻转功耗和对应的时钟树的翻转功耗。如下所示:下图左侧是DC综合后的clk -gating结构图,使用了ICG模块进行时钟gating,被gating后的时钟连接到寄存器的CK端。右侧是没有被clk-gating的寄存器结构图。

2、Clock-gating 编码风格

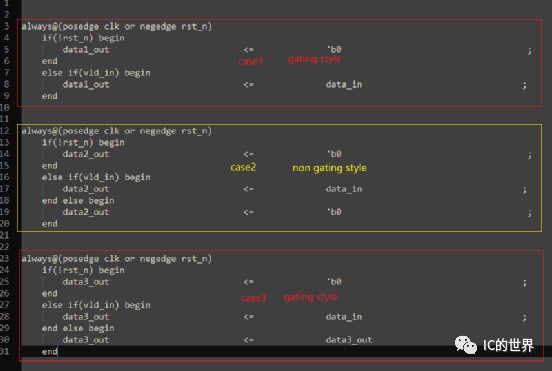

如下图所示,case1和case3 为gating style风格。DC综合时更容易产生clk gating。NOTE: 这里说的是更容易,而不是一定。综合工具会根据同一组(同一个vld控制的)的寄存器bit位数量进行决策,如果数量过少,则不进行clk gating,因为使用ICG模块本身就存在面积和功耗的增加。

案例1中,data为3bit,则没有产生clk gating。

案例2中,data为7bit,data1_out和data3_out均产生了产生clk gati

3、data位宽3bit

3.1 RTL代码

module try_top (

input clk , //

input rst_n , //

input vld_in , //

input [3-1:0] data_in , //

output reg vld_out , //

output reg [3-1:0] data3_out , //

output reg [3-1:0] data1_out , //

output reg [3-1:0] data2_out //

);

always@(posedge clk or negedge rst_n)

if(!rst_n) begin

vld_out <= 1'b0 ;

end

else begin

vld_out <= vld_in ;

end

always@(posedge clk or negedge rst_n)

if(!rst_n) begin

data1_out <= 'b0 ;

end

else if(vld_in) begin

data1_out <= data_in ;

end

always@(posedge clk or negedge rst_n)

if(!rst_n) begin

data2_out <= 'b0 ;

end

else if(vld_in) begin

data2_out <= data_in ;

end else begin

data2_out <= 'b0 ;

end

always@(posedge clk or negedge rst_n)

if(!rst_n) begin

data3_out <= 'b0 ;

end

else if(vld_in) begin

data3_out <= data_in ;

end else begin

data3_out <= data3_out ;

end

endmodule

3.2 网表文件--没有产生clk-gating

module try_top ( clk, rst_n, vld_in, data_in, vld_out, data3_out, data1_out,

data2_out );

input [2:0] data_in;

output [2:0] data3_out;

output [2:0] data1_out;

output [2:0] data2_out;

input clk, rst_n, vld_in;

output vld_out;

wire n6, n8, n10, n12, n14, n16, n18, n20, n22, n24, n26;

SDFFRPQL_*CELL_TYPE* data2_out_reg_0_ ( .D(n6), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n24), .Q(data2_out[0]) );

SDFFRPQL_*CELL_TYPE* vld_out_reg ( .D(vld_in), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n24), .Q(vld_out) );

SDFFRPQL_*CELL_TYPE* data1_out_reg_2_ ( .D(n22), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n24), .Q(data1_out[2]) );

SDFFRPQL_*CELL_TYPE* data1_out_reg_1_ ( .D(n20), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n24), .Q(data1_out[1]) );

SDFFRPQL_*CELL_TYPE* data1_out_reg_0_ ( .D(n18), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n24), .Q(data1_out[0]) );

SDFFRPQL_*CELL_TYPE* data3_out_reg_2_ ( .D(n16), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n24), .Q(data3_out[2]) );

SDFFRPQL_*CELL_TYPE* data3_out_reg_1_ ( .D(n14), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n24), .Q(data3_out[1]) );

SDFFRPQL_*CELL_TYPE* data3_out_reg_0_ ( .D(n12), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n24), .Q(data3_out[0]) );

SDFFRPQL_*CELL_TYPE* data2_out_reg_2_ ( .D(n10), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n24), .Q(data2_out[2]) );

SDFFRPQL_*CELL_TYPE* data2_out_reg_1_ ( .D(n8), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n24), .Q(data2_out[1]) );

INVP_*CELL_TYPE* U18 ( .A(rst_n), .Y(n24) );

AND2_*CELL_TYPE* U19 ( .A(data_in[1]), .B(vld_in), .Y(n8) );

AND2_*CELL_TYPE* U20 ( .A(data_in[2]), .B(vld_in), .Y(n10) );

AND2_*CELL_TYPE* U21 ( .A(data_in[0]), .B(vld_in), .Y(n6) );

INVP_*CELL_TYPE* U22 ( .A(vld_in), .Y(n26) );

AO21_*CELL_TYPE* U23 ( .A0(data3_out[1]), .A1(n26), .B0(n8), .Y(n14) );

AO21_*CELL_TYPE* U24 ( .A0(data3_out[0]), .A1(n26), .B0(n6), .Y(n12) );

AO21_*CELL_TYPE* U25 ( .A0(data1_out[0]), .A1(n26), .B0(n6), .Y(n18) );

AO21_*CELL_TYPE* U26 ( .A0(data1_out[1]), .A1(n26), .B0(n8), .Y(n20) );

AO21_*CELL_TYPE* U27 ( .A0(data3_out[2]), .A1(n26), .B0(n10), .Y(n16)

);

AO21_*CELL_TYPE* U28 ( .A0(data1_out[2]), .A1(n26), .B0(n10), .Y(n22)

);

endmodule

4、data位宽7bit

4.1 RTL代码

module try_top (

input clk , //

input rst_n , //

input vld_in , //

input [7-1:0] data_in , //

output reg vld_out , //

output reg [7-1:0] data3_out , //

output reg [7-1:0] data1_out , //

output reg [7-1:0] data2_out //

);

always@(posedge clk or negedge rst_n)

if(!rst_n) begin

vld_out <= 1'b0 ;

end

else begin

vld_out <= vld_in ;

end

always@(posedge clk or negedge rst_n)

if(!rst_n) begin

data1_out <= 'b0 ;

end

else if(vld_in) begin

data1_out <= data_in ;

end

always@(posedge clk or negedge rst_n)

if(!rst_n) begin

data2_out <= 'b0 ;

end

else if(vld_in) begin

data2_out <= data_in ;

end else begin

data2_out <= 'b0 ;

end

always@(posedge clk or negedge rst_n)

if(!rst_n) begin

data3_out <= 'b0 ;

end

else if(vld_in) begin

data3_out <= data_in ;

end else begin

data3_out <= data3_out ;

end

endmodule

4.2.网表文件--产生了clk-gating

module try_top ( clk, rst_n, vld_in, data_in, vld_out, data3_out, data1_out,

data2_out );

input [6:0] data_in;

output [6:0] data3_out;

output [6:0] data1_out;

output [6:0] data2_out;

input clk, rst_n, vld_in;

output vld_out;

wire clk_gclk_0, n3, n5, n7, n9, n11, n13, n15, n31;

SNPS_CLOCK_GATE_HIGH_try_top inferred_cg_0 ( .CLK(clk), .EN(vld_in), .ENCLK(

clk_gclk_0), .TE(1'b0) );

SDFFRPQL_*CELL_TYPE* data3_out_reg_0_ ( .D(data_in[0]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data3_out[0]) );

SDFFRPQL_*CELL_TYPE* data2_out_reg_0_ ( .D(n3), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n31), .Q(data2_out[0]) );

SDFFRPQL_*CELL_TYPE* vld_out_reg ( .D(vld_in), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n31), .Q(vld_out) );

SDFFRPQL_*CELL_TYPE* data1_out_reg_6_ ( .D(data_in[6]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data1_out[6]) );

SDFFRPQL_*CELL_TYPE* data1_out_reg_5_ ( .D(data_in[5]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data1_out[5]) );

SDFFRPQL_*CELL_TYPE* data1_out_reg_4_ ( .D(data_in[4]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data1_out[4]) );

SDFFRPQL_*CELL_TYPE* data1_out_reg_3_ ( .D(data_in[3]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data1_out[3]) );

SDFFRPQL_*CELL_TYPE* data1_out_reg_2_ ( .D(data_in[2]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data1_out[2]) );

SDFFRPQL_*CELL_TYPE* data1_out_reg_1_ ( .D(data_in[1]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data1_out[1]) );

SDFFRPQL_*CELL_TYPE* data1_out_reg_0_ ( .D(data_in[0]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data1_out[0]) );

SDFFRPQL_*CELL_TYPE* data3_out_reg_6_ ( .D(data_in[6]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data3_out[6]) );

SDFFRPQL_*CELL_TYPE* data3_out_reg_5_ ( .D(data_in[5]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data3_out[5]) );

SDFFRPQL_*CELL_TYPE* data3_out_reg_4_ ( .D(data_in[4]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data3_out[4]) );

SDFFRPQL_*CELL_TYPE* data3_out_reg_3_ ( .D(data_in[3]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data3_out[3]) );

SDFFRPQL_*CELL_TYPE* data3_out_reg_2_ ( .D(data_in[2]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data3_out[2]) );

SDFFRPQL_*CELL_TYPE* data3_out_reg_1_ ( .D(data_in[1]), .SI(1'b0), .SE(

1'b0), .CK(clk_gclk_0), .R(n31), .Q(data3_out[1]) );

SDFFRPQL_*CELL_TYPE* data2_out_reg_6_ ( .D(n15), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n31), .Q(data2_out[6]) );

SDFFRPQL_*CELL_TYPE* data2_out_reg_5_ ( .D(n13), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n31), .Q(data2_out[5]) );

SDFFRPQL_*CELL_TYPE* data2_out_reg_4_ ( .D(n11), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n31), .Q(data2_out[4]) );

SDFFRPQL_*CELL_TYPE* data2_out_reg_3_ ( .D(n9), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n31), .Q(data2_out[3]) );

SDFFRPQL_*CELL_TYPE* data2_out_reg_2_ ( .D(n7), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n31), .Q(data2_out[2]) );

SDFFRPQL_*CELL_TYPE* data2_out_reg_1_ ( .D(n5), .SI(1'b0), .SE(1'b0),

.CK(clk), .R(n31), .Q(data2_out[1]) );

INVP_*CELL_TYPE* U13 ( .A(rst_n), .Y(n31) );

AND2_*CELL_TYPE* U14 ( .A(vld_in), .B(data_in[6]), .Y(n15) );

AND2_*CELL_TYPE* U15 ( .A(vld_in), .B(data_in[5]), .Y(n13) );

AND2_*CELL_TYPE* U16 ( .A(vld_in), .B(data_in[4]), .Y(n11) );

AND2_*CELL_TYPE* U17 ( .A(vld_in), .B(data_in[3]), .Y(n9) );

AND2_*CELL_TYPE* U18 ( .A(vld_in), .B(data_in[2]), .Y(n7) );

AND2_*CELL_TYPE* U19 ( .A(vld_in), .B(data_in[1]), .Y(n5) );

AND2_*CELL_TYPE* U20 ( .A(vld_in), .B(data_in[0]), .Y(n3) );

endmodule

module SNPS_CLOCK_GATE_HIGH_try_top ( CLK, EN, ENCLK, TE );

input CLK, EN, TE;

output ENCLK;

PREICG_*CELL_TYPE* latch ( .CK(CLK), .E(EN), .SE(TE), .ECK(ENCLK) );

endmodule

5、ICG模块说明

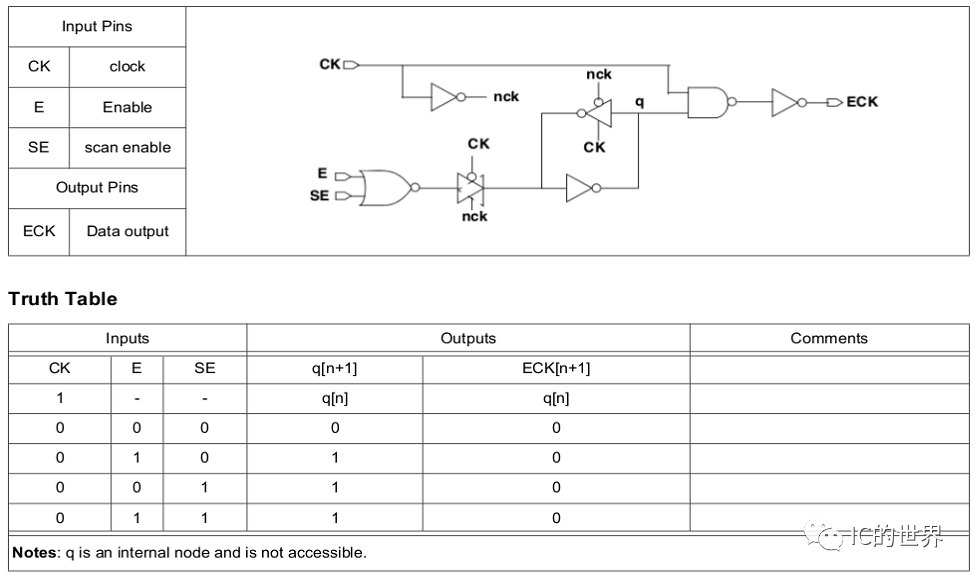

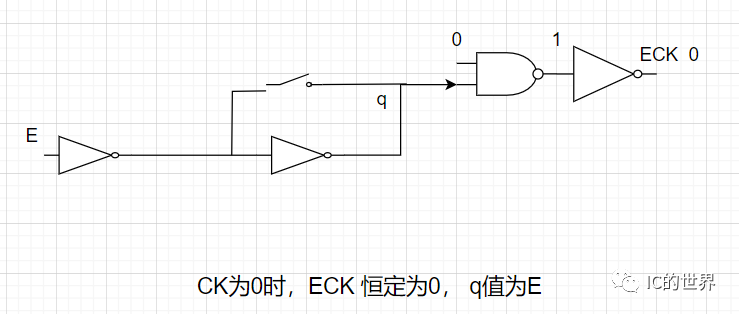

ICG(integrated latch clock gate)就是一个gating时钟的模块,通过使能信号能够关闭时钟。常用场景:低功耗状态下,关闭部分时钟源;无毛刺时钟动态切换等。 如图所示为一款ICG电路结构图,输入时钟为CK,输出时钟为ECK,E为使能信号,E为0表示关闭时钟,ECK输出为0。

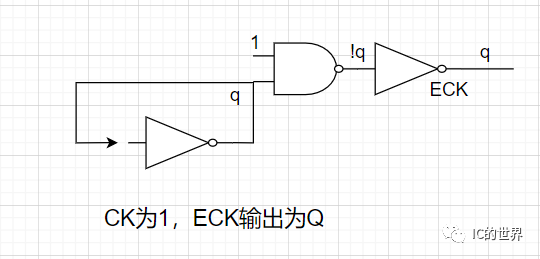

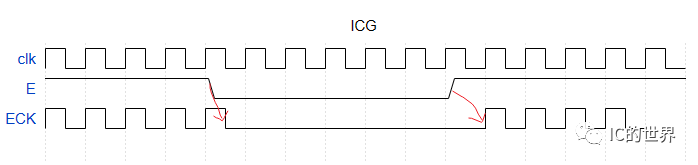

结合波形图和电路结构图,可以看到: 当CK为0时,ECK 恒定为0, q值为E:如果E为1,则q为1,如果E为0,则q为0。 当CK为1时,ECK 恒定为q(n),即对应的上一次CK为0时,锁存的E值。 因此最终的效果就是,只要E配置成了0,那么ECK会在CK的下降沿跳变成0,随后只要E保持为0,那么ECK一直为0。 当E从0跳变成1时,ECK会在CK的下一个上升沿跳变成1.

NOTE: 建议先将E输入信号同步到CK时钟域,这样E的跳变会发生在CK上升沿附近,因此在CK处于低电平时,E已稳定,有足够的时间驱动q值,使q达到标准电压阈值,而不是介于0/1之间的电压,从而保证了ECK的驱动能力。

编辑:黄飞

-

AD9514: 1.6 GHz Clock Distribution IC, Dividers, Delay Adjust, Three Output Data Sheet2021-01-28 415

-

AD9511: 1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Five Outputs Data Sheet2021-01-28 420

-

浅谈IC设计中逻辑综合2013-05-16 0

-

verilog 循环以及@(clock)的综合2015-02-03 0

-

低功耗设计基础:Clock Gating2023-06-27 1166

-

AND GATE的clock gating check简析2023-06-29 1855

-

Clock Gating的特点、原理和初步实现2023-07-17 2645

-

ASIC的clock gating在FPGA里面实现是什么结果呢?2023-08-25 686

-

clock-gating的综合实现2023-09-04 1255

-

浅析clock gating模块电路结构2023-09-11 1148

-

什么是Clock Gating技术?Clock Gating在SoC设计中的重要性2023-10-07 1549

-

SOC设计中Clock Gating的基本原理与应用讲解2024-04-28 67

全部0条评论

快来发表一下你的评论吧 !