PCIe总线的定义、组成和分层结构

接口/总线/驱动

描述

1、PCI-E总线定义

PCI-E(PCI-Express)是一种通用的总线规格,它由Intel所提倡和推广,其最终的设计目的是为了取代现有电脑系统内部的总线传输接口,这不只包括显示接口,还囊括了CPU、PCI、HDD、Network等多种应用接口。

PCIe总线与PCI最大的区别在工作原理上,PCIe是采用点到点的串行方式进行传输的,被称为“串行PCI”,由于采用了串行方式传输使得其工作频率可以达到2.5Ghz,大大增加了传输速率,同时采用全双工的通信方式,使得其传输速度提高了一倍,每一个PCIe总线设备与外部通信时有四根数据总线,分别有两个RX和TX,两根用于发送,两根由于接收。

当前的Intel平台CPU每颗最大支持40个通道(Lane),但是对于现在比较主流的GPU服务器需要插入多张高兴能显卡,每颗CPU提供x40个通道就显得不够用了。另外,传统存储控制器之间需要做各种数据交换和同步,一般也是用PCI-E,这又增加了对通道数量的消耗。对于一般的高端服务器,普遍都是双路、四路配置,双路下提供x80通道,理论上可连接10个x8的PCI-E设备,去掉一些用于管理、内部嵌入式PCI-E设备的通道占用之后,连接8个设备不在话下,可以覆盖几乎所有应用场景。

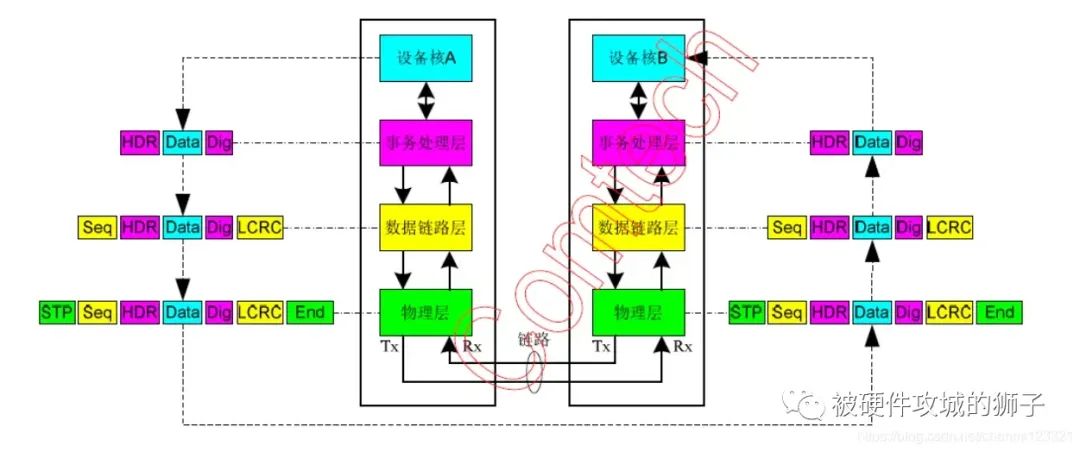

2、PCI-E的组成和分层结构

与大多数总线一样,PCIe总线也包括电气属性和协议组成两部分。PCIe 规范对于设备的设计采用分层的结构,有事务层、数据链路层和物理层组成,各层有都分为发送和接收两功能块。在发送端,应用程序(设备核A)在事务层形成事务层包(TLP——Transaction Layer Package),储存在发送缓冲器里,等待推向下层。在数据链路层,在TLP 包上再串接一些附加信息,这些信息是对方接收TLP 包时进行错误检查要用到的,形成数据链路层包(DLLP——Data Link Layer Package);在物理层,对DLLP 包进行编码,占用链路中的可用通道,从发送器发送出去。在接收端,实际上是发送端的“逆”过程。如果说发送端是在不断组包,那么接收端就是不断的拆包,最后提取出有用的数据信息供B设备的应用程序使用。

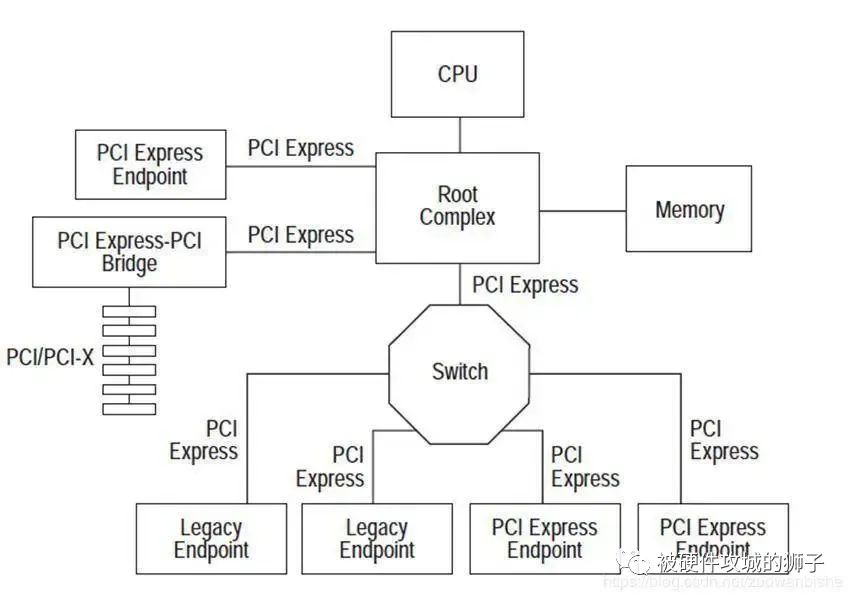

3、PCI-E总线架构图

PCIE体系架构一般包含根组件RC(rootcomplex),交换器switch,终端设备EP(endpoint)等类型的PCIE设备组成。RC在总线架构中只有一个,用于处理器和内存子系统与I/O设备之间的连接,而switch的功能通常是以软件形式提供的,它包括两个或更多的逻辑PCI到PCI的连接桥(PCI-PCI Bridge),以保持与现有PCI兼容,具体功能类似现在的网络交换机。

RC(Root Complex)

RC在功能上和Switch几乎一样,都是用于将一个PCIE接口拓展成多个PCIE接口,区别是RC集成在芯片内部,并且还会连接内存,类似PCI总线的根桥;

EP(Endpoint)

EP就是终端设备,没有转发数据的功能;

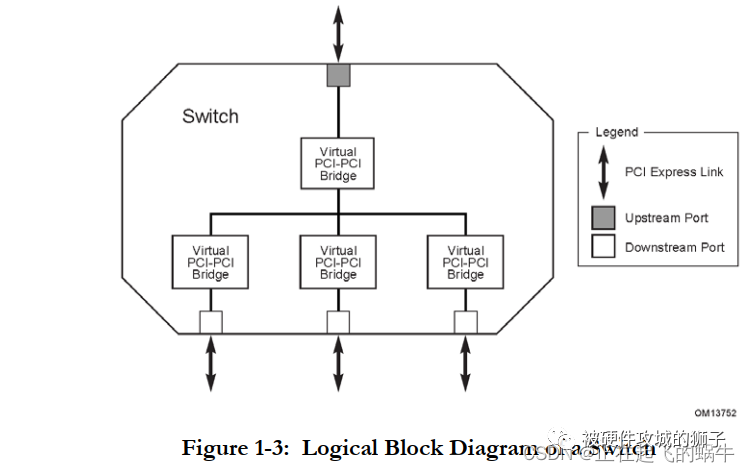

Switch

(1)Switch用于拓展PCIE接口。PCIE是串行接口,所以一个PCIE接口只能接一个PCIE设备,想要多接几个PCIE设备就需要用到Switch设备,起到数据转发的作用;

(2)Switch的内部结构可以看做由PCI桥组成;

(3)在Switch中,每个端口对应的PCIE设备号是写死的;

(4)Switch设备会记录下游PCIE端口连接设备分配到的PCIE地址,在接收到TLP包时,通过比较目的地址和下游设备的地址,来决定是否转发以及转发到哪个PCIE端口。

审核编辑:汤梓红

-

PCIE总线的FPGA设计方法2015-10-30 0

-

pcie总线基础知识 精选资料推荐2021-07-29 0

-

PCIe总线和PCI总线有哪些不同之处呢2021-10-26 0

-

单片机定义用途组成结构2021-11-17 0

-

CCIX 1.1设备必须支持PCIe 5.0 PHY或CCIX EDR PHY这两种物理层吗2022-08-16 0

-

基于FPGA的PCIE总线扩展卡的设计2010-10-08 1911

-

PCIE总线基本资料2012-05-10 1261

-

软件定义内容网络中基于分层的缓存管理2017-01-07 641

-

PCIE总线的多DSP系统接口设计2017-10-31 911

-

pcie接口定义及知识解析2017-12-12 154916

-

一个简化的PCIe总线体系结构2018-04-21 5303

-

PCIe链路端到端的数据传递 PCLe总线的层次结构2020-11-21 3660

-

PCI Express总线架构和总线层次结构浅析2020-11-25 3555

-

PCIe引脚定义和PCIe协议层介绍2023-09-26 7800

全部0条评论

快来发表一下你的评论吧 !