IC设计:一种简单超时机制

电子说

描述

1.超时判断机制

在设计中,为了增加异常处理能力,保证设备的正常运行,常常需要进行超时判断。

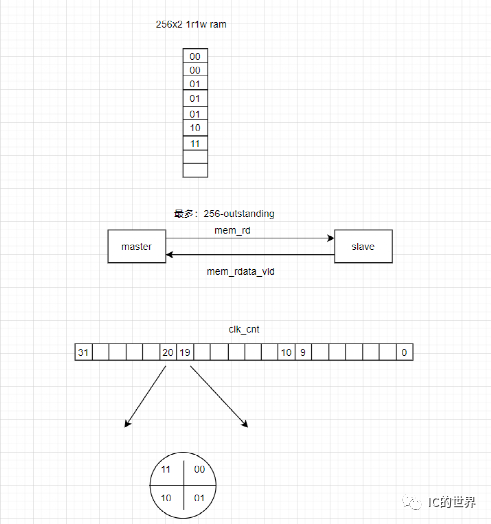

如下图,当master发起mem读请求后,收到读返回数据时,进行超时判断,如果超时,则数据丢弃,如果没有超时,则数据正常接收。

2.超时机制实现

如果在数据发送过程中,发送者向接收者发送数据,通常需要接收者通知发送者自身是否可以接收数据

采用一个公共的32bit clk_cnt作为时间基准,根据不同的超时精度,采用32bit中的连续2bit,1GHz时钟,每个周期1n,例如采用clk_cnt[20:19],可以记录2^21ns级别的精度,即2ms级别的时间精度。

本文中master能够发起256个outstanding(未完成)请求,req_id[7:0]从0到255,且工作时钟clk为1Ghz,发起的mem读请求,且在1us后都没有收到数据,则认为超时。

步骤1:master发起mem_rd请求时,以req_id作为地址,将clk_cnt[20:19]作为data,写入256x2 1r1w_ram中。

步骤2:当master收到读返回数据时,以req_id作为地址从ram中读取data,记作clk_cnt_record

步骤3:提取当前时刻clk_cnt[20:19],记录为clk_cnt_now,如果clk_cnt_now-clk_cnt_record 的绝对值大于1,则表示超时。

案例:

clk_cnt_record 为 10,clk_cnt_now为00,则表示超时。

clk_cnt_record 为 10,clk_cnt_now为11,则认为不超时。

3.特点说明

优点:此类设计比较简单,所需的逻辑资源较少,并且可以调节超时时间精度。

缺点:

如果超时时间过长,已经从clk_cnt_record翻转了一圈再返回时,则无法判断是否为超时。即clk_cnt_record(10)-->11-->00-->01-->10-->11(clk_cnt_now),实际已超时,但是判断为没有超时。

没有读返回数据时,无法判断是否超时。

审核编辑:汤梓红

-

请问HAL库的超时机制可以修改吗?2019-01-30 0

-

Linux串口通信的超时机制2019-07-05 0

-

VxWorks共享看门狗定时机制该怎么设计?2019-09-03 0

-

请问板子的延迟函数是一种什么机制?2019-10-15 0

-

怎样去设计一种同步补偿机制(CDCO算法)?2021-05-17 0

-

实现嵌入式软件超时的方法2021-12-24 0

-

分享一个非常简单的内存数据库2022-02-11 0

-

TCP运输层协议的超时重传原理实现2022-04-14 0

-

是否有一种机制可以从虚拟功能处理程序进行屏幕转换呢?2022-12-13 0

-

一种简单的报错设计,分享2023-05-20 0

-

基于公平心跳超时容错机制2018-01-02 492

-

嵌入式软件定时/超时机制程序设计2021-11-03 259

-

IC设计知识点:一种简单超时机制2022-09-21 663

-

如何设计STM32嵌入式程序的超时机制?2023-06-15 920

-

影响报文超时上报的机制有哪些2023-08-07 925

全部0条评论

快来发表一下你的评论吧 !