基于SILICON C8051的JTAG是如何进行烧录的?

电子说

描述

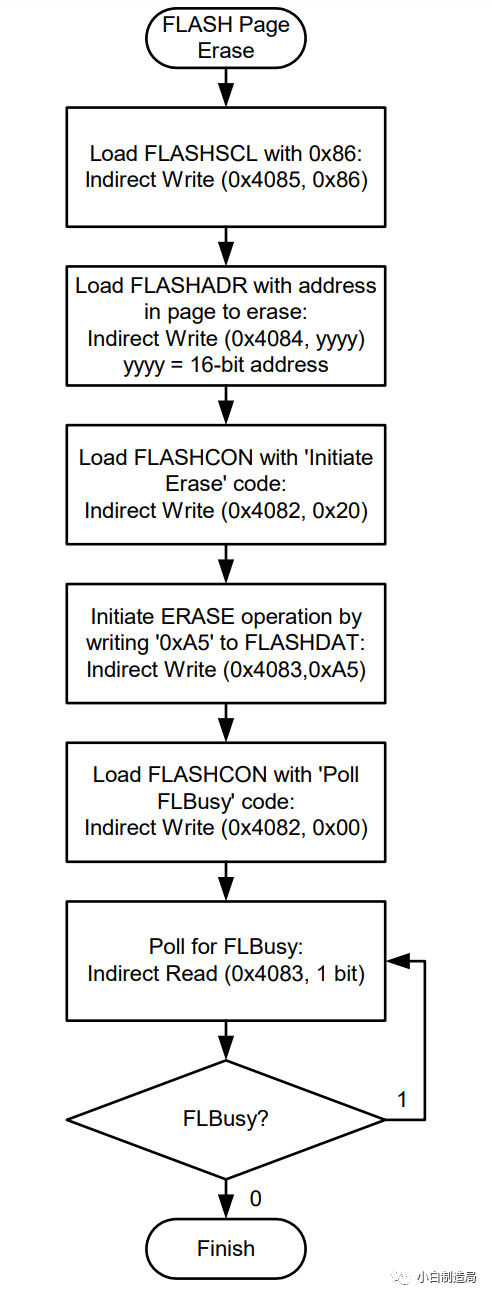

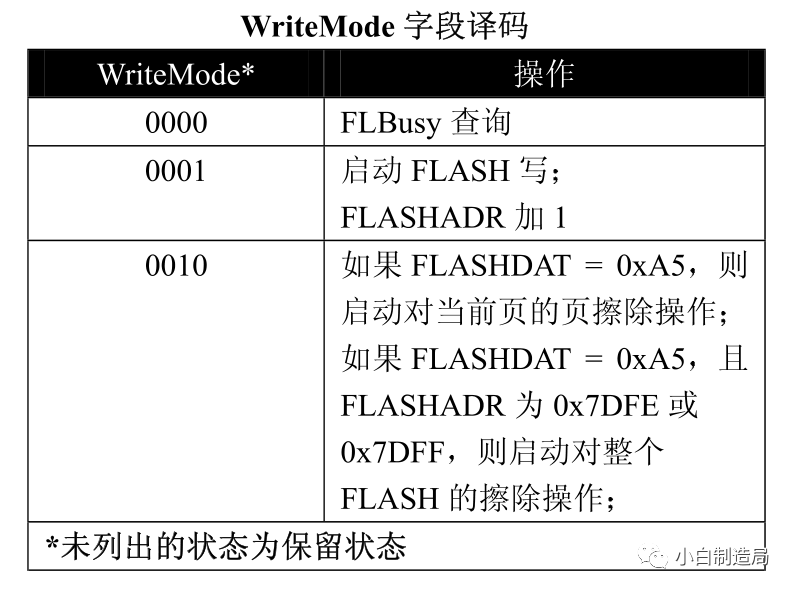

FLASH的页擦除

FLASH由一系列的页组成,每页512字节。FLASHCON寄存器设置为0x20,FLASHDAT寄存器设置为0xA5,FLASHADR寄存器可以设置为要擦除的页内的任何一个地址。

如果FLASHADR被设置为锁定字节地址中的任何一个(0x7DFE或0x7DFF),则该擦除操作将擦除整个FLASH存储器,位于0x7E00和0x7FFF之间的保留区除外。

与读和写操作不同,在擦除操作完成后FLASHADR并不自动加1。

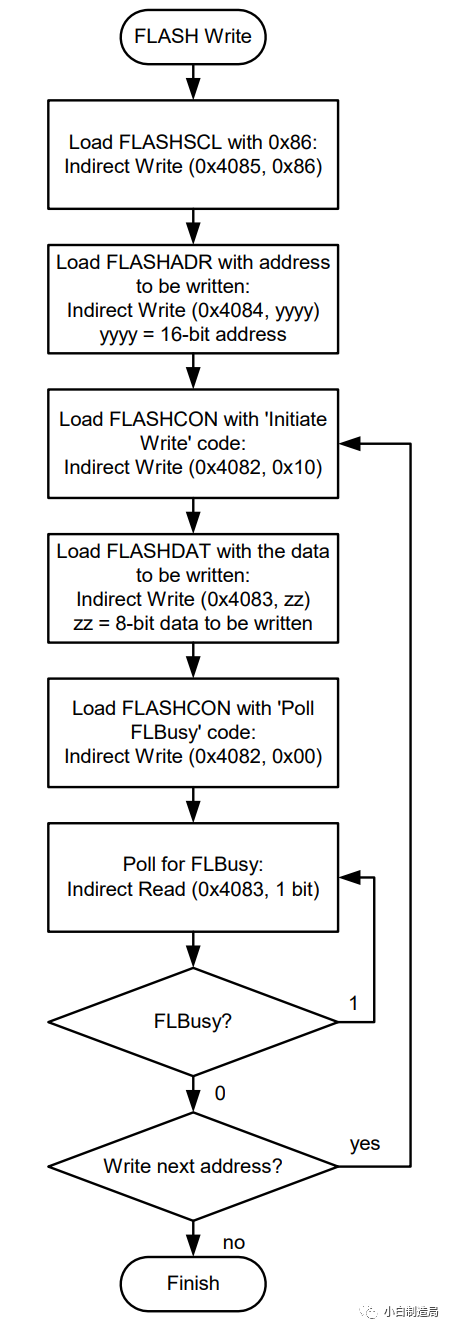

FLASH的字节写

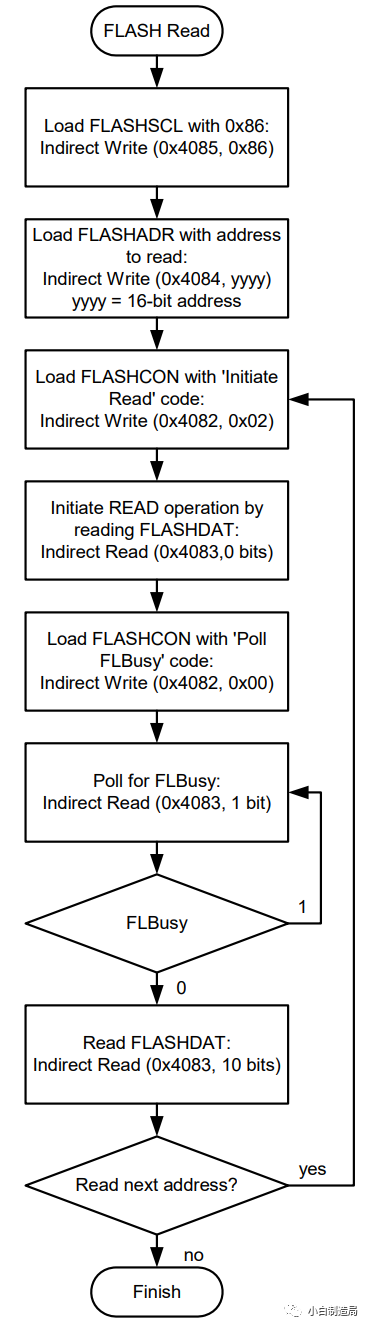

FLASH的字节读

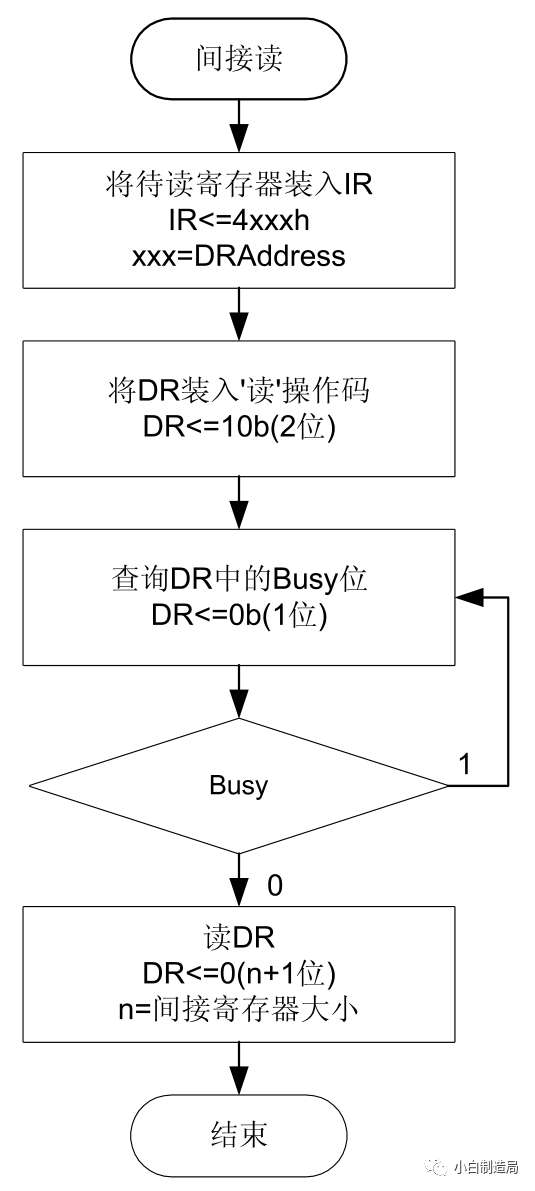

间接读

读操作启动一次从由DRAdress选择的寄存器中读取数据的过程。该过程可以通过向间接寄存器移入两位来启动。在读操作被启动后,可以通过查询Busy位来确定操作何时完成和何时可以读取数据。

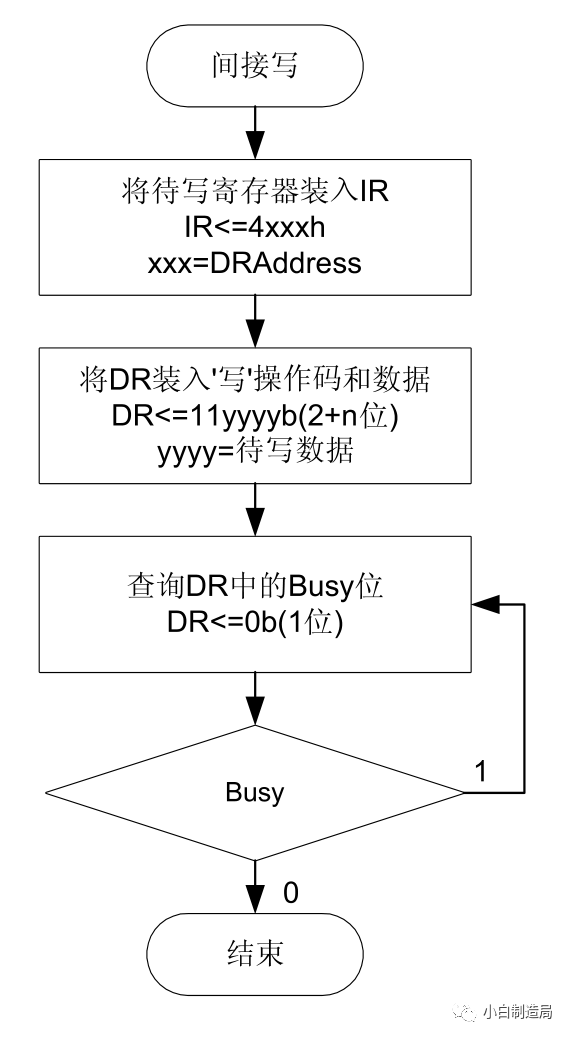

间接写

写操作启动一次向由DRAddress选择的寄存器内写数据的过程。可以写长度不大于18位的任意长度的寄存器。如果待写寄存器的长度小于18位,写数据(WriteData)应左对齐(MSB占据位17)。在启动一个写操作之后,应查询“Busy”位来确定该操作何时完成。

FLASH寄存器

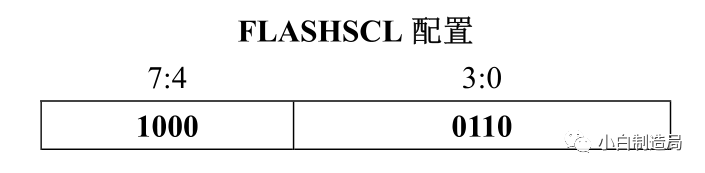

FLASHSCL

FLASHSCL是一个8位寄存器,用它设置FLASH操作时序所需要的预分频值。当使用内部的2MHz系统时钟时,该寄存器应配置如下:

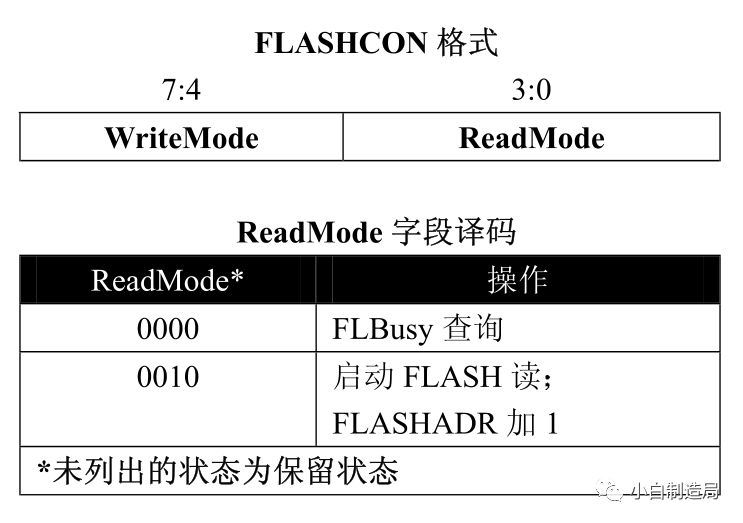

FLASHCON

FLASHCON是一个8位寄存器,它控制FLASH逻辑如何响应对FLASHDAT寄存器的读和写操作。FLASHCON寄存器包含一个读方式设置和一个写方式设置。

FLASHDAT

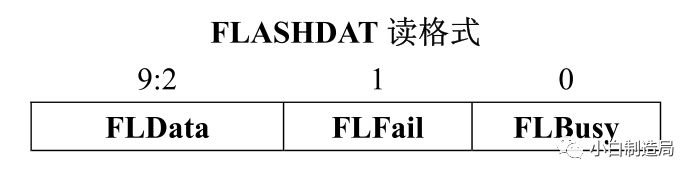

FLASHDAT是一个10位的寄存器,它包含8位数据,一个FLFail位和一个FLBusy位,如图所示:

写FLASHDAT只需要8位,因为最后一个被锁存的位处于MSB位置。

读FLASHDAT只需要11个DR_SHIFT周期(8个用于FLData,一个用于FLFail,一个用于FLBusy)。

查询FLBusy至少需要2个DR_SHIFT周期,一个用于FLBusy,一个用于Busy。

FLASHADR

FLASHADR是一个16位寄存器,它包含待读或待写的FLASH字节的地址。

注意点

在对FLASH进行烧录之前,需要对器件复位并禁止看门狗。否则,看门狗定时器可能在FLASH操作期间启动系统复位,导致预想不到的后果!

-

C8051单片机,Silicon labs 产品2011-11-19 0

-

C8051也可以实现TCP/IP2012-04-15 0

-

C8051的C语言的彻底应用.pdf2012-05-19 0

-

C8051的C语言的彻底应用2012-10-07 0

-

《C8051的C语言的彻底应用》书籍2012-12-08 0

-

求c8051单片机实践的小实验的视频2013-01-29 0

-

哪位有C8051学习资料,望赐教2013-06-14 0

-

LY c8051学习资料,电机测速程序2014-02-19 0

-

用新华龙的c8051时为什么使用printf函数的时候不行?2019-06-20 0

-

siliconc8051f Silicon C8051F编程器使用出错怎么解决2021-12-08 0

-

C8051与SRAM的高速接口2011-07-18 895

-

C8051的C语言的彻底应用2016-08-31 1184

全部0条评论

快来发表一下你的评论吧 !