混合键合推动异构集成发展

电子说

描述

来源:《半导体芯科技》杂志

随着人工智能(AI)、无人驾驶、增强现实/虚拟现实(AR/VR)和5G等前沿应用的快速发展,半导体制造商需要在不增加生产成本的前提下开发出高带宽、高性能、低功耗设备。随着传统的二维硅片微缩技术达到其成本极限,半导体行业正转向异构集成技术。异构集成是指不同特征尺寸和材质的多种组件或晶片的制造、组装和封装,使其集成于单个器件或封装之中,以提高新一代半导体器件的性能。

经过集成式晶片到晶圆键合后附在晶圆上的独立晶片

晶圆到晶圆(W2W)混合键合涉及不同生产线的晶圆堆叠和电连接处理,是异构集成的核心工艺,在CMOS图像传感器以及各类内存以及逻辑技术应用中表现出色。然而,在组件或晶片尺寸不相同的情况下,晶片到晶圆(D2W)混合键合更适用于异构集成。凭借新型D2W键合解决方案和市场领先的W2W混合键合解决方案,加之异构集成能力中心(Heterogeneous Integration Competence Center™)带来的丰富行业合作经验,EV集团(EVG)为D2W键合应用提供有力支持。

01融熔和混合键合技术

融熔或直接晶圆键合可以通过每个晶圆表面上的介电层实现永久连接,用于工程基板或层转移,例如背照式CMOS图像传感器。

混合键合扩展了融熔键合,在键合界面中嵌入金属焊盘,允许晶圆的面对面(face-to-face)连接。混合键合的主要应用是先进的三维(3D)器件堆叠。

融熔或直接晶圆键合允许介电层和更精确活化的官能团悬垂,在氢桥键(hydrogen bridge bond)的帮助下在晶圆之间桥接。该预粘合步骤在室温和大气条件下进行。只有在随后的退火步骤中,低能氢桥键才会变成共价键。

融熔键合传统上用于工程基板,最近用于使用全面积电介质的堆叠晶圆。由于在环境条件下进行预键合,小于100nm的高精度对准允许3D集成场景使用晶圆到晶圆融熔键合。此外,铜焊盘可以与介电层并行加工,允许在环境温度下预粘合介电层,而电接触可以在退火期间通过金属扩散键合实现。这种特殊情况称为混合键合。混合键合的主要应用包括CMOS图像传感器、存储器以及3D片上系统(SoC)。

02D2W融熔和混合键合

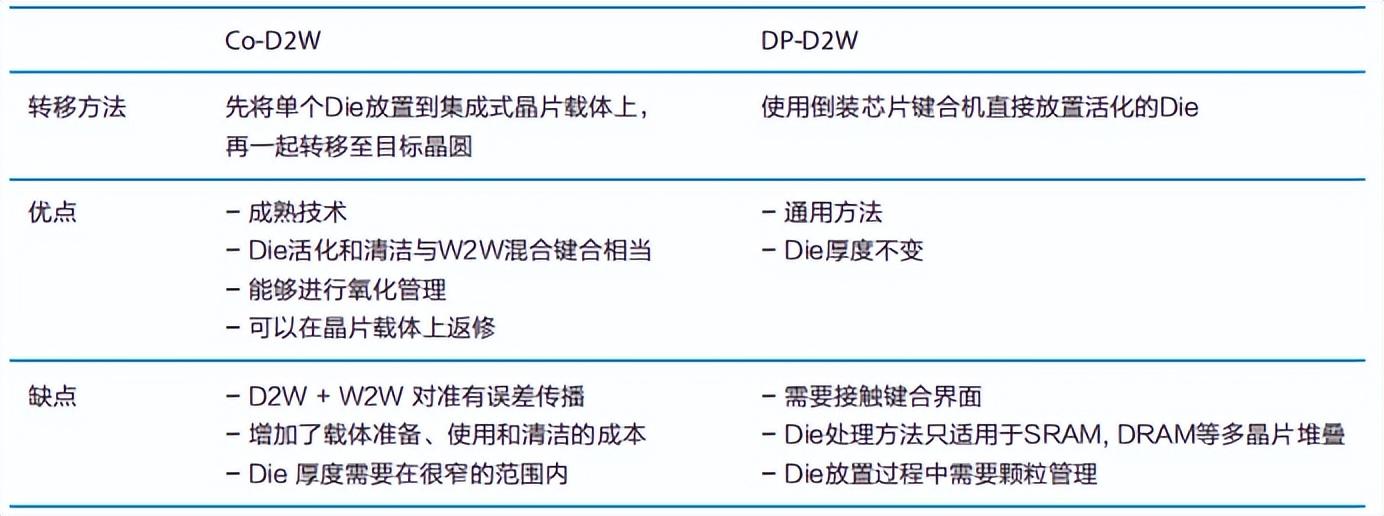

作为异构集成的核心工艺,W2W混合键合,已经在CMOS图像传感器和各种存储器、逻辑技术方面获得良好的成功记录。然而,由于许多小芯片(chiplet)的尺寸不一定相同,因此D2W混合键合方法可能更实用。异构集成有几种不同的D2W键合方法,包括集成式D2W(Collective D2W,Co-D2W)和直接放置D2W(Direct Placement,DP-D2W)键合,每种方法都有各自的优点和缺点,如表1所示。

△表1:Co-D2W和DP-D2W两种键合方法对比

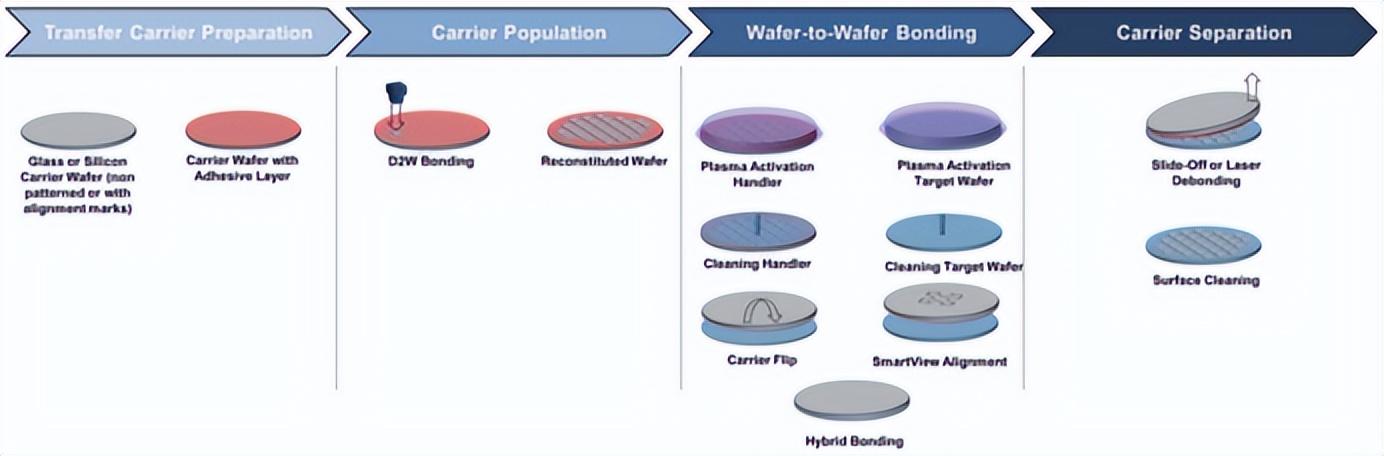

03Co-D2W键合

在过去几年中,Co-D2W键合已经在硅光子学等应用中有限批量生产中实施。在Co-D2W键合中,是在单个工艺步骤中将多个晶片一次转移到最终晶圆上。Co-D2W键合工艺的制造流程如图1所示,包括四个主要部分:晶片载体(晶圆)制备、载体填充(在载体上放置晶片)、晶圆键合(临时和永久)和载体分离。

△图1:Co-D2W键合工艺的制造流程。

04DP-D2W键合

用于异构集成的另一种混合D2W键合方法是DP-D2W键合,其中使用拾放式倒装芯片键合机将晶片逐一单独键合到目标晶圆上。图2显示了DP-D2W键合工艺的制造流程,其成本包括三个主要部分:载体填充(在载体上放置晶片,为清洁做准备)、晶片清洁和活化、直接贴装倒装芯片。

图2:DP-D2W键合工艺的制造流程。

目前有多种D2W键合技术和设备可供使用,可以根据应用和客户要求进行选择。在Co-D2W键合中,单个晶片放置于集成式晶片载体之上,再送至目标晶圆进行晶片转移,此时可使用W2W混合键合系统(如GEMINI FB)完成晶片与目标晶圆的键合。在DP-D2W键合中,则使用拾放式倒装晶片键合机将单个晶片逐一键合至目标晶圆上。等离子体活化和处理器芯片上的晶片表面清洁是在晶片和目标晶圆之间建立高产量键合和电界面的关键步骤。而这一步正是EVG® 320D2W活化系统发挥作用的重要舞台。

05利用EVG的异构集成能力中心™加速技术开发

为了应对异构集成技术挑战,EVG建立了异构集成能力中心™(HICC)。该中心致力于帮助客户充分利用EVG工艺解决方案和专业知识,通过系统集成和封装技术的进步,加速开发创新产品和应用。

2022年7月,EVG宣布在D2W熔融与混合键合领域取得重大技术突破。EVG在单次转移过程中使用GEMINI® FB自动混合键合系统,在完整3D SoC中对不同尺寸芯片实施无空洞键合,良率达到100%。直至今天,此类键合仍是D2W键合领域面临的关键挑战,也是降低异构集成成本的主要障碍。EVG的异构集成技术中心(HICC ™)取得了这一重大技术突破。

混合键合的接口呈固态,采用嵌入式金属焊盘,以实现晶圆和芯片的直接电气连接,因此D2W混合键合需要达到与前端半导体制造工艺类似的清洁度标准和制造公差。在这一趋势的推动下,高精度计量在控制混合键合对准和工艺良率方面开始发挥更为重要的核心作用,反过来又推动了D2W键合和计量工艺集成为统一生产线。

GEMINI® FB自动化Co-D2W键合系统

此外,目前数种不同的D2W混合键合工艺流程正在接受评估,每种工艺流程都有其独特优势和要求。自两年前成立以来,HICC发挥了重要作用,帮助客户和合作伙伴开发及优化D2W混合键合工艺,满足给定器件设计和应用的独特需求,并在开发中综合考虑多种因素,如芯片尺寸、芯片厚度、总堆叠高度,以及触点设计和密度等接口考虑因素。HICC还配备了先进的洁净室,其洁净度标准与多家领先半导体工厂相当,使EVG有能力满足D2W和W2W混合键合工艺开发的严格要求。

EVG业务发展总监托马斯·乌尔曼(Thomas Uhrmann)博士表示:“混合键合需要完全不同于标准封装工艺的制造技术,它更接近前端制造——特别是在清洁度、颗粒控制、对准和计量精度方面。我们在W2W混合键合领域处于市场领先地位。在此基础上,我们将继续扩展D2W混合键合解决方案,优化设备,为重要的上下游工艺提供支持,包括等离子活化和清洁技术,以加快部署和完善D2W混合键合技术。数年之前,EVG的GEMINI FB技术已配置用于D2W集成流程,满足D2W键合需求。EVG® 320 D2W晶片准备和活化系统则用于D2W键合的直接贴装,提供与D2W键合机的直接接口。EVG® 40 NT2套刻计量系统使用AI、前馈和反馈回路进一步提高混合键合良率。在这些技术之外,EVG又推出完整的端到端混合键合解决方案,以加速部署3D/异构集成。”

参考文献

1.EV集团实现芯片到晶圆熔融和混合键合技术突破多芯片3D片上系统的芯片转移良率达到100%.

2.EVG's die-to-wafer fusion and hybrid bonding technologies - supporting collective die-to-wafer as well as direct die-to-wafer process flows.

3.EV集团(EVG)在中国国际半导体展上展示新型晶片到晶圆混合键合活化解决方案,旨在加快3D-IC/异构集成技术的发展

审核编辑 黄宇

-

集成电源是电源技术发展的必由之路2011-03-09 0

-

iPhone8推动PCB发展2017-02-27 0

-

先进封装技术的发展趋势2018-11-23 0

-

异构集成的三个层次解析2020-07-07 0

-

异构混合并行编程模型及其研究综述2021-05-13 614

-

混合键合将异构集成提升到新的水平2023-07-03 1766

-

异构集成推动面板制程设备(驱动器)的改变2023-07-10 288

-

3D异构集成与 COTS (商用现成品)小芯片的发展问题2023-11-27 294

-

华芯邦科技开创异构集成新纪元,Chiplet异构集成技术衍生HIM异构集成模块赋能孔科微电子新赛道2024-01-18 284

全部0条评论

快来发表一下你的评论吧 !