谈谈LDO设计时的一些思考

电子说

描述

1. 模拟LDO

1.1 FVF BasedLDO

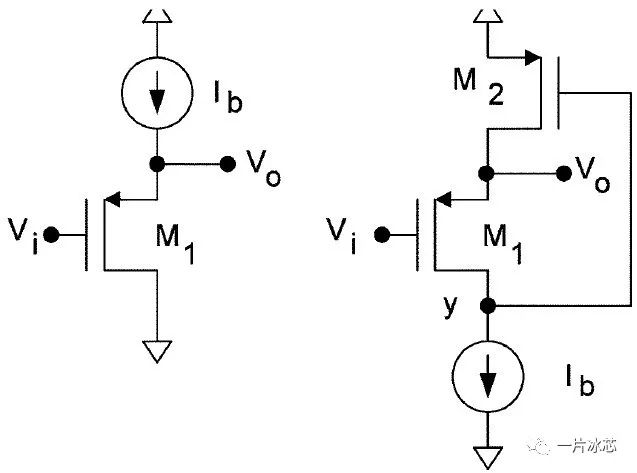

FVF全称为Flipped Voltage Follower是一种输出阻抗很低的新型源跟随器,其拥有更大的电流驱动能力,相对传统单管源跟随器输出阻抗减小了gm2ro1倍,如图1所示,其中gm2为M2管的跨倒,ro1为M1管的小信号电阻 ^[1-2]^ 。

(a)单管源极跟随器(b)FVF

Fig1. 单管源极跟随器及FVF源级跟随器

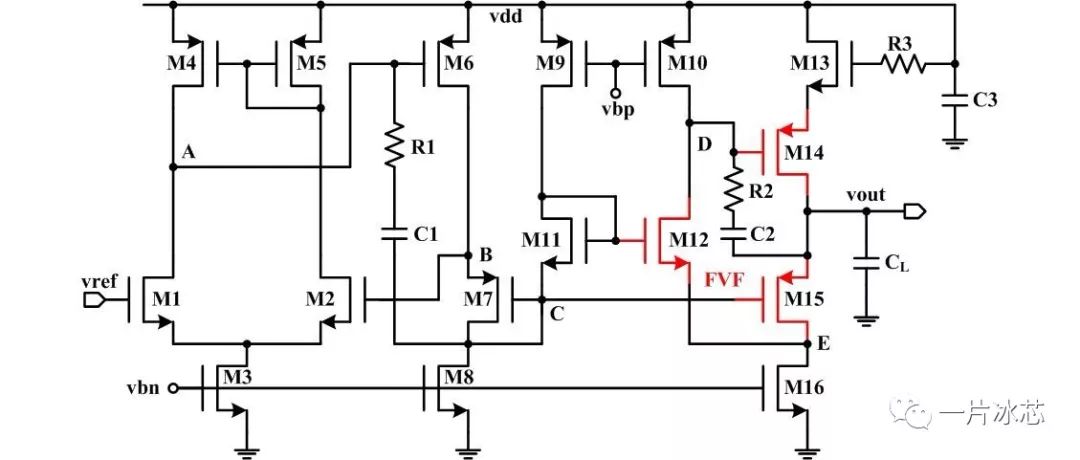

图1所示简单FVF结构无法提供较大的环路增益,这会导致较差的DC 特性,为了提高低频增益可以采用参考文献[3]的共源共栅FVF结构,图2是我在项目中设计的共源共栅FVF LDO。M12为FVF环路(M14、M15、M12)提供共源共栅级,提高了环路增益,代价是FVF环路包含了三个极点(图2中vout、D、E),因此需要采用密勒补偿来保证环路稳定性。

Fig2. 共源共栅FVF LDO

此外,图2中M13的引入是为了提高PSRR,M1和M2管的length取大可以减小输出级的噪声(一般噪声贡献较大的管子为运放的输入对管和电流偏置管),保证稳定的前提下CL尽量取大,因为大的CL在环路带宽不够时可以保证输出级有较好的负载瞬态跳变调节能力,同时可以提高高频PSRR。

1.2 高PSRR LDO

这边多说几句,芯片内部电源往往通过外部DC-DC提供,DC-DC内部通常会有几百kHz到几十MHz的时钟,并且可能会产生几mV到几十mV的电源纹波。在sub-6G FR1 5G通信中Channel Bandwidth高达100MHz,mm-Wave FR2 5G通信中Channel Bandwidth达到400MHz,因此从系统应用上讲MHz的PSRR也十分重要。

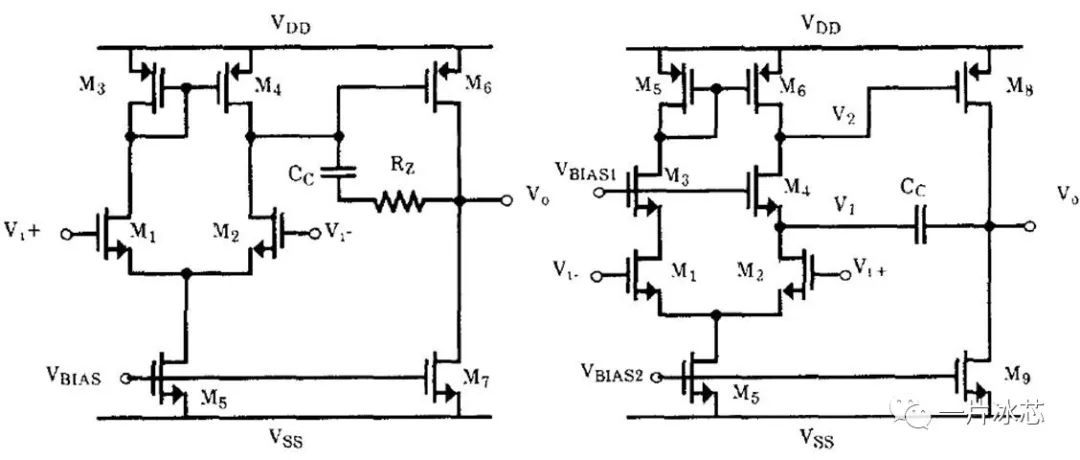

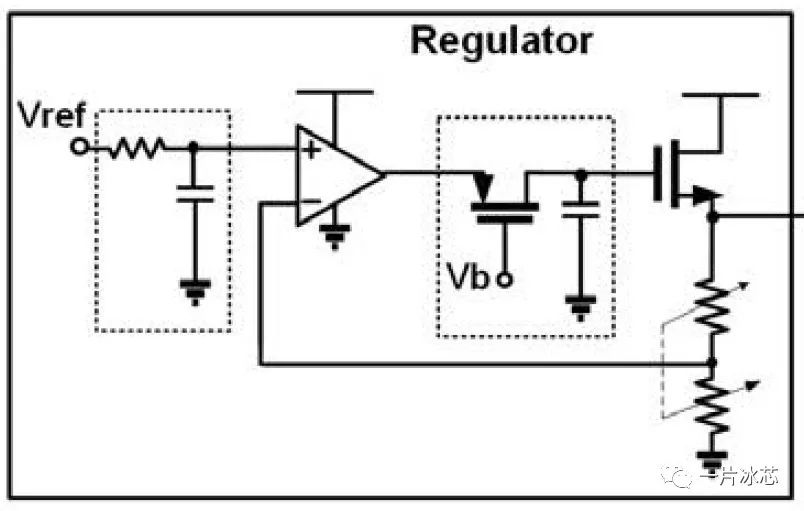

图3给出了传统LDO和高PSRR LDO原理图 ^[4]^ 。将密勒补偿电容接在M4管的源极以提高M8管高频PSRR(低频PSRR比较容易,通常会卡在高频处)。

(a)传统LDO (b)高PSRR LDO

Fig3. 传统LDO和高PSRR LDO

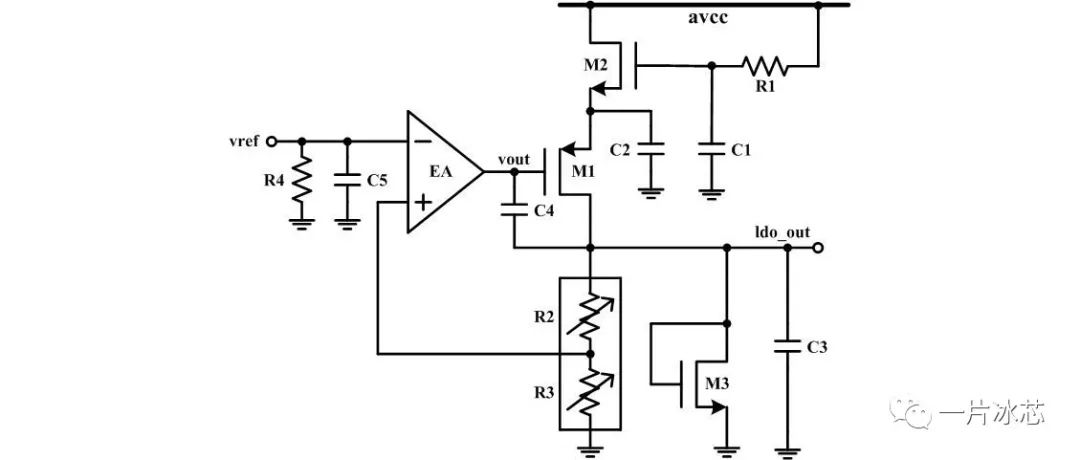

图4 LDO结构在之前的layout讲议中提到过,大电容C2的引入保证在GHz频率处仍有-20dB的PSRR,高频PSRR要优于图2的共源共栅FVF结构。

Fig4. 高PSRR LDO

电源到LDO输出端内阻越小,LDO越接近一个理想电压源,输出电压越稳定,将功率管由PMOS换成NMOS可将功率管输出阻抗由ro变为1/g m ,进一步提高PSRR^[5-6]^,如图5所示。此外,为了减小N管的Drop电压,功率管可采用Native管。

Fig5. 高PSRR的N管LDO

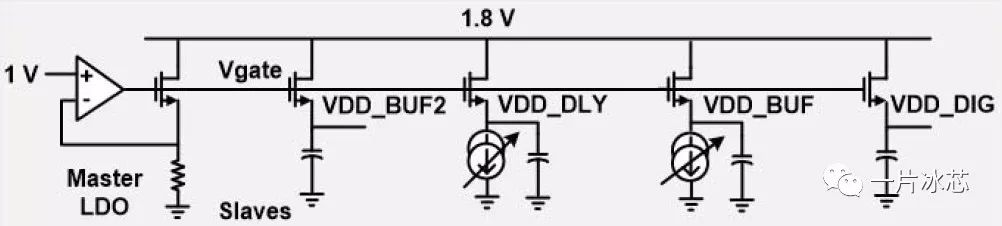

1.3 Replica LDO

基于NMOS LDO特性,Replica LDO更适用于数字负载,Replica LDO结构如图6所示。Replica LDO分为Master和Slave级,通常由一个Master产生Vgate电压,然后接到多个Slave级,通过合理设置电流比例及负载可以粗略复制Master的参考电压,如果负载能接受电压变化,这种结构问题不大。此外,这种结构输出级工作在开环状态且采用NMOS做功率管,负载突变时具有较小的undershoot和overshoot。

Fig6. Replica LDO

1.4 耐压结构LDO

之前项目需要一个3.3V转0.8V的LDO,但用的是22nm先进工艺,里面高压管最高只能耐1.98V的电压,拿到这个需求时,真是一万个头大,脑海里一堆问题,1.8V的device怎么抗3.3V的电压啊?基准电压、mux、buffer、LDO主体电路、triming电路通通需要耐压结构,没这方面的设计经验啊。

芯片面积有10mm*10mm,外部单3.3V电源,经LDO产生0.8V的电压做为内部的core电源而且是Capless结构。我们还联系过法国Dolphin公司(海豚集成)帮我们做,他们是可以做,但没有Capless结构的IP,让他们做需要20W美金(真黑)。价格没谈就只能硬着头皮自己做喽,期间查了很多资料,方案也修改了多次,万幸流片测试一把成了,因工作需要这里就不给大家透露具体细节了,基本思想就是叠管子耐高压,有这方面需求的可以私信我。

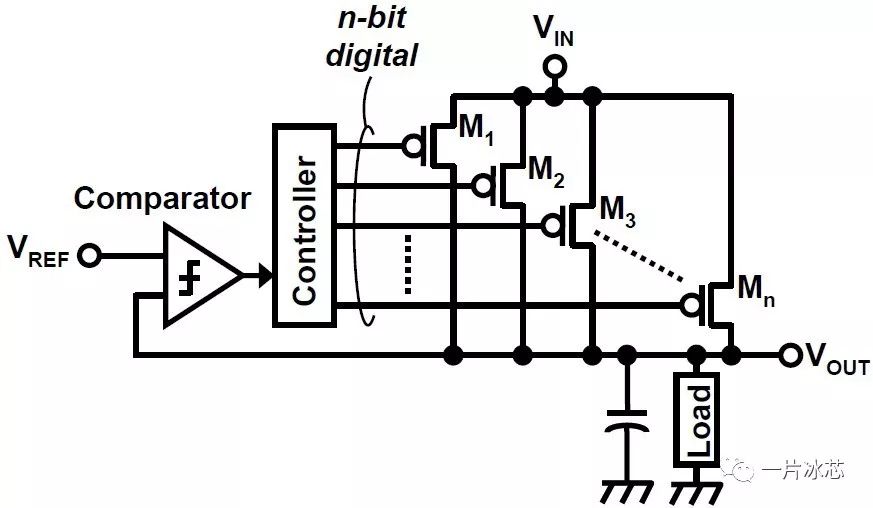

2. 数字LDO

数字LDO原理很简单,把模拟LDO功率管分割成许多功率开关,这些开关由移位寄存器控制,比较器每个时钟周期比较Vout和Vref电压并指示移位寄存器打开或关断一个功率开关,结构框图如图7所示。

Fig7. 数字LDO

数字LDO可以工作在比较低的电压下,而且方便工艺移植。由于有限的输出精度,在稳定时数字控制码会振荡,这就是所谓的有限周期振荡(Limit-Cycle Oscillation, LCO)。数字LDO环路包含了z域和s域,分析起来较复杂。

**3. **总结

①LDO的设计指标要看你的应用,如果是给数字电源供电,PSRR、noise、电源精度这些都不是特别重要,如果是给VCO供电,那就要小心了,建议PSRR在0100MHz小于-20dB@ 1MHz,noise在1MHz小于20nV/√Hz,LDO基准电压PSRR在0100MHz小于-30dB@ 1MHz,noise在1MHz小于10nV/√Hz。

②LDO参考电压一般需要加大的RC滤波,-3dB带宽要小于你的环路带宽。

③采用N管做为功率输出级可以提高PSRR并减小undershoot和overshoot。

④Replica LDO也挺常用的我就在pll中用过,而且PSRR、undershoot和overshoot确实好,输出电压变化也不是那么大。

-

大家来谈谈LDO吧2012-11-14 0

-

关于编程的一些问题?2014-06-03 0

-

什么是LDO噪声?LDO噪声是如何分类的?2019-08-01 0

-

一些常见的DC-DC、LDO输出设计原理图2020-04-07 0

-

关于车载信息娱乐系统软件设计的一些思考2021-05-11 0

-

分享一些RS-485设计技巧2021-05-19 0

-

关于MCU,给研发提供一些思考吧!2021-06-18 0

-

谈谈电容的一些基本应用及注意事项2021-11-10 0

-

介绍一些常用的LDO相关术语2021-11-12 0

-

谈谈对替换电容的一些看法2021-11-16 0

-

讲述LDO和DC-DC的一些差异2021-11-17 0

-

谈谈void指针的一些妙用2022-01-26 0

-

《 AI加速器架构设计与实现》+学习和一些思考2023-09-16 0

-

谈谈开关电源和LDO电源的一些原理2021-08-10 4732

全部0条评论

快来发表一下你的评论吧 !