在PDK中是如何定义Vth的呢?

电子说

描述

以N管为例(P管类似),当Vg逐渐升高,p衬底中的空穴被向下的电场赶离栅区留下负离子以镜像栅上的电荷。换句话说,就是形成了一个耗尽层。此时,由于没有载流子而无电流流动。

随着Vg进一步增大,界面电势足够高时,栅氧化层中形成载流子沟道,硅表面电子浓度恰好等于空穴浓度,器件处于临界导通状态,此时的Vg即为晶体管的阈值电压(Vth)。那么在PDK中是如何定义Vth的呢?本期以某SOI工艺为例,带大家了解一下PDK中的Vth。

**1 **定义

直观说,Vth就是MOS的开启电压,我们知道即使MOS管的Vgs为零,源漏之间也存在漏电流(Ids),这样看来MOS管似乎一直是“开启”的,那么我们该如何定义晶体管的开启电压呢?

以某SOI工艺为例,Vth有两种定义:一种是让晶体管工作在线性区来测量Vth(VtLin),另一种是让晶体管工作在饱和区来测量Vth(VtSat)。两种方法都需要规定一个Iconstant电流和Vds电压,该电流和电压通常由Foundry提供且可能跟器件类型相关。

1.1 VtLin

VtLin方法如下:

给定Vds=50mV, Iconstantn=300nA, Iconstantp=70nA, 宽长比为2u/0.3u(或其他尺寸),DC扫描Vgs电压,当Idsn/p=Iconstantn/p * (2/0.3)时,此时的Vgs电压即为n/p管的阈值电压。

1.2 VtSat

VtSat方法如下:

给定Vds=1.8V, Iconstantn=300nA, Iconstantp=70nA, 宽长比为2u/0.3u(或其他尺寸),DC扫描Vgs电压,当Idsn/p=Iconstantn/p * (2/0.3)时,此时的Vgs电压即为n/p管的阈值电压。

**2 **仿真及对比

2.1 仿真

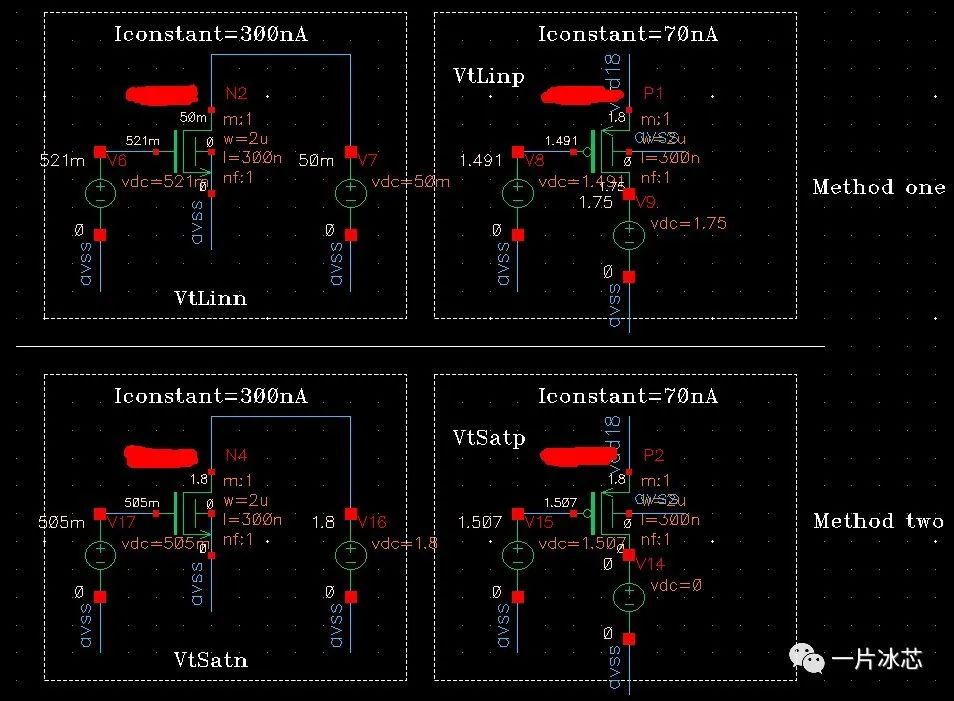

按某SOI PDK对Vt的定义,可以查到Icostantn=300nA,Iconstantp=70nA,Vds=50mV,Vdd=1.8V,可搭建图1所示testbench(不同于传统Bulk工艺,SOI工艺PMOS背栅电位可接地)来验证仿真结果与PDK是否一致。

Fig1. Vth仿真testbench

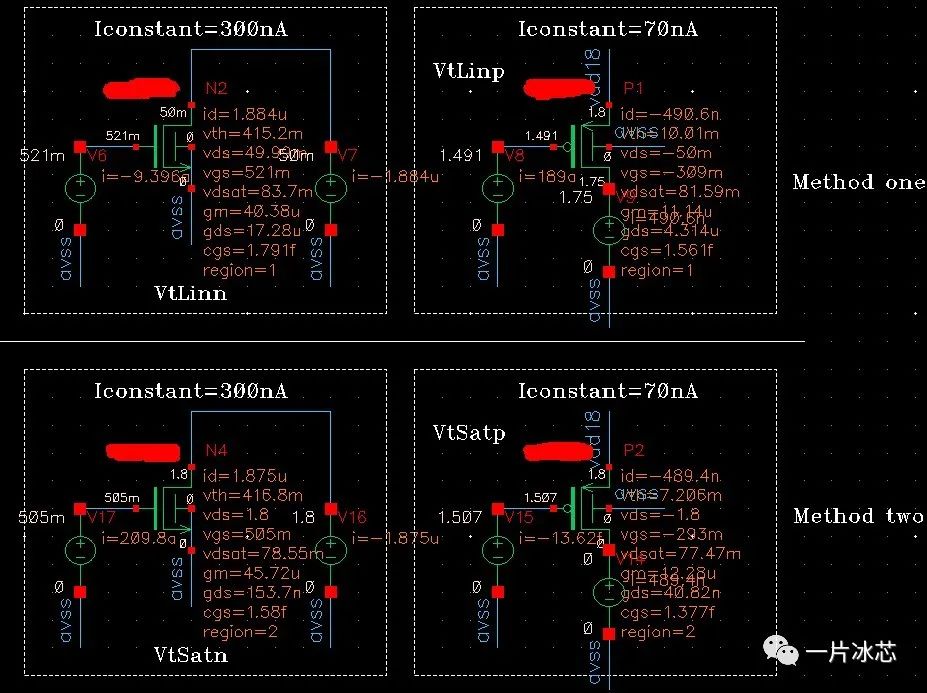

打出图1静态电流,如图2所示。

Fig2. 图1静态电流

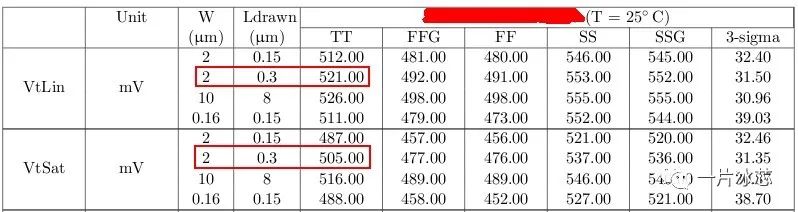

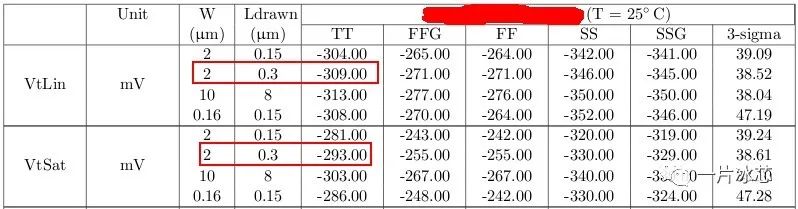

2.2 对比

图2两种方法仿真得到的N管id(即ids)约为2uA(计算结果为:300nA * 2/0.3=2uA),P管得到的id约为0.5uA(计算结果为:70nA * 2/0.3=467nA),在电流相近时(仿真结果与计算结果),此时图2中的Vgs电压与PDK给的VtLin和VtSat一致,如图3所示。

(a) NMOS Vth

(a) PMOS Vth

Fig3. PDK给出的Vth(VtLin和VtSat)

由此可见,仿真出的临界开启电压(即Vtyh)与PDK给的一致!

-

理解MOSFET的VTH:栅极感应电压尖峰,会导致直通损坏吗?2016-11-08 0

-

电源系统低温不开机,你遇到过吗:理解VTH温度系数2016-11-14 0

-

关于PDK里面platform文件夹中platform.h里面的函数问题!2018-06-21 0

-

有专门用于C6655/57的PDK吗?2018-06-21 0

-

请问sy***ios工程能否用PDK库?2018-07-25 0

-

PDK下的例程pdk_C6678_1_0_0_16\packages\ti\drv\exampleProjects每次编译都有错2018-12-25 0

-

ads1281_EVM_PDK使用找不到板子2019-02-27 0

-

PDK 验证软件PQLab的优势和技术指标2020-07-01 0

-

TSMC.18 BCD PDK是什么?有何作用?2021-06-22 0

-

TSMC130_PDK是什么?如何去安装?2021-06-25 0

-

在STM32中如何去实现多个串口重定义printf输出呢2021-12-01 0

-

基于不同VTH值的新型CMOS电压基准2011-08-18 2472

-

PDK是什么,它在半导体产业起着什么样的作用2020-12-24 12459

-

OpenLight宣布推出首款PDK采样器2023-03-06 457

全部0条评论

快来发表一下你的评论吧 !