AXI数据传输读写数据结构

描述

在 AXI 数据传输过程中,主要涉及到

•窄位宽数据传输(Narrow Transfer)

•非对齐传输(Unaligned Transfer)

•混合大小端传输(mix-endianness)等问题。

(1)窄位宽数据传输

当本次传输中数据位宽小于通道本身的数据位宽时,称为窄位宽数据传输,或者直接翻译成窄传输。

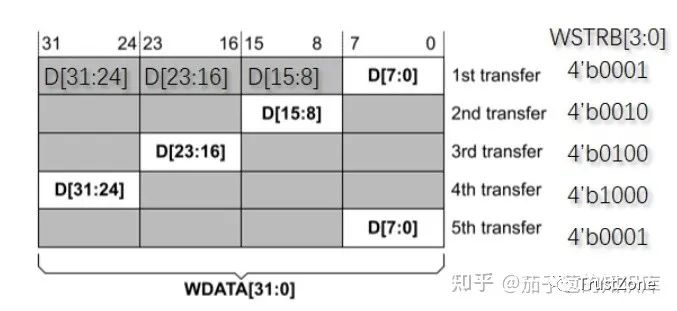

在窄位宽写传输中,主机需要告知从机数据通道中哪些bit(原文写的是字节,应该是写错了)是有效的,需要使用到写数据通道中的 WSTRB 信号。WSTRB信号中的单个 bit 置起,表示对应位置上的字节有效,对应关系为:

WSTRB[n] 对应 WDATA[8n+7:8n],也就是:当 WSTRB[n] 为 1 时,WDATA[8n+7:8n]有效。

WSTRB 信号比特位宽等于数据通道位宽的字节数量,比如 32bit 位宽的数据通道,对应 WSTRB 信号位宽为 4bit。

根据该图可直观的看出WSTRB信号的作用。上图的窄位宽传输有以下特点:

•burst 传输长度为 5

•burst 传输位宽为 8bit

•起始地址为 0x0

•数据总线位宽为 32bit

•突发类型为 INCR

引用部分可帮助理解窄位宽传输的情况:

个人理解该设计的意义在于,当主机是因为从机或者其他客观条件限制,需要进行窄传输时,可以一次性将数据放置于数据总线上,只需在每次传输期间改变 WSTRB信号即可。

以上图为例,主机将 D[31:0] 防置于总线,在接下来的四个周期中,仅需对 WSTRB 进行移位,即可依次完成 4 个字节的传输。

该结构有利于 memory 类型的从机进行写入处理,这里设想一种实现方式,结合下图讲解,在 64bit 位宽的总线上进行 32bit位宽传输,起始地址为 0x4 。此时假设存储介质位宽与总线位宽一致,为 64 bit。

在 transfer 1st 中,从机获取整个总线上的 64bit 数据存储至存储介质中,比如 DDR,并利用 wstrb 作为 mask信号屏蔽无效的低 32 bit(比如 DDR 的 DQM 信号)。

这时候存储介质的写入地址为 0x0,但实际只从地址 0x4 开始写入了 32bit 数据。在后续的 transfer 继续按以上模式工作。

-

labview数据传输2013-07-04 0

-

求助 ,关于STM32的USB数据传输问题2017-07-06 0

-

汽车行驶记录仪的数据传输设计2018-12-04 0

-

无线数据传输模块的实际应用2019-06-18 0

-

AXI-stream数据传输过程2021-01-08 0

-

怎么实现基于FPGA的具有流量控制机制的高速串行数据传输系统设计?2021-05-25 0

-

DMA进行数据传输和CPU进行数据传输的疑问2023-05-25 0

-

Modem数据传输标准2009-12-28 921

-

什么是U盘的数据传输率2010-01-30 628

-

数据传输,数据传输的工作方式有哪些?2010-03-18 5951

-

数据传输速率是什么意思2010-03-18 4941

-

数据传输中的成帧2010-03-18 3671

-

基于dMAX和EMIF接口的数据传输2011-05-12 1648

-

浅析AXI DMA收发数据传输过程2022-10-11 1950

-

AXI传输数据的过程2023-10-31 466

全部0条评论

快来发表一下你的评论吧 !