三星1.4nm工艺有何不同之处?

制造/封装

描述

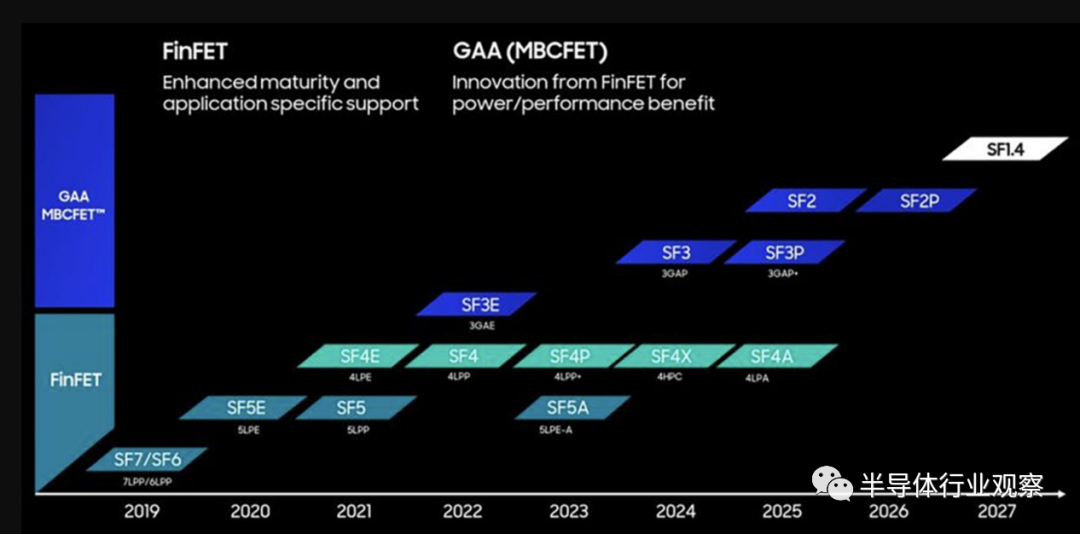

据DigiTimes报道, 三星代工厂副总裁 Jeong Gi-Tae 告诉 The Elec,三星表示,其即将推出的 SF1.4(1.4 纳米级)工艺技术将把纳米片的数量从 3 个增加到 4 个。此举有望为性能和功耗带来显着的好处。

三星是第一家在 2022 年中期推出依赖于环栅 (GAA) 纳米片晶体管的工艺技术的公司,其 SF3E(也称为3nm-class gate-all-around ear, 3GAE)。该公司使用该技术制造各种芯片,但据信该节点的使用仅限于微型芯片,例如用于加密货币挖掘的芯片。明年,三星计划推出 SF3 技术,该技术有望被更广泛的应用领域所采用。三星计划在 2025 年推出其性能增强型 SF3P 技术,该技术专为数据中心 CPU 和 GPU 设计。

同样在 2025 年,三星预计将推出 SF2(2nm 级)制造工艺,该工艺不仅依赖 GAA 晶体管,还将采用背面功率传输,这在晶体管密度和功率传输方面带来了巨大的好处,

也许在推出基于 GAA 的 SF3E 后三星生产节点的最大改革将发生在 2027 年,届时三星的 SF1.4 技术将通过将纳米片数量从 3 个增加到 4 个来获得额外的纳米片。

增加每个晶体管的纳米片数量可以增强驱动电流,从而提高性能。更多的纳米片允许更多的电流流过晶体管,从而增强其开关能力和运行速度。此外,更多的纳米片可以更好地控制电流,这有助于减少漏电流,从而降低功耗。此外,改进的电流控制还意味着晶体管产生的热量更少,从而提高了功率效率。

英特尔和台积电都打算分别于 2024 年和 2025 年开始使用 GAA 晶体管及其 20A 和 N2(2 纳米级)工艺技术。当这些公司推出基于纳米片的节点时,三星将在环栅晶体管方面拥有丰富的经验,这可能对代工厂有利。

三星:大客户接洽3奈米,2奈米、1.4奈米讨论中

“代工业务客户大约需要三年时间才能做出最终采购决定。由于我们目前正在与大客户接触,未来几年将会发生变化。”

23 日,三星电子晶圆代工部门首席技术官 (CTO) Jeong Ki-tae 在三成 COEX 举办的“Semiconductor Expo 2023”上以“晶圆代工行业的最新技术趋势”演讲者的身份宣布了这一消息。

这是对三星电子在争取高通、NVIDIA等大客户方面仍落后于台积电的批评的回应,尽管三星电子在2017年首次成功量产3纳米GAA(Gate All around)工艺。

CTO Jeong Ki-tae表示,“在代工业务中,从客户的角度来看,‘稳定性’是最重要的”,“从一开始就采用新技术并不容易。” 他补充道,“代工厂用与客户联姻的说法。这就是业务结构的紧密程度。”

解释是,如果芯片制造商出现问题,客户也会受到损害,所以他们在选择供应商时别无选择。不过,该公司表示有信心在 3 纳米及以下先进工艺领域获得大客户。

CTO Jeong 表示:“虽然 GAA 工艺是一项可持续技术,但 FinFET 技术很难找到任何进一步的改进,”并补充道,“我们正在与大客户讨论 2 纳米和 1.4 纳米等未来工艺”。

CTO Jeong预测,三星电子、台积电和英特尔在先进封装(后处理)领域的竞争格局将持续下去。

他表示,“相比前段制程,中国企业进入后段制程领域相对容易,但除非他们拥有像台积电这样的多种客户并获得反馈,或者是集成半导体公司(IDM) )像三星或英特尔一样既设计又制造,“新玩家进入竞争并不容易,”他说。

编辑:黄飞

-

借力意法FD-SOI 三星eMRAM进驻MCU早有计划2023-03-21 0

-

今日看点丨三星透露:已和大客户接洽2nm、1.4nm代工服务;广汽埃安 AION S Max 纯电轿车正式上市2023-10-27 783

-

三星宣布:DRAM工艺可达10nm2015-12-14 0

-

苹果芯片供应商名单曝光后 三星哭了!2016-07-21 0

-

线性与开关电源有何不同之处?2021-03-11 0

-

回收三星ic 收购三星ic2021-08-20 0

-

台积电将启动1.4nm制程研发,欲保持其领先地位2022-05-10 1214

-

台积电已启动1nm工艺先导计划 升级下一代EUV光刻机是关键2022-10-31 1374

-

噪音抑制与主动降噪:有何不同之处?2023-11-30 327

-

关于1.4nm,台积电重申2023-11-23 352

-

今日看点丨台积电首次提及 1.4nm 工艺技术,2nm 工艺按计划 2025 年量产;消息称字节跳动将取消下一代 VR 头显2023-12-14 773

-

台积电1.4nm制程工艺研发持续,预计2027-2028年量产2023-12-15 319

-

台积电首次提及 1.4nm 工艺技术,2nm 工艺按计划 2025 年量产2023-12-18 236

-

台积电:1.4nm 研发已经全面展开2023-12-19 355

-

光纤和光缆有何不同之处?2024-01-15 411

全部0条评论

快来发表一下你的评论吧 !