铝硅丝超声键合引线失效分析与解决

电子说

描述

摘要:

在微电子封装中,引线键合是实现封装体内部芯片与芯片及芯片与外部管脚间电气连接、确保信号输入输出的重要方式,键合的质量直接关系到微电子器件的质量和寿命。针对电路实际生产中遇到的测试短路、内部键合丝脱落等问题,分析其失效原因,通过试验,确认键合点间距是弧形状态的重要影响因素。据此,基于键合设备的能力特点,在芯片设计符合键合工艺规则的前提下,提出键合工艺的优化。深入探讨在设计芯片和制定封装工艺方案时,保证键合点与周围金属化区域的合理间距以及考虑芯片PAD与管壳键合指的距离的重要性。

1引言

在微电子封装中,封装体内部芯片到芯片,以及芯片到外部管脚之间都需建立电气连接,以确保信号的输入与输出[1]。引线键合以工艺简单、成本低廉、适用封装形式多样而在连接方式中占主导地位。目前所有封装管脚的90%以上均为采用引线键合的方式完成[2],键合的质量直接关系到微电子器件的质量和寿命[3]。

研究选用的某几款电路,均采用直径32μm铝硅丝超声键合工艺。由于采用的键合机为30度角键合头,为避免线夹及键合丝碰撞到键合指台阶,电路采用反向键合方式完成芯片与管壳引脚的引线互连。在对所选电路的封装中出现了共性化的键合质量问题,表现为电路密封前后键合目检及强度均合格,满足GJB548B方法2010.1和方法2011.1中相关规定[4],但在随后的测试和筛选考核试验中出现了部分引脚测试短路或引线脱落,导致器件失效。

2键合失效分析试验

对失效电路封装过程进行追查,未发现设备、引线、操作过程、键合参数等出现异常,首件检验也无异常,同期封装的其他品种电路也均无异常。综合考虑失效电路、封装过程和同期封装其他电路皆正常的情况,可以排除设备、引线、劈刀、人员及工艺检测等存在问题的可能[5]。

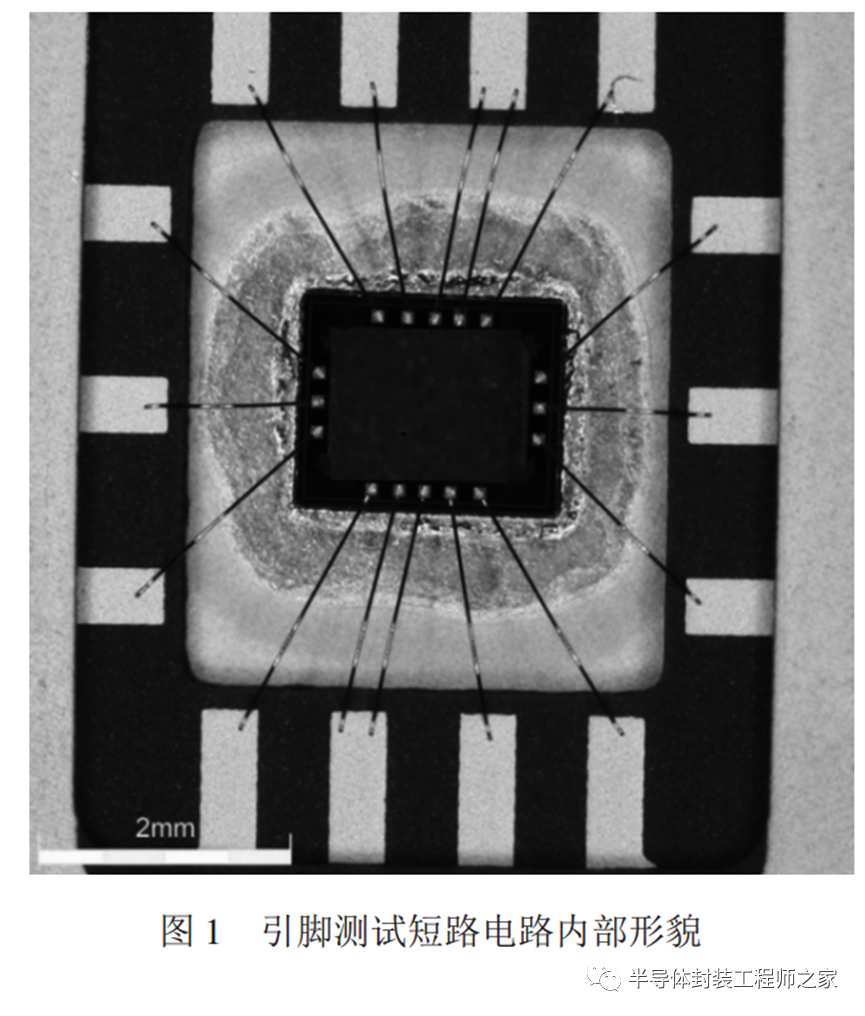

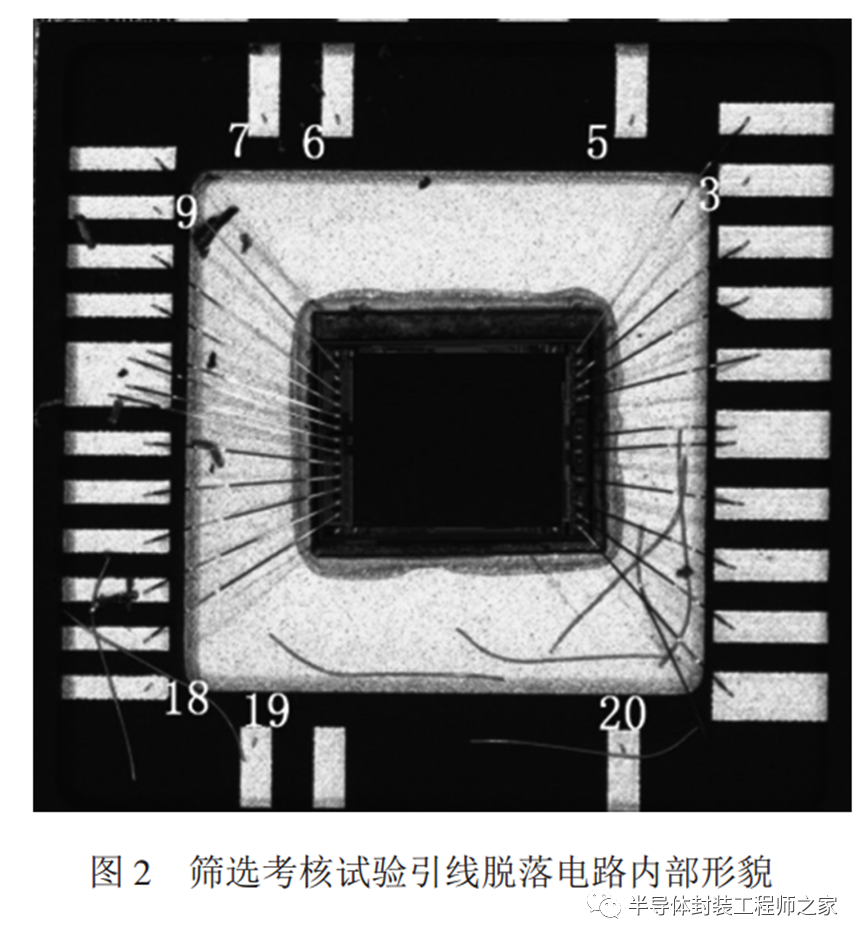

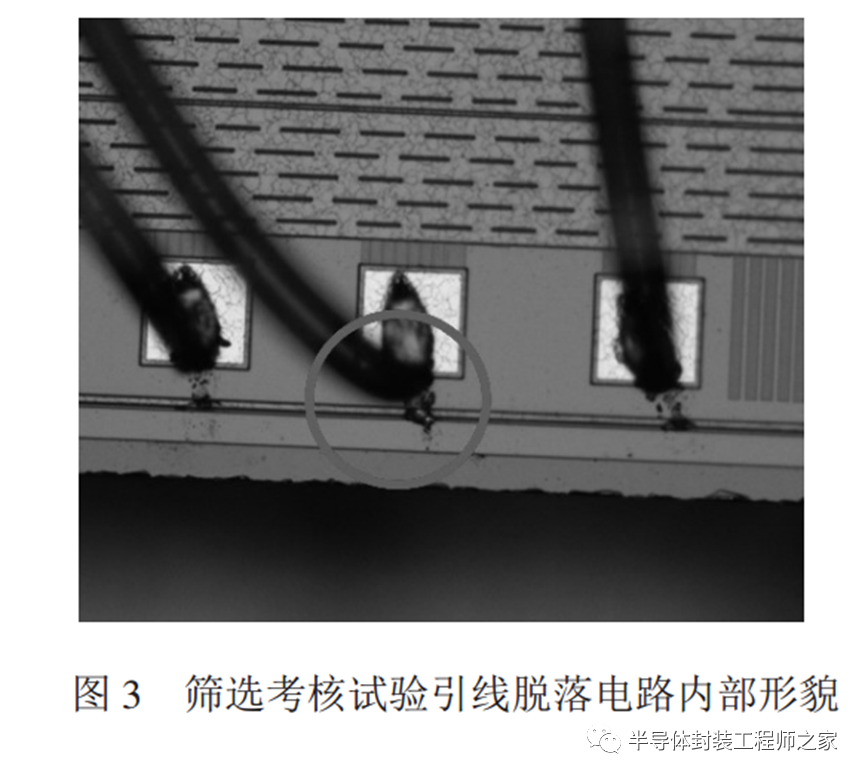

将失效电路金锡盖板开封后在显微镜下观察。引脚测试短路电路内部形貌如图1所示;筛选考核试验引线脱落电路内部形貌如图2所示。高放大倍数显微镜下观察两电路键合点及引线形貌均未见异常。

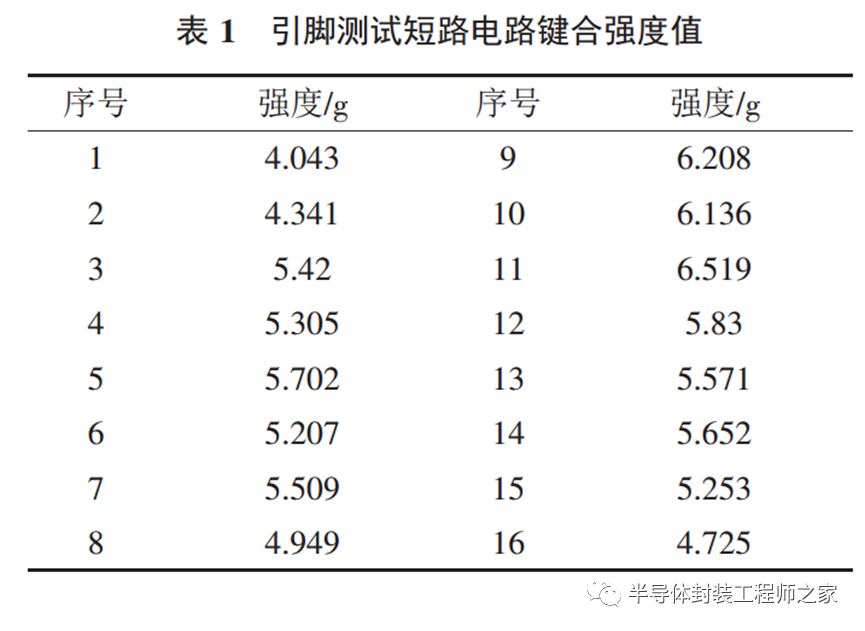

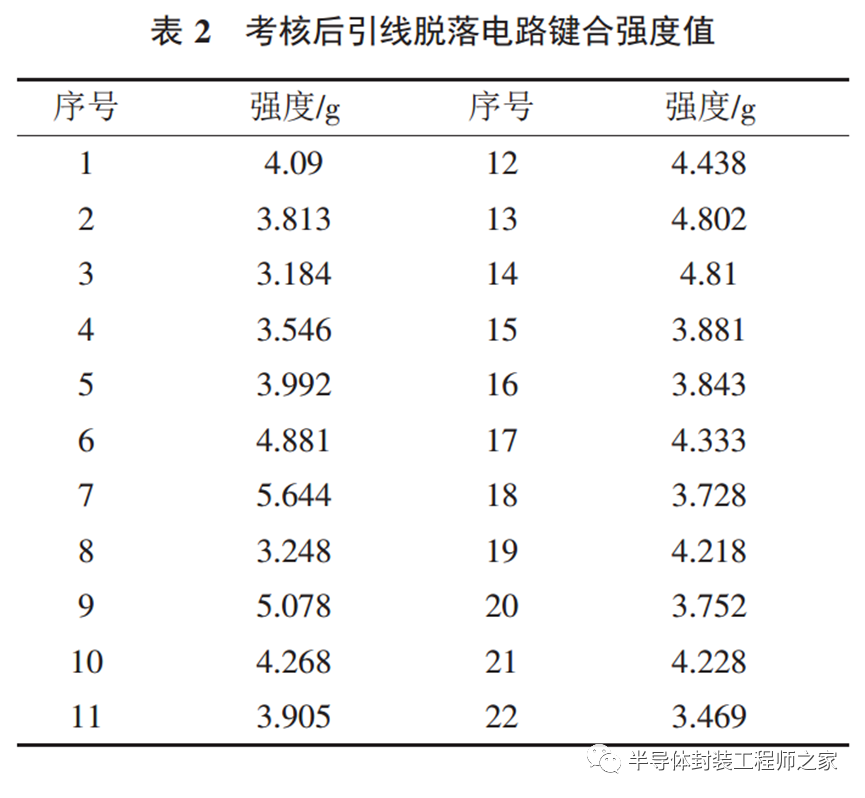

将上述两款电路分别进行键合强度测试,测试得到的拉力值如表1、表2所示。

结合图、表中的信息可以确认,两电路经密封考核筛选后,其形貌及键合强度均满足国军标中相关规定。

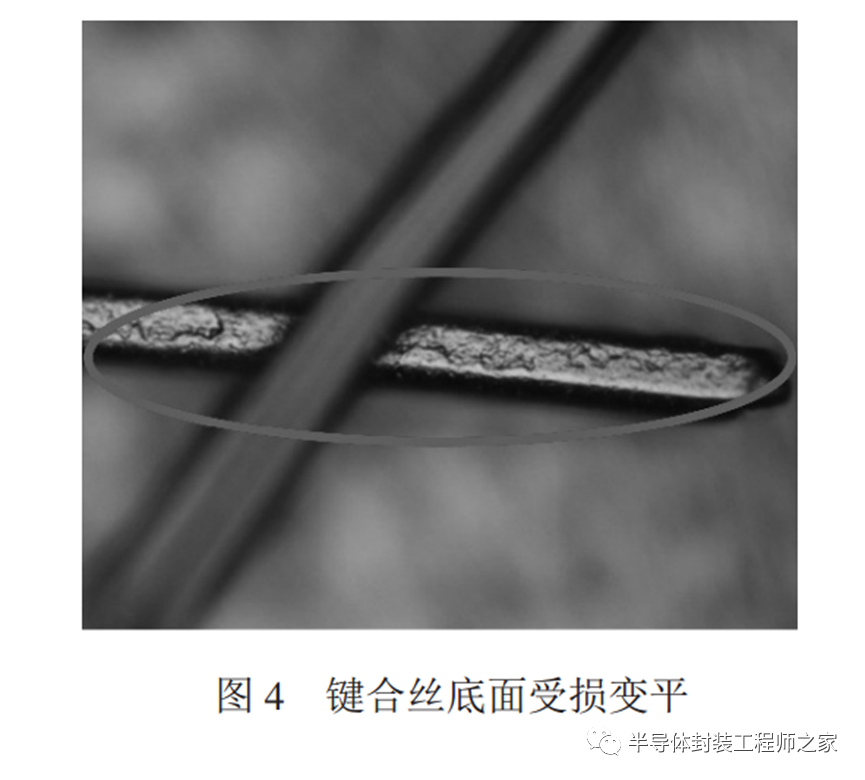

为进一步查找键合失效原因,将键合丝完全断开,观察芯片PAD及键合丝底面的形貌,结果在两款电路中均发现了芯片PAD外围环线表面钝化层破损的现象,如图3所示。同时,在引线脱落电路中发现键合丝底面由原本的圆柱形变成了平面形,如图4所示。

从图3和图4可以观察到明显的电路缺陷,在芯片PAD外围环线钝化层受到了损伤,键合丝底面受损变扁平,须针对此异常现象挖掘背后的成因,以定位问题来源所在。

3原因分析及工艺优化

超声键合原理为:键合丝与芯片表面接触,在劈刀的压力和超声振动的综合作用下,与被键合材料形成冶金结合[6-7]。

由此可推断出以下两点结论:

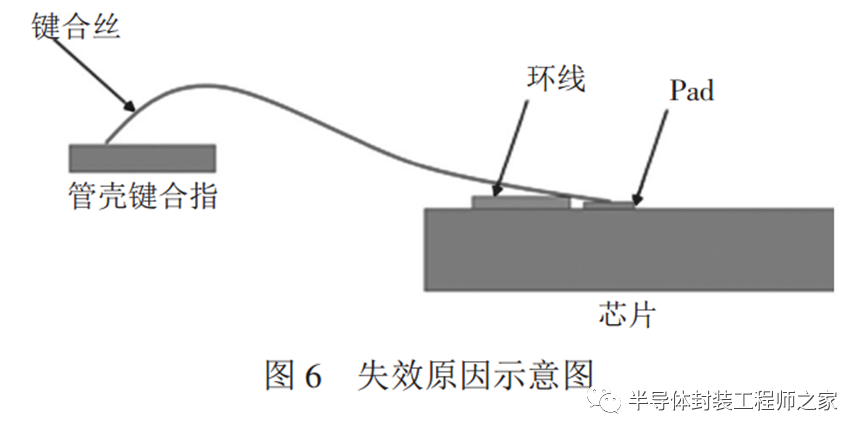

1)在测试中出现的部分引脚短路,是因为芯片PAD外围环线表面钝化层在键合过程中受到键合丝的刮蹭,受损后铝导线暴露在外面,键合丝将其与PAD搭接,两者间形成电连接,导致测试短路;

2)键合丝由于与环线表面钝化层摩擦,导致键合丝根部受损、变形或部分键合丝被剥离,强度下降,在后面的筛选考核试验中,难以承受由恒加及冲击振动带来的强度冲击,从而引起键合丝脱落。

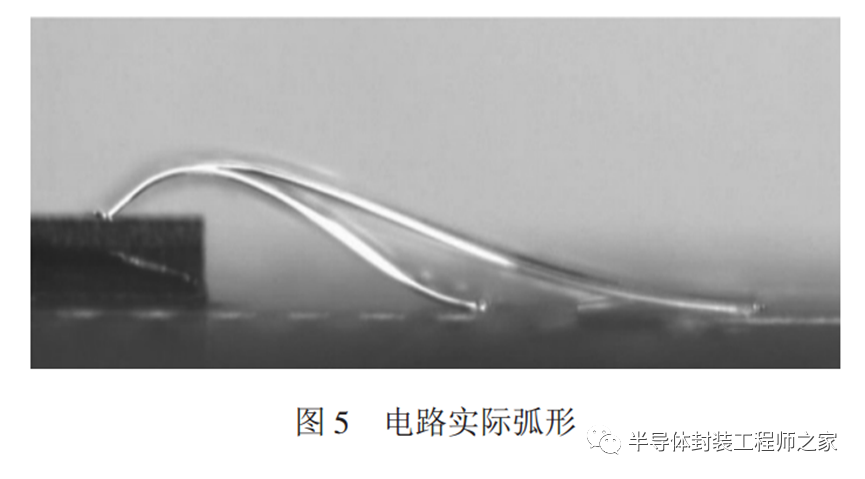

至此,造成电路测试短路及键合丝脱落的根本原因可归结为:在键合过程中键合丝与环线钝化层刮蹭,造成了钝化层的破损和引线的损伤。电路实际弧形如图5所示,失效原因则如图6所示。对此,可从两个方面采取措施,一是控制键合丝的长度,二是调整键合参数及键合点位置[8]。

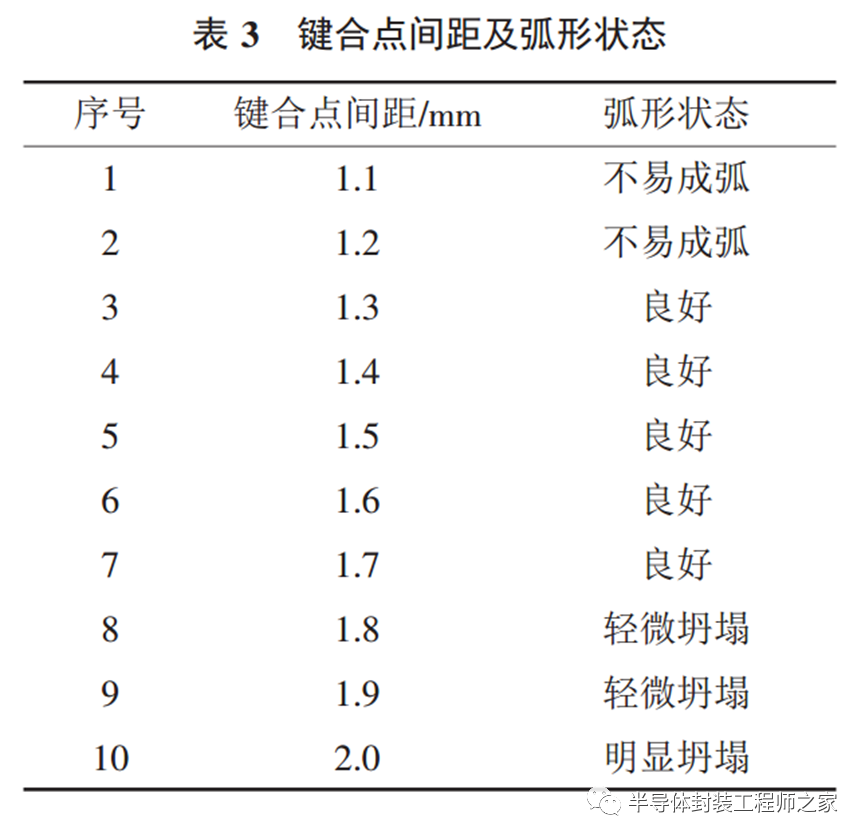

为了优化弧形,在不同的键合点间距条件下对弧形状态所产生的影响进行了试验。键合点间距选取在1.1~2.0mm之间,以0.1mm的距离递增。实验中弧形状态变化情况如表3所示。

通过分析可确定优化措施。鉴于键合点间距是弧形状态的重要影响因素,当键合点间距过大,弧形易发生坍塌,故此对此间距进行优化调整,并以AB559A键合机进行直径32μmAl-Si丝键合为例,进行对比试验,观察优化的效果。

通过对比试验可以看出,当键合点间距取在1.3~1.7mm时,弧形状态良好,键合强度较高,引线可靠性较高。此时已不再出现短路现象,引线在后续筛选考核试验中也没有出现损伤情况,表现出良好的可靠性。

在实验中还发现,当键合点间距超过1.8mm以后,引线坍塌逐步趋于明显,接近键合点根部的引线仰角变小,趋于水平甚至下垂。在筛选考核的应力试验中,不同程度地造成了引线损伤。当键合点与外围金属化区域的距离小于40μm时,则极易产生引线搭接,导致短路现象的发生。

4结束语

键合工艺的优化需要基于键合设备的能力特点并符合键合工艺规则的芯片设计方案,以AB559A键合机为例,键合点间距在1.3~1.8mm时,引线弧形较好;当键合点间距大于1.8mm时,线弧会发生轻微坍塌,可能直接引起短路或在后续应力试验中引发引线的损伤甚至断线。因此,在芯片设计和封装工艺方案的制定中,应保证键合点与周围金属化区域的间距至少在40μm或PAD尺寸的50%以上,同时还要考虑芯片PAD与管壳键合指的距离大小。

审核编辑:汤梓红

-

有偿求助本科毕业设计指导|引线键合|封装工艺2024-03-10 0

-

半导体引线键合清洗工艺方案2010-04-22 0

-

元器件失效了怎么分析? 如何找到失效原因?2016-10-26 0

-

元器件失效分析方法2016-12-09 0

-

IC智能卡失效的机理研究2018-11-05 0

-

芯片失效分析2020-01-10 0

-

芯片失效测试方法汇总2020-01-17 0

-

失效分析方法---PCB失效分析2020-03-10 0

-

MLCC样品失效分析方法汇总2020-03-19 0

-

LED芯片失效分析2020-10-22 0

-

关于封装的失效机理你知道多少?2021-11-19 0

全部0条评论

快来发表一下你的评论吧 !