英伟达系列芯片设计的高阶自动驾驶系统启动时序流程

电子说

描述

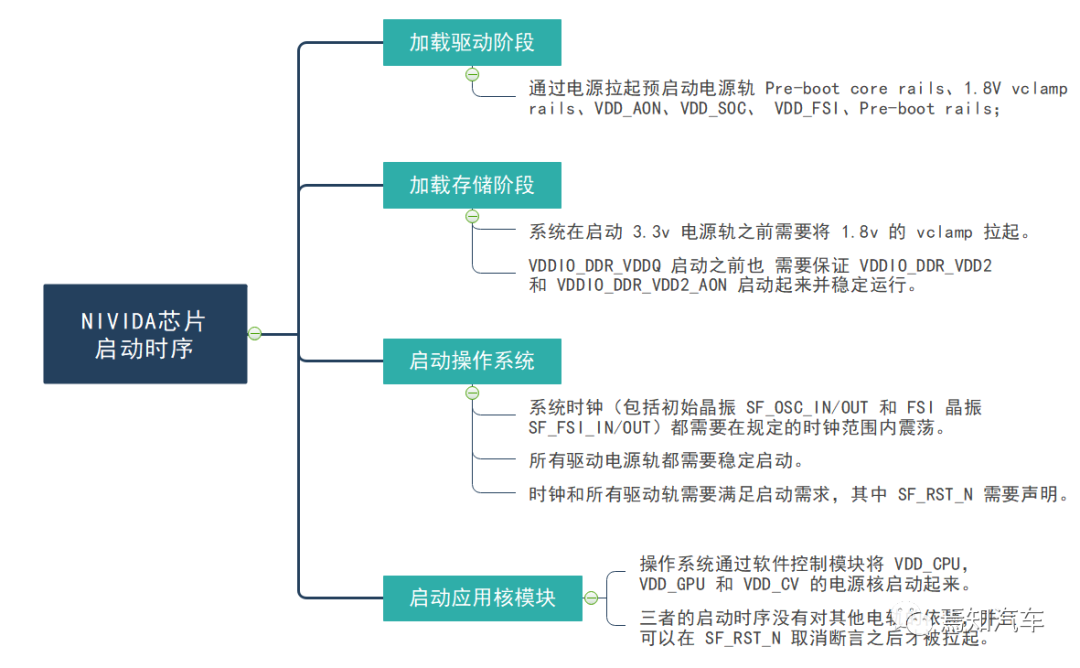

本文所阐述的整个状态定义还处于顶层状态,也不能表征 Orin 系列内部的所有状态细节和事件。Orin系列芯片启动 ROM 执行并最终通过控制到系统依赖的软件。整个 Orin 启动分为加载驱动、加载存储、启动操作系统、调用应用核模块几个大方向。

如下图所示,各时序图所表示的整个 SOC 芯片启动时序。

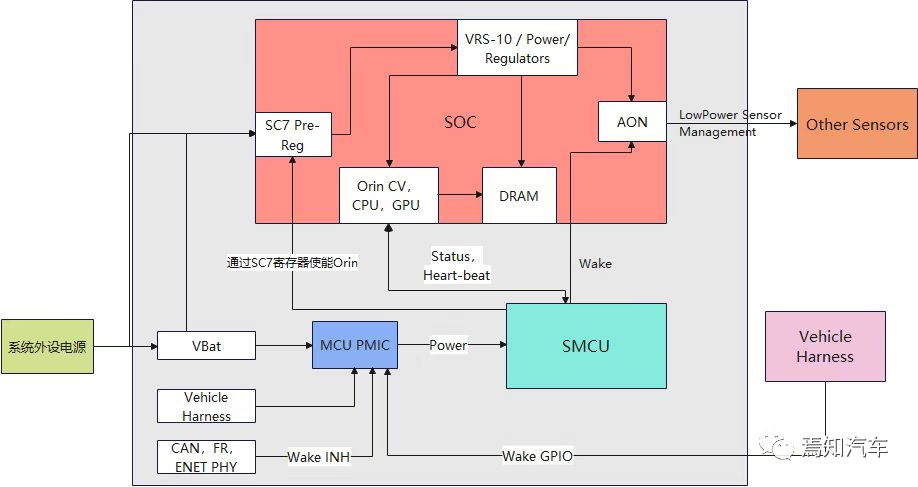

通常,Orin 系列芯片所能实现的高阶驾驶辅助系统架构通常需要引入单独的 MCU 芯片对其规划的执行指令做执行仲裁,其他系统电源轨由SMCU进行监控。这样不仅可以提升相应的安全等级,也是作为低电压控制的关键策略。在Orin功能安全岛中可以运行OEM跟功能安全相关的算法,如车控算法、比对算法、传感器后融合算法等。通过运行Safety框架,对Orin芯片对Orin系列芯片和Drive OS软件进行监控。

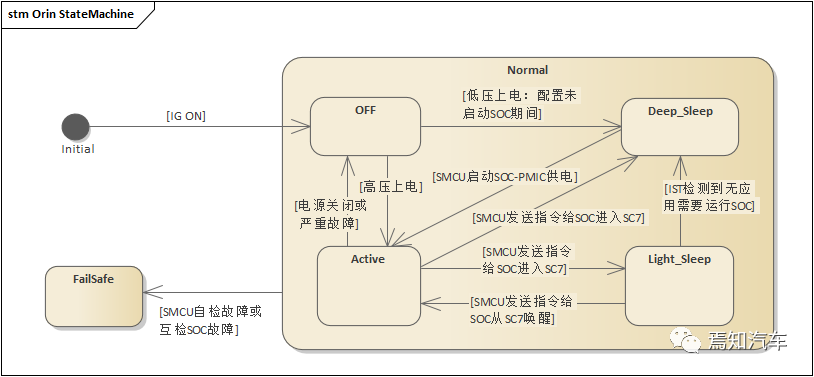

Orin系列芯片支持各种电源状态包含Active(SC0)、Deep Sleep(SC7)、OFF SC7 电源状态,同时也被称为挂起到存储状态,这种设置是在用于从深度睡眠(SC7)状态到激活(Active)的快速重启中,SC7 在这种状态下一直处于低电量消耗的睡眠状态。

不仅 SC7 进入和退出需要专门的电源供给时序,同时也需要操作系统(这里指英伟达专门的操作系统 Drive OS)支持从挂起状态中重启。这个过程涉及两个子过程“Suspend-to-Memory” (即悬置到存储态),再从“Memory-to-Resume”(从存储态到重启)。这里的存储(memory) 单元实际就是系统的动态随机存取内存(DRAM)。

英伟达系列芯片的功耗模式主要有四种电源状态,且这四种状态之间可以进行有效的状态跳转。

如下表表示了典型的电源转换表。

| 电源状态 | Orin PMIC状态 | MCU PMIC状态 | 使用场景 |

| OFF | OFF SC7 | OFF | 系统关闭(KL30 未连接上) |

| Deep_Sleep | Deep Sleep(SC7) | Standby | 深睡眠状态,可通过 PHY 线、SC7 故障或者整车电源唤醒 |

| Light_Sleep | Deep Sleep(SC7) | ON | 待机状态,可通过 PHY 或整车 电源(GPIO)唤醒 |

| Active | Active(SC0) | ON | 整个系统被开启且具备完整 的功能(电源连接至 KL30) |

| FailSafe | FailSafe | FailSafe | MCU PMIC/Orin PMIC的失效模式状态表示 当严重错误被检测到 |

当然,如上的系统状态是通过SYS_VIN_LV VRS_10/12 VDD和SYS_VIN_HV VRS_11/VDD进行同步监测的。

对于 Deep_Sleep和Light_Sleep两种状态,可以通过特定设置来决定 PHY 的电源状态,他们可以选择将自己的待机模式放在上面,也可以将完整的电源关闭。Tier1 或主机厂需求也可以决策如何通 过 PHY 线来进行唤醒。例如,如果整车线束的 GPIO 口可以用来作为唤醒源,则所有 PHY 可 以在Deep_Sleep和Light_Sleep状态下完全关闭。

以上每个状态之间还有中间状态,可以被区分为 a、b 两种子状态,从 a 到 b 的两种子状态转换会发生在 MCU 所连接的固件启动没有其他额外触发事件的情况下,这些固件包括摄像头的子系统和其他系统设备电源供给。当然,这些固件是可以通过 MCU 通过内部启动模块进行单独启停控制。当 MCU PMIC 或Orin PMIC出现严重错误时,系统将进入 FailSafe状态,MCU 的整个电源状态将被置位为故障状态。

接下来将对Orin系列中的电源每个子模块进行详细说明。

1)AON(Always on Cluster)群集

可以提供所有可能的硬件特征用于支持低电压传感器管理和唤醒使用场景。这些集群指令包含一个 ARM Cortex-R5 的紧耦合内存的处理器核,可以支持周边件(如时钟、中断控制器),不同的 I/O 控制端,路由逻辑。AON 模块中的 Cortex-R5 处理器也可以被当做传感器处理引擎(SPE)。

AON Cortex-R5 可以实现:

ARM V7-R ISA 完整指令集和数据缓存紧耦合存储(TCM)接口用于局部 SRAM

向量中断支持

64 位 AXI/32 位 AHB 初始化接口,可分别用于 DRAM 需求和 MMIO 需求

32 位 AHB 初始化接口可以用于 ARM 向量中断控制器接入

AXI 目标接口用于 DMA 接入到局部 SRAM

2)SC7-深度睡眠

SC7 是用于在最低可能的电源输入下来进行快速重启。该状态下所有 CPU 核被关闭,且大多数的 I/O 和内部模块都被关闭了,软件执行被挂起。系统状态被保存在 DRAM 中,并且总是处于自更新模式。

芯片从浅睡眠转移到深睡眠的状态需要满足如下条件:

冻结所有正在运行的应用

同步文件系统内容到存储设备

挂起各自的设备驱动,保存 DRAM 中的其他状态

将 DRAM 放到自刷新模式中

当需要在 SC 之前运行时,断电序列也与系统内测试有关。

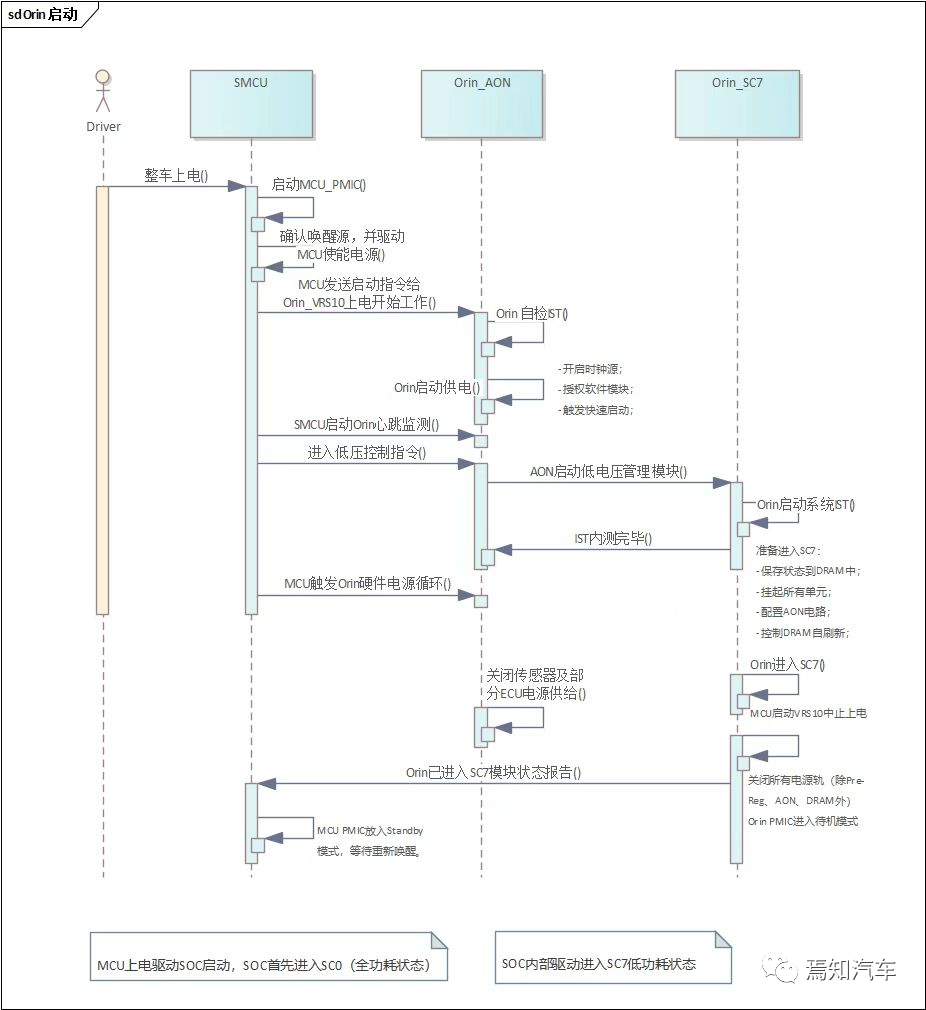

如下图表示了整个系统进入和退出低功耗模式的电源启动时序图(其中,如下左图表示 SC7 内侧进入时序)。

进入退出低功耗时序图

进入退出低功耗时序图

对如上时序概括起来将,Orin-x 进入深度睡眠(SC7)实际是间断性的关闭一些高功耗模块。其中,包含如下完整的处理步骤:

首先, 通过电源管理软件模块关闭最高功耗模块:VDD_CPU、VDD_GPU 和 VDD_CV 电源轨, 从而为进入 SC7 深睡眠模式做准备;

其次, SC7 进入固件将 DRAM 置于自刷新过程中;

然后, SC7 进入前需要将固件配置时钟节拍完成后才进入电源深度休眠状态。在进入电源深度休眠前,软件需要确保IO 状态不会和任何其他平台需求(比如拉高拉低需求,额外的元器件需求)相冲突,从而确保 IO 漏洞尽可能最小化;

Orin 芯片的使能端 SF_PWR_SOC_EN 被 PMC 固件和其中的电源轨会被逐步取消断言;

平台依赖 IO 电源轨和 PLL 电源轨将被选择性的关闭;

两个存储控制端口 VDDIO_DDR_VDD2 和 VDD_DDR_VDDQ 电源轨将被关闭;

基于芯片正常电压和特征参数而变化的逻辑轨 VDD_SOC 和功能安全控制电源轨 VDD_FSI 将 被关闭;

接下来是系统如何退出低功耗模式。

当系统断电后,系统硬件会将电源和时钟给到 Orin-x 芯片。注意可能有其他的系统层限制(比如 LPDDR5 存储电源时序限制)出现。

整体上退出低功耗模式SC7是有整车传递过来的指令输入。首先,需要完成包含MCU PMIC电源管理程序后,由MCU控制触发SC7退出指令,同时控制VRS10开始正常上电工作,随即Orin芯片开始进行自检后控制退出SC7并开启时钟源、授权软件模块、触发快速驱动,最后进入下一个待命状态。MCU端则开始与Orin之间启动对应的心跳监测。

3)系统内检(IST)

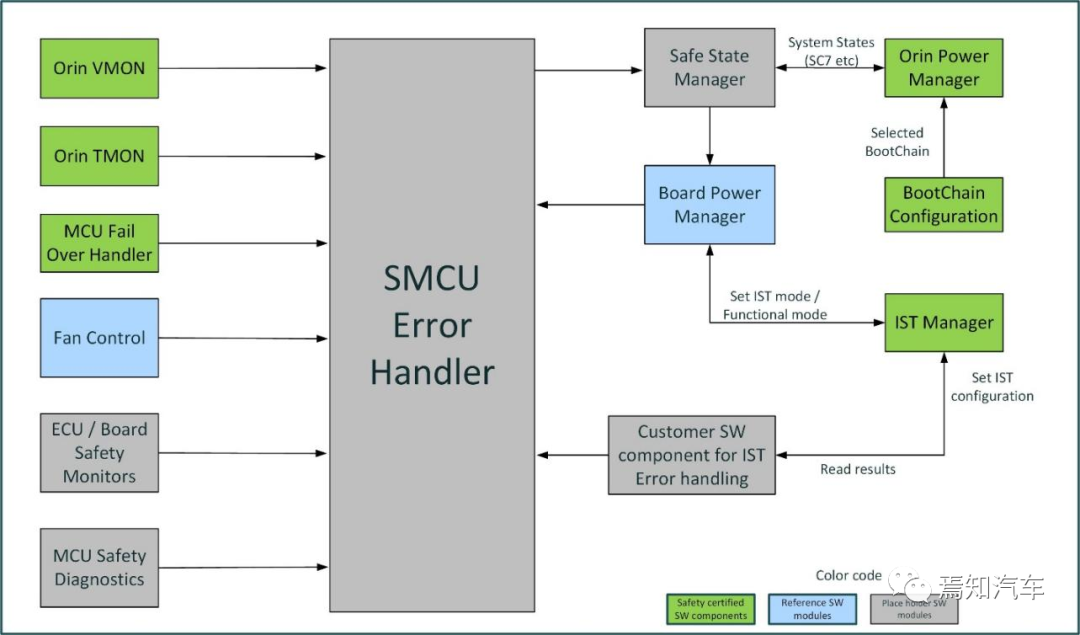

Orin系列芯片会提供一种机制来检测由系统内测(IST)所产生的永久的故障,IST 应该在 Orin-x 功能安全系统中使用期间被启动。IST 需要以特定的规则来配置零部件的软硬件。IST 可以配置来执行一个在单 Orin-x 或者 Orin-x 外加一个 dGPU 的模式组成智驾系统。整个错误(Failsafe)处理机制如下:

①当系统无错误时,标准的电源时序会通过特定的 I/O 端或总线(CAN/Flexray/Ethernet PHYs) 唤醒整个系统。这也包含启动所有 SC7 断电域,然后是支持从内存恢复的操作系统 DRIVE OS,以结束正在运行的活动状态。其中,启动的快慢取决于内存的自恢复能力。

②当 SC7 模块失效或 Timeout 时会产生相应的失效时序,芯片内部错误、温度异常导致的宕机、低压/过压等都是这些失效模式之一。整体来说,如果芯片处于失效状态时,实际是首先唤醒 MCU 后,通过内部检测机制确认是否进入 SC7 。已经 timeout 或故障时,需要控制 VRS-10 关闭所有的 SC7 电源轨,只留下唤醒 PHY 线处于低电压供电状态。MCU 最终会将PMIC 模块至于待机状态后将MCU 关闭。

此外,系统内测程序 ITS 还需要检测 Orin 是否长期维持在低功耗状态 SC7下,如果是,则系统将会退出该低功耗SC7模式。并且在下一个系统自检过程中判断是否有重新进入低功耗SC7模式的需求。

对于IST系统内侧应用而言,NVIDIA Orin 专门配置了相应的IST管理器来实现如下一些功能子项:

①提供一个用于设置IST配置的接口。

将用户应用程序设置的配置与NVIDIA DRIVE Orin通信™ 以太网上的软件(IST客户端)(用于钥匙打开/关闭Orin IST)。

②提供一个用于读取IST结果的接口。

提供接口,平台电源管理器可以使用这些接口查询是否必须执行Keyon/KeyOff IST,并查询IST是否已完成。

③在引导过程中,决定NVIDIA Orin应处于IST模式还是正常模式。

④通过GPIO断言触发IST,监控NVIDIA Orin上IST的执行,并通过超时检测IST卡住的场景。

⑤提供一个中止IST执行的接口。

⑥检测并处理以下硬件错误情况。

在某些情况下,IST的执行会受阻,且该阻塞会由基于GPT的硬件计时器检测到,该计时器具有可配置的超时。与 DRIVE Orin的通信™ SoC由具有可配置超时的软件计时器进行监控。这取决于MCU和Orin之间的活动以太网(VLAN200)连接。客户应用程序应使用NvMCU_ISTManager提供的接口,在每个电源循环期间设置有效的IST配置。这是使用串行控制台外壳命令完成的。

总结

本文从芯片内部到芯片外部详细分析了整个芯片工作的启动时序流程、状态跳转、系统监控能力等。相对于单SOC芯片启动而言,基于SOC+MCU的自动驾驶系统架构可更好的利用两芯片各自的优势进行互补,同时其按照基础的驱动原理也可以由SMCU很好的对整个电源管理和启动时序进行管控和监测。考虑Orin系列芯片在后续智驾系统的不断深入应用,这些前期的设计分析过程必将成为后期系统架构和硬件架构设计中不可或缺的一环。

审核编辑:刘清

-

【话题】特斯拉首起自动驾驶致命车祸,自动驾驶的冬天来了?2016-07-05 0

-

自动驾驶真的会来吗?2016-07-21 0

-

细说关于自动驾驶那些事儿2017-05-15 0

-

自动驾驶的到来2017-06-08 0

-

AI/自动驾驶领域的巅峰会议—国际AI自动驾驶高峰论坛2017-09-13 0

-

UWB主动定位系统在自动驾驶中的应用实践2018-12-14 0

-

如何让自动驾驶更加安全?2019-05-13 0

-

自动驾驶汽车的处理能力怎么样?2019-08-07 0

-

自动驾驶系列报告大放送了涉及传感器,芯片,执行控制等2019-08-09 0

-

自动驾驶AI芯片现状分析2020-12-04 0

-

自动驾驶系统设计及应用的相关资料分享2021-08-30 0

-

自动驾驶技术的实现2021-09-03 0

-

安培GPU发布 英伟达自动驾驶芯片算力升级2020-06-05 2857

-

自动驾驶备受关注 小马智行完成D轮融资 英伟达将量产自动驾驶芯片DRIVE Orin2022-03-30 3052

-

高通自动驾驶靠软件开发革新力压英伟达自动驾驶芯片2024-02-20 899

全部0条评论

快来发表一下你的评论吧 !