一个运放的STB仿真和AC仿真区别分析

电子说

描述

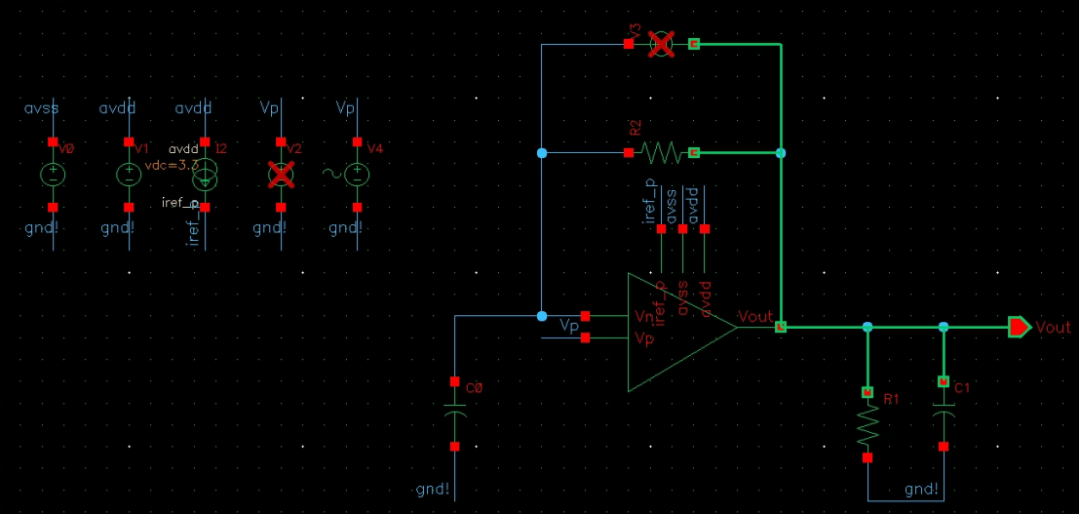

以一个二级弥勒补偿运放为例,说明stb仿真和ac仿真的区别,vdd=3.3,Vcm=1.25V,ibias=5uA,负载电容是5pF,负载电阻是100K。

注:二级运放是pmos输入差分对,第二级是nmos共源级(原理图是NM5),负载是pmos电流源(原理图是PM5)。

1.stb仿真

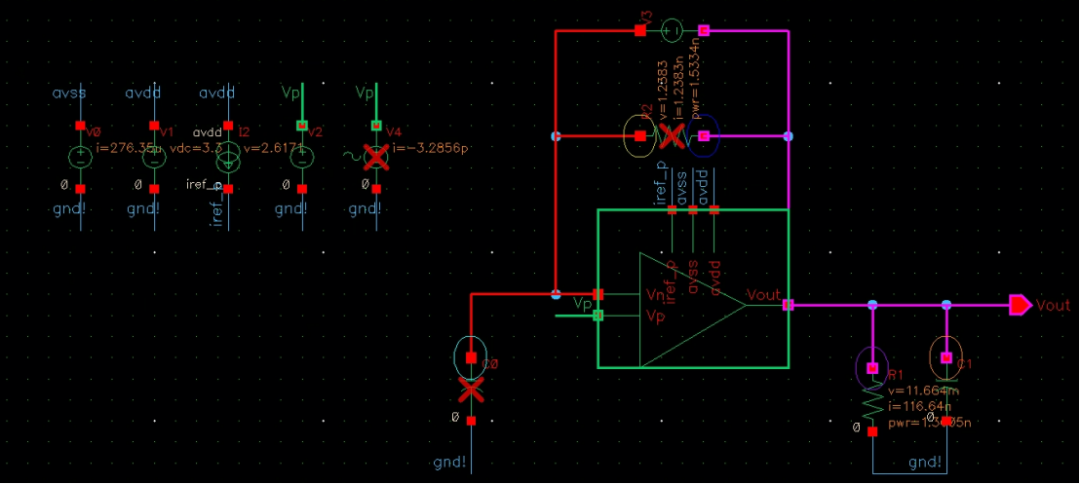

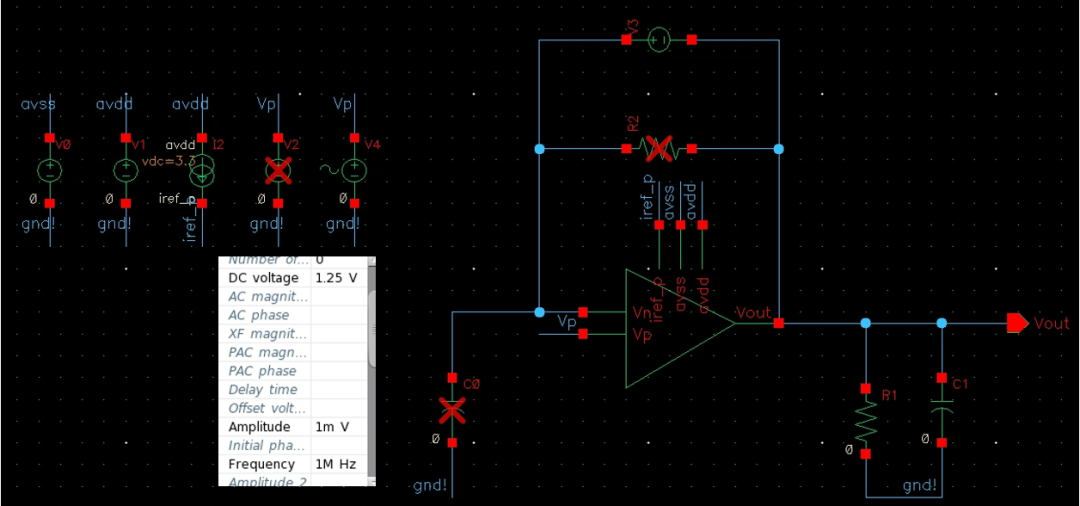

加入一个vdc=0的电压源做probe(下图中V3),接成单位增益反馈形式,Vp给一个直流源=1.25V。

stb仿真分析环路特性的testbench

仿真环路稳定性,结果如下:

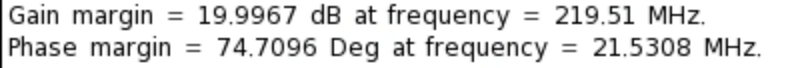

(1) 频率范围从0.001Hz1GHz(从1Hz1GHz结果是一样的)

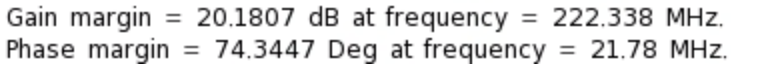

仿真的output log汇报的稳定性参数如下:

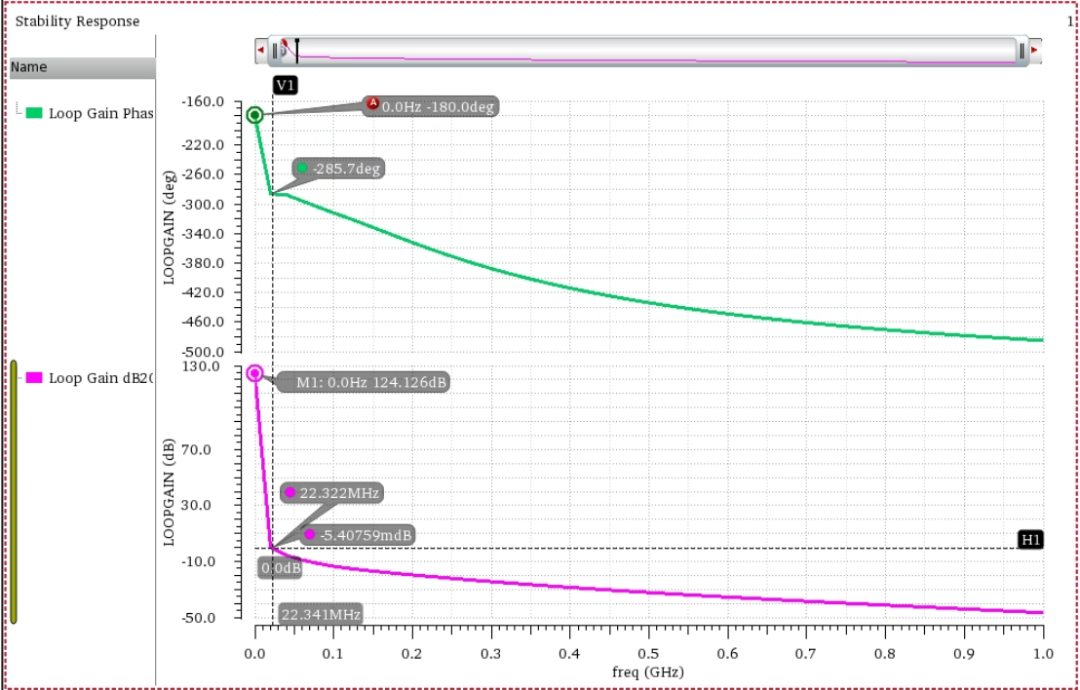

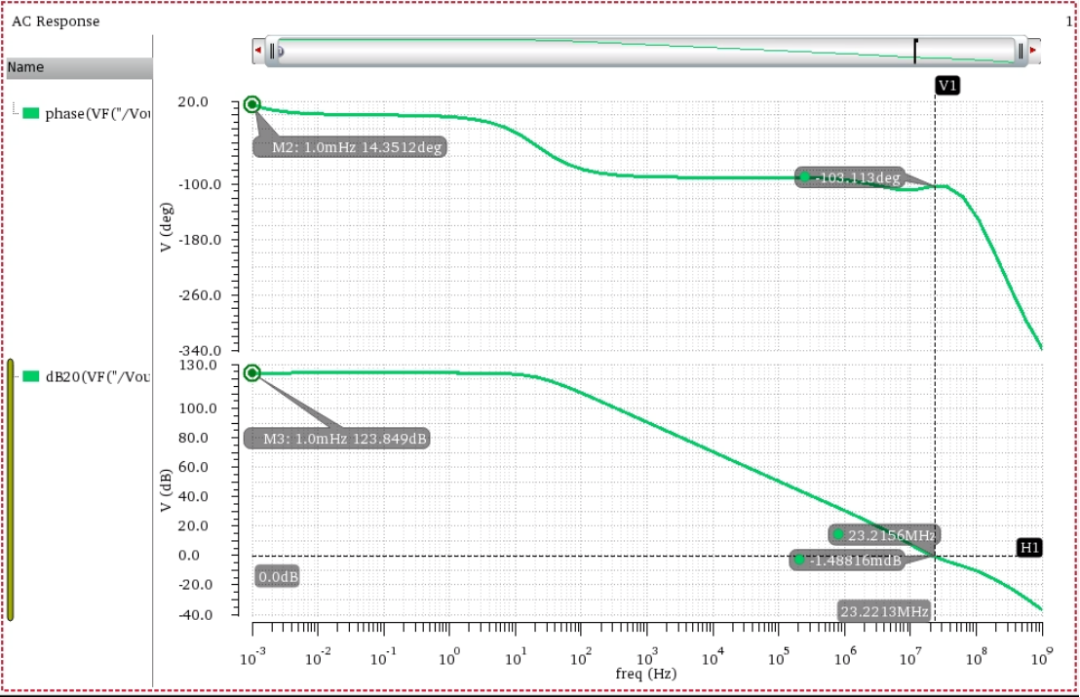

绘制出波特图如下:

stb仿真的波特图

可看出,低频相位从179.99度开始(看成180度),波特图正常,从低频的180度下降180到0度,就是相位交点PX,在增益交点GX(环路增益幅度为1,DB=0处)频率是21.79MHz(即GBW),GX对应的相位是74.69度,高出0度74.69度,这个值就是PM相位裕度。GBW和PM的结果和output log汇报的结果吻合。

运放一般都是闭环使用,开环使用就是一个性能拙劣的比较器。

由于是单位增益,因此反馈系数β=1,环路增益就是运放的开环增益。

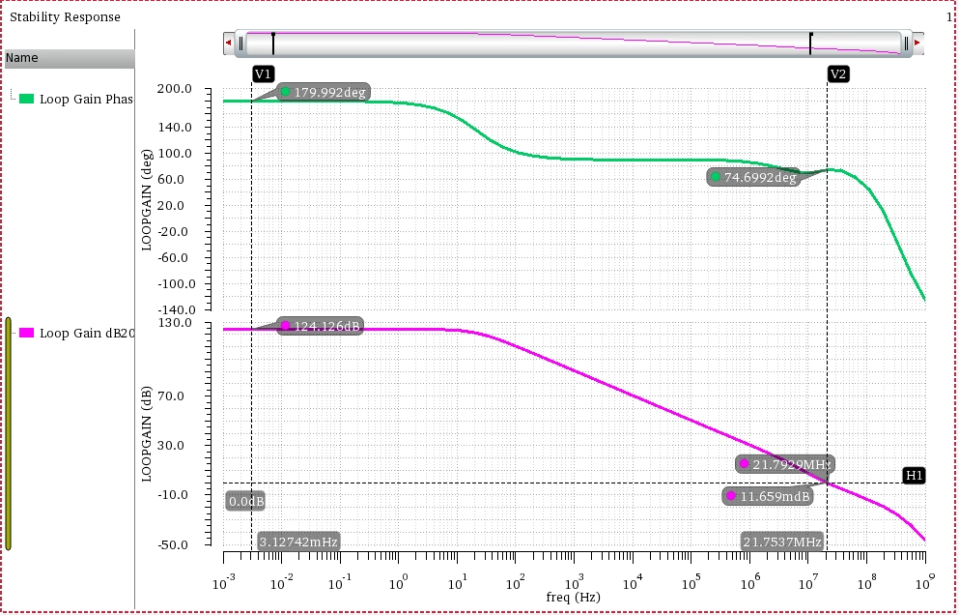

以下标出了频率为1KHz和1MHz时的环路增益。

1K频率,增益还很大(90.7dB=34276.8倍),1M的时候增益很小了,31.2dB(36.3倍)。

1K 和1M处的环路增益值

(2) 频率范围从0Hz~1GHz

仿真的output log汇报的稳定性参数如下:

绘制出波特图如下:

stb仿真的波特图

波特图形状奇怪,相位从-180度开始,下降180到-360度,增益交点频率(GBW)对于的相位是-285.7,高出-360约74.3度,即PM,也是可以和log汇报结果对上的,PM结果和GBW结果是正确的,但是图的形状很奇怪。

注:无论是比特图分析还是噪声分析,初始频率值都不要设置成0HZ,设置成0Hz结果不靠谱。

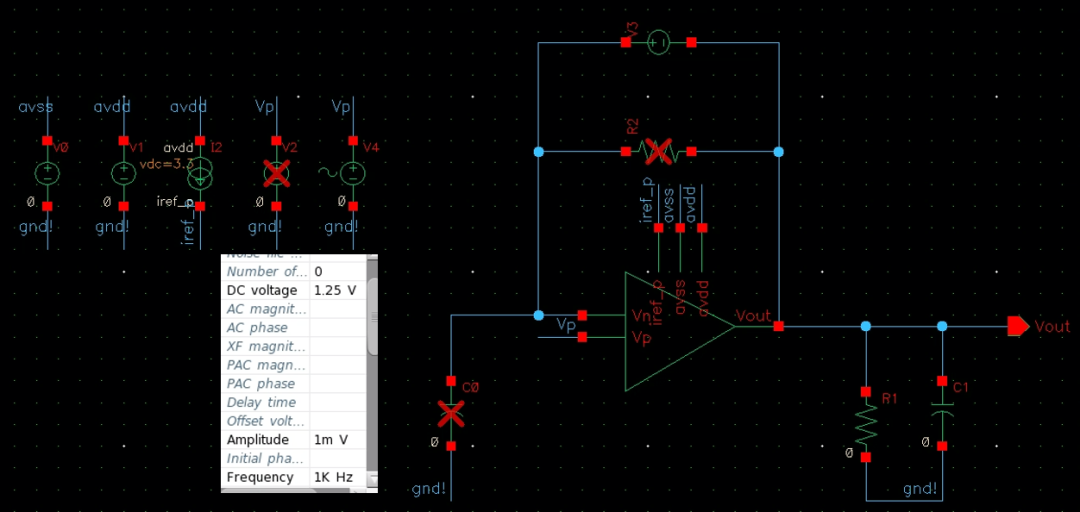

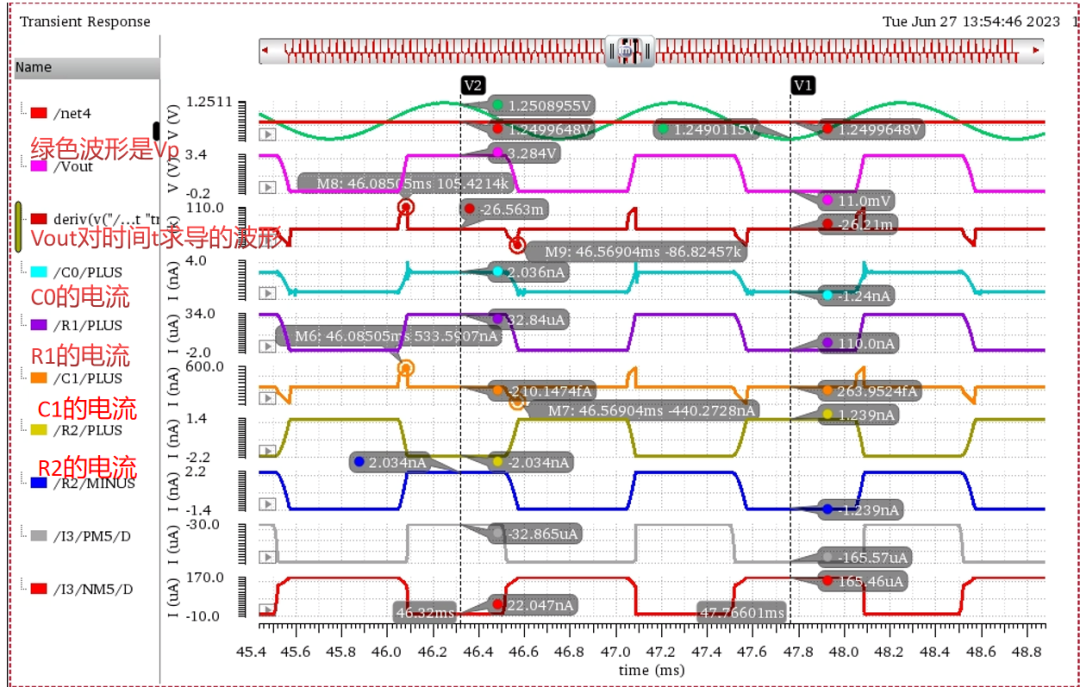

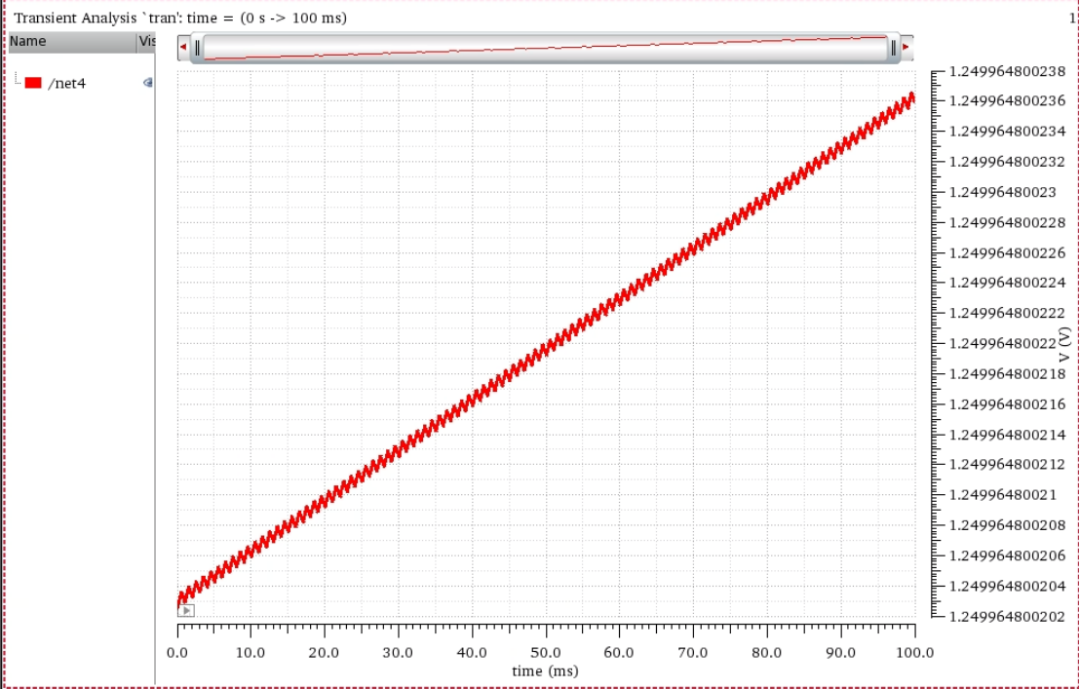

(3) tran仿真--情况1

Vp设置为dc=1.25V,幅度是1mV,频率是1KHz的正弦.

tran仿真的testbench

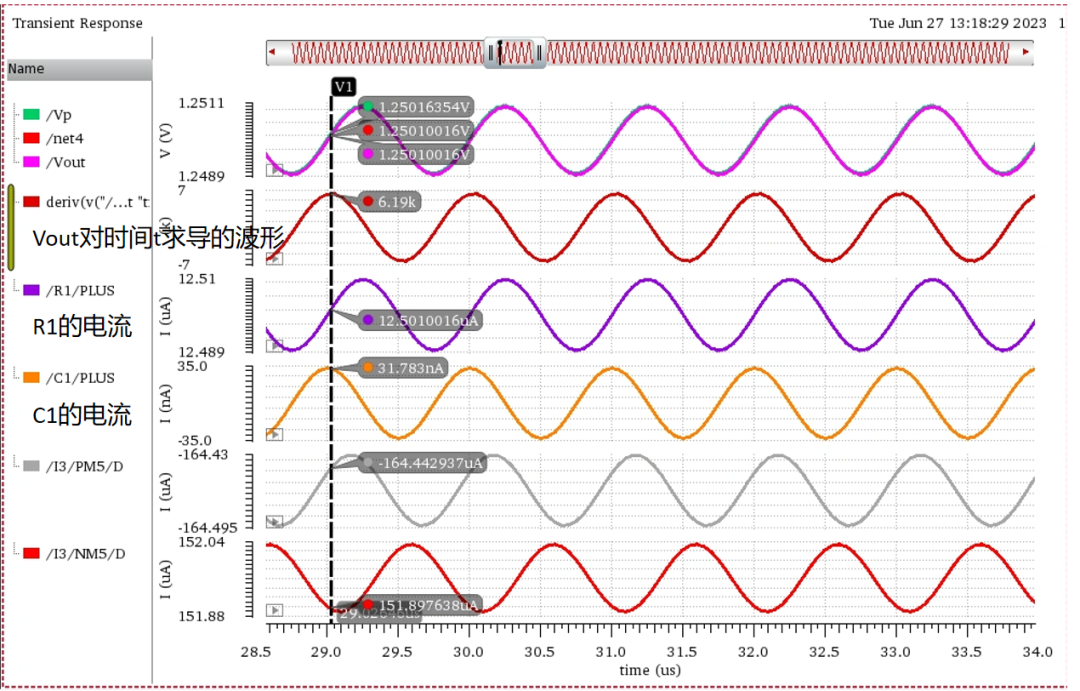

1K频率正弦,1K时候的增益还很大(90.7dB=34276.8倍),1K的时候做到了很好的单位增益,两端输入(Vp是正端,net4是负端)和输出Vout大小相等,波形重合。

注:二级运放是pmos输入差分对,第二级是nmos共源级(原理图是NM5),负载是pmos电流源(原理图是PM5)。

tran仿真结果(1K正弦)

仔细分析波形图,Vout/R1就是流过负载电阻R1的电流,Vout求导再除以C1就是流过C1的电流,Vout求导值最大的时候,就是C1电流最大的时候,因为Q=CU=IT,电流I=C*ΔU/ΔT,此时R1和C1的电流是从二级运放的第二级的pmos电流负载管PM5抽取的,此时由于Vout在1.25上下,Vout只会给C1充电,C1不会放电,不会向nmos放大管NM5灌电流。

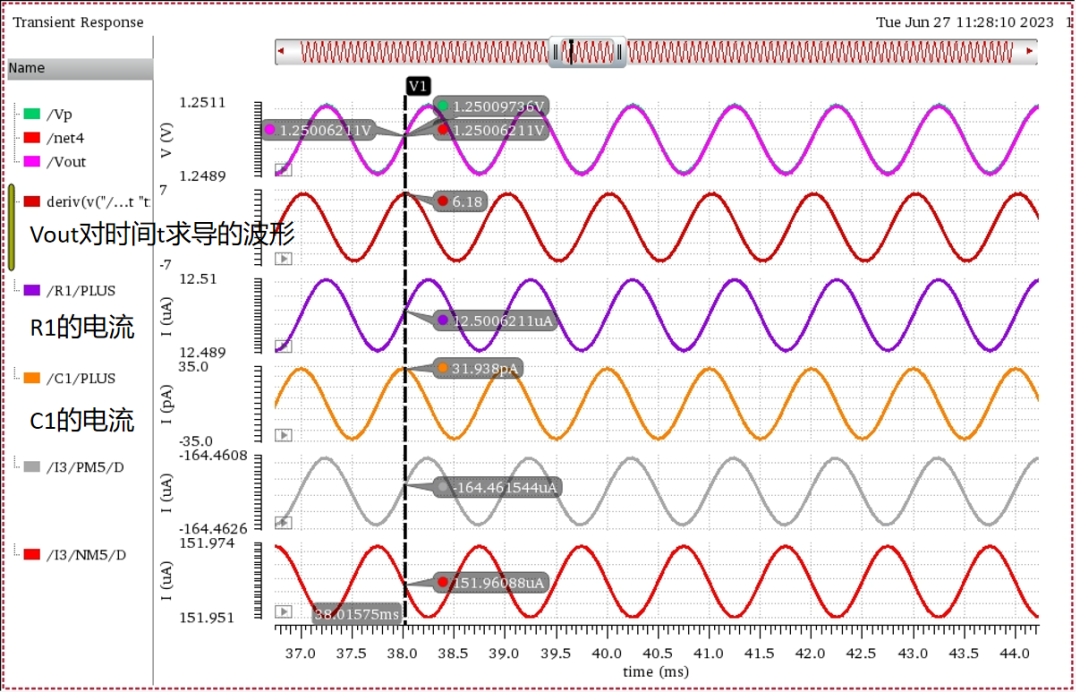

(4) tran仿真--情况2

Vp设置为dc=1.25V,幅度是1mV,频率是1MHz的正弦.

tran仿真的testbench

tran仿真结果(1M正弦)

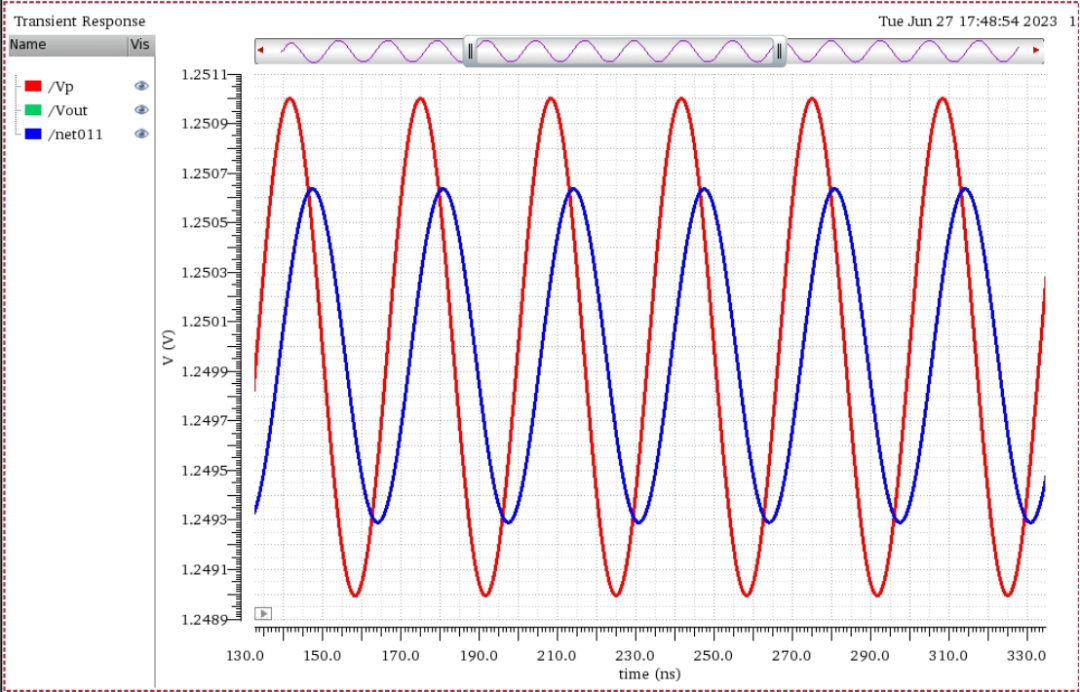

虽然此时环路增益很低了,但是也实现了不错的单位增益buffer。A(Vin-Vout)=Vout,将1M时的环路增益(约是36)代入进去,不会有这么好的跟随效果啊?why?难道是因为负反馈的调节作用?当Vout大于Vin了,即Vp

输入改为30MHZ的正弦波,大于了GBW,但是也能跟随,虽然跟随的不好。30M的时候在波特图上,环路增益已经是衰减的了,即开环运放的增益是负的了,衰减了。

tran仿真的结果(30M正弦)

作者也没明白这里是什么原因,有知道的伙伴可以留言哦。

2.ac仿真

注:我们导师说仿真稳定性最好不要用ac仿真,大家都是用stb。

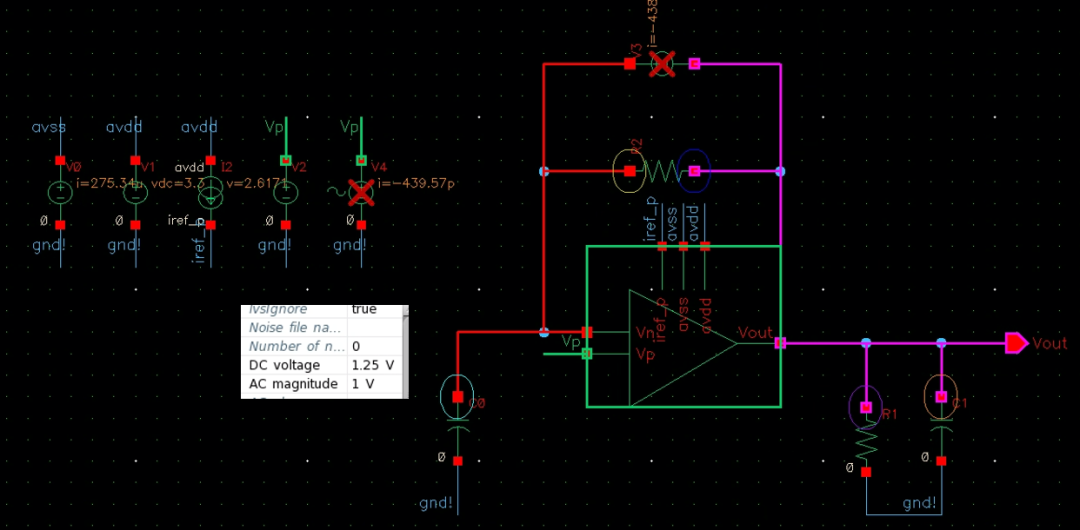

稳定性仿真,Vp的交流幅度改为1V,加入1G大电阻和1F大电容,前者提供直流反馈,后者旁路交流小信号分量。

ac仿真运放的稳定性testbench

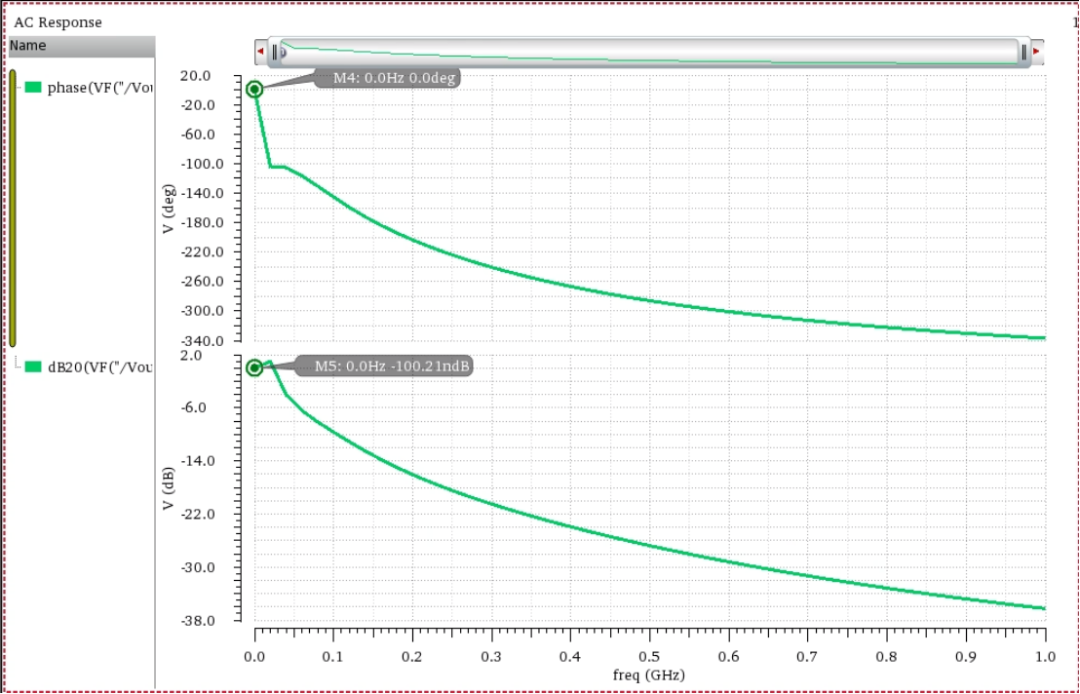

(1) 频率范围从0.001Hz~1GHz

ac仿真的波特图

低频增益和stb仿真结果差不多,GBW也差不多,是23.2MHz稍大于stb的结果。低频相移是14度,其实在0度开始是0Hz,下降180度到-180,-103.1高于-180有76.7度,即PM值,也和stb的相差不大。

有没有发现,stb仿真环路为什么低频相位是180度而ac仿真低频相位是0度,因为stb是实打实的环路分析,在直流时,环路是负反馈,因此是180度(或者-180度)。ac分析并没有环路,相位都是从0开始,给输入一个交流,只是单纯看输出点的幅度和相位。

(2) 频率范围从0~1GHz

ac仿真的波特图

可看到0Hz时相移是0度,但是增益曲线不正常。

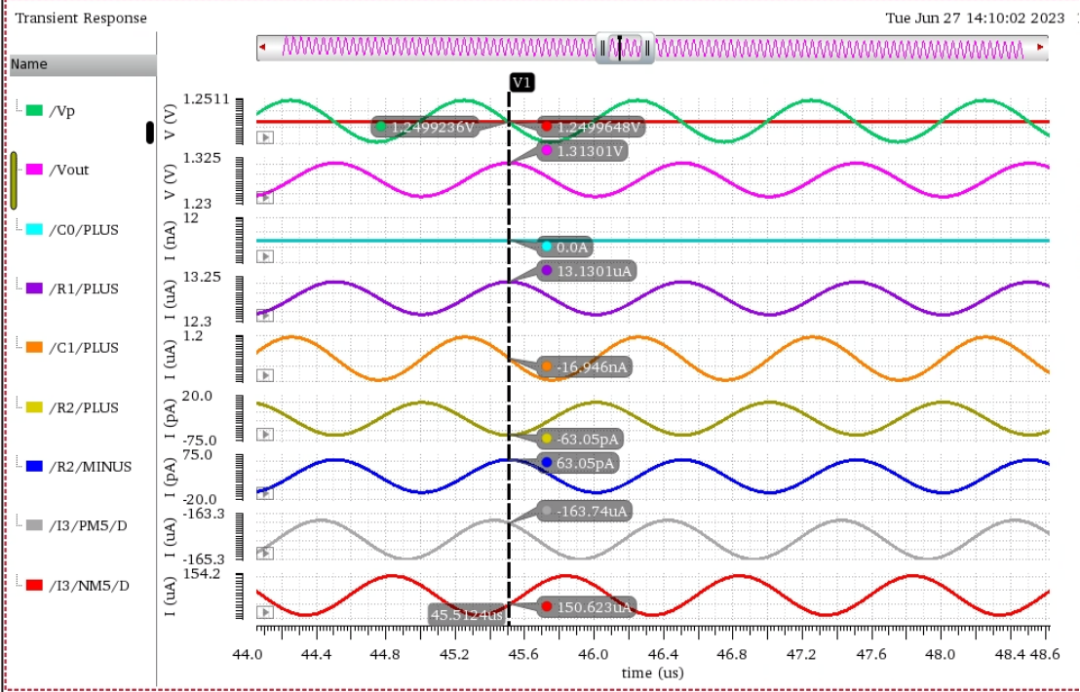

(3) tran仿真--情况1

tran仿真的testbench

Vp设置为dc=1.25V,幅度是1mV,频率是1KHz的正弦。

注:ac仿真本质上,大信号是闭环的,通过1G大电阻提供直流反馈,但是小信号还是开环的,因为1F大电容滤掉了交流小信号。

此时其实就是一个开环的状态,所以近似比较器,输出几乎是rail – rail的,电容充放电交替进行,抽电流和灌电流,net4即是Vn一端波形,Vn可看出几乎只有dc分量,Vout的共模电压和Vp的共模电压相等都是1.25V,输出的ac分量不会耦合到net4,因为1F大电容就把交流分量滤掉了,但是不完全滤掉,电容越大,纹波越小,纹波很小不会影响dc点状态就可以。

ac仿真用的不多,个人感觉不好用,原则是不是闭环应用,小信号开环,大信号闭环,单纯仿真一下放大器的低频开环增益是可以用的,进行稳定性分析一般都是闭环的,开环的电路一般不进行稳定性分析,我们一般是哪里有环路,哪里进行稳定性分析,怕振荡。stb原则是都是闭环的,因此符合实际。

可看到,运放Vn端几乎是直流,Vp是给定的正弦波,Vout输出求导的最大值M8处,对应的负载电容C1的电流最大,即M6点,可代入公式算出,即1054215pF约是533nA。C1的最小电流也是这样的求法。可看出C1充放电时间还是挺快的,这取决于运放的SR。负载电阻R1的电流就是Vout/R1,在3.28/100k=32.8uA和11mV/100k=110nA切换。

当R1电流是31.2uA时,此时Vout是3.28V,运放的第二级NMOS放大管被压入截止区,几乎无电流(约22nA),PMOS负载管被压入线性区,R1的31.2uA的电流是通过PMOS从vdd抽取的,当R1电流是110nA时,此时Vout是11mV,R1几乎不抽也不灌电流,NMOS和PMOS电流和dc时候几乎相等。

tran仿真的结果(1M正弦)

运放Vn端的放大波形(有一定纹波)

(4) tran仿真--情况2

Vp设置为dc=1.25V,幅度是1mV,频率是1MHz的正弦。

输出共模电平不是1.25,约是1.277,因为开环增益这么小已经达不到很好的直流反馈效果了,因此Vout共模点不再是1.25V。由于Vout-net4之差很小,因此C0几乎没有电流。C1只充电不放电。

1M时候的增益是36.3,下图验证了这个增益。

Vp的交流是1mV,即在1.25±1mV,Vout是1.277±36.3mV=1.241V~1.313V。36.3*1mV就是放大的小信号结果。

tran仿真的结果(1M正弦)

-

PSpice仿真运放问题2012-08-22 0

-

Pspice仿真运放的反相比例、微分电路时选用瞬态分析吗?2014-08-26 0

-

最简单的运放仿真怎么实现不了2015-06-03 0

-

用multisim13仿真实现一个“经典运放全波精密整流电路”2015-12-14 0

-

multisim仿真运放没输出2016-07-03 0

-

仿真和实际电路运放输出电压不一致2016-09-21 0

-

multisim关于运放的仿真问题2017-04-29 0

-

Multisim仿真关于运放的问题2018-07-19 0

-

请问仿真一个运放的输入失调电压是不是要做MC分析?2021-06-24 0

-

单电源运放和双电源运放分析2021-11-11 0

-

电路仿真其运放输出为什么会超过了电源电压呢2021-12-31 0

-

在PLL中的LDO进行AC仿真结果很奇怪求解答2022-06-15 0

全部0条评论

快来发表一下你的评论吧 !