讲一讲LOD效应

电子说

描述

LOD效应也是DSM效应的其中一种。DSM Effect即Deep Sub-Micron Effect,包括WPE、LOD、OSE、Hot carrier effects等等,本篇介绍LOD effect,和WPE一样,是大家经常讨论的effects。

大家知道,用于隔离器件的几种方法:整面全区氧化、LOCOS、STI。

整面全区氧化隔离在最早期使用,工艺简单,但是效率不高,占用很大面积,现在先进工艺不再使用。

后来出现了LOCOS隔离,局部氧化,优于整面全区氧化,但是有鸟嘴。

先进工艺现在多用STI浅槽隔离,工艺相对复杂,但是隔离效果好,占用面积小。

LOCOS是做的湿法氧化,STI是用的CVD工艺,CVD化学气相沉积沉积速率高,说白了就是挖出沟槽这个动作会对两侧的器件产生机械压力,因此STI会产生应力。

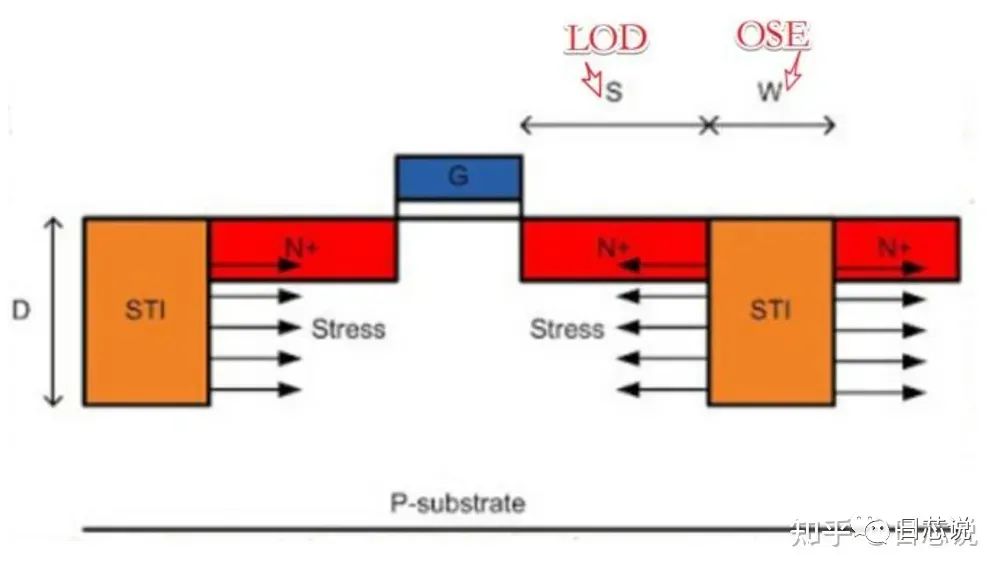

这个应力会使得STI两侧的器件特性受到影响,具体什么影响呢?这里就涉及到了LOD和OSE效应了。

LOD效应:由于STI到多晶硅栅poly的距离也就是器件有源区长度的不同,应力对器件的影响也不同,因此叫做扩散区长度效应,如下图,有源区OD的长度越大,STI对器件的应力影响越小。因此,如果想要2个MOS匹配,那么他们到STI的距离应该是一样的或者距离大到可以忽略不计LOD效应。

OSE效应:OD Space Effect,是由于STI本身的宽度不同引起的对两侧器件的应力不同。这个效应在数字IC研究居多,模拟IC主要研究LOD效应。

LOD效应和WPE效应一样,直接影响MOS管的阈值电压等参数,因此如果电路对阈值电压比较敏感,那么在layout中一定要把LOD效应考虑在内,不然layout画完再做优化就很费事,导致芯片设计周期变长。

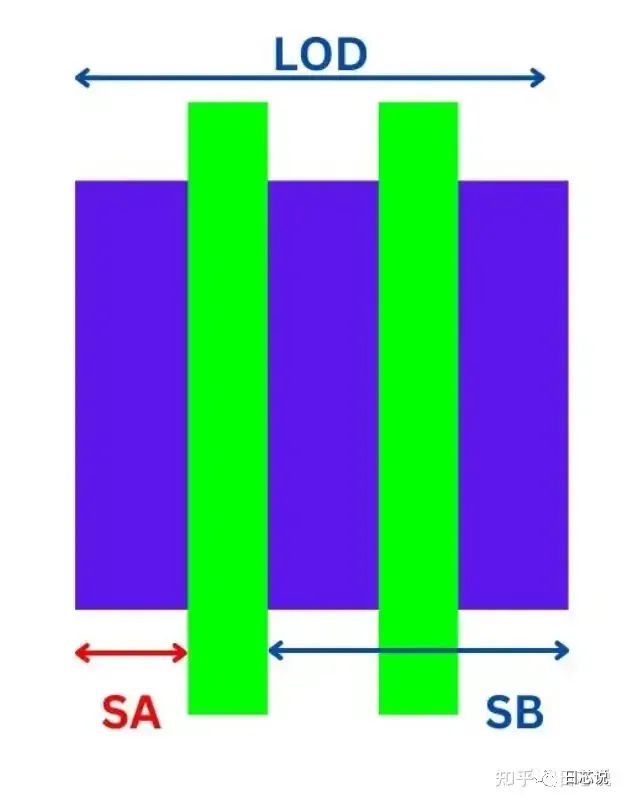

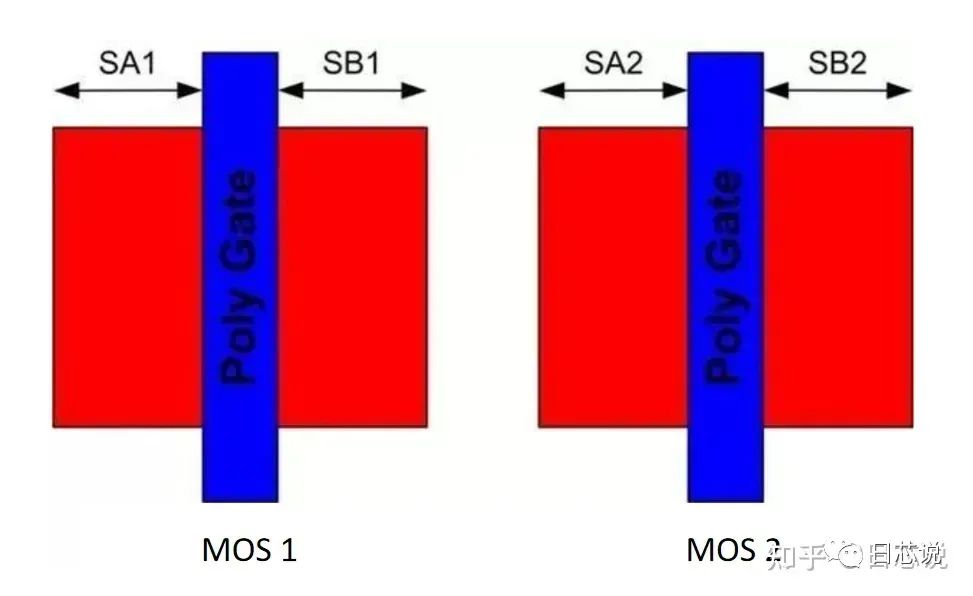

LOD效应对MOS性能影响的大小,与有源区OD的长度有关,如下图,绿色代表poly,蓝色代表OD有源区,以左侧poly为MOS管为例,SA代表源极OD长度,SB代表漏极OD长度(可互换),对于单个MOS来说,源漏极OD长度不是必须相等的。

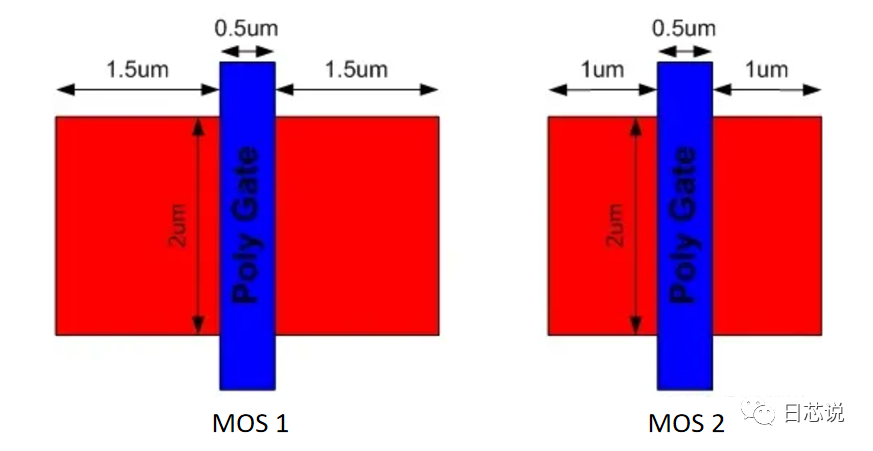

下图中,两个MOS的W都是2um,L都是0.5um,但由于左边管子MOS A的源漏的长度是SA=SB=1.5um,右边管子MOS B的源漏的长度是SA=SB=1um,那么相同尺寸的管子,由于OD长度不相等,所以流过的电流大小并不完全相等。

因此,如果想要MOS A和B做到完全匹配,那么A和B的OD长度应该做到相等才可以,即SA_A=SA_B,SB_A=SB_B。

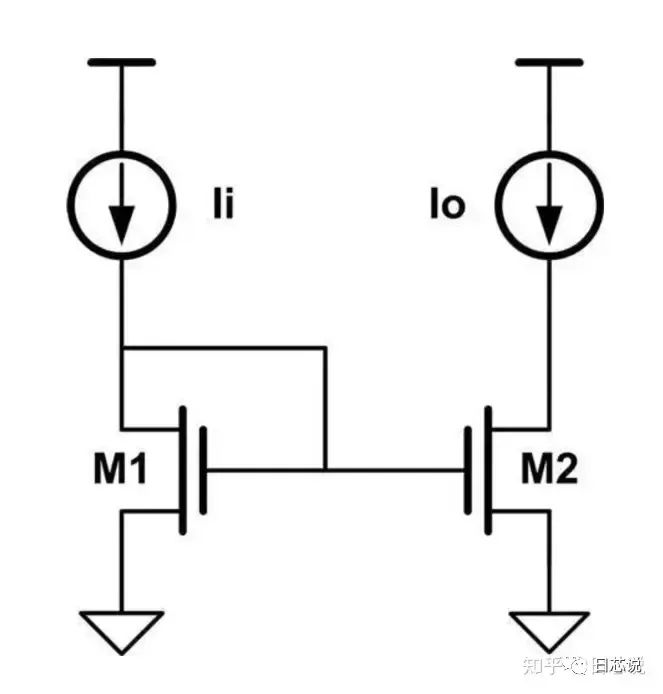

在具体的模拟IC电路中,如何考量LOD效应呢,接下来以一个简单的mirror电路为例讲解一下,以下部分笔记参考bubuchen的笔记。

以下电流镜电路,Ii是输入电流,Io是输出电流,拿到这个电路,我们第一目的是想要Ii完全等于Io,或者有整数倍的关系。

假如,我们想要Io=Ii,即M1和M2的尺寸要相等。以一个finger为例,M1和M2分开放置,不共用源漏,如下图。在layout中,我们要保证SA1=SA2,SB1=SB2,不用保证SA=SB,那么LOD效应对MOS 1和MOS 2的影响是一样的,因此M1和M2就可以做到匹配了,Io=Ii就不会因为LOD造成误差。

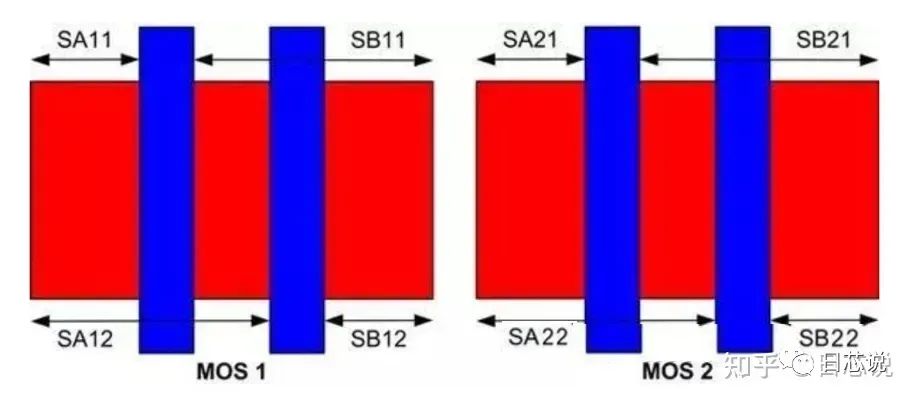

如果fingger=2会是什么情况呢?如下图,M1和M2的finger都是2,且不共用源漏,分开放置,为了使得M1和M2匹配且不受LOD影响,那么我们在版图中应该做到SA11=SA21,SB11=SB21,SA12=SA22,SB12=SB22,那么LOD对M1和M2的影响是一样的,因此M1和M2就可以做到匹配了,Io=Ii就不会因为LOD造成误差。

所以当我们要设计Io=Ii时,,不论是Single Finger或是Multi Fingers,我们主要保证MOS 1和MOS 2的Layout一模一样即可避免LOD Effect所造成的Mismatch,即使MOS 1和MOS 2画在同一块OD也是如此。

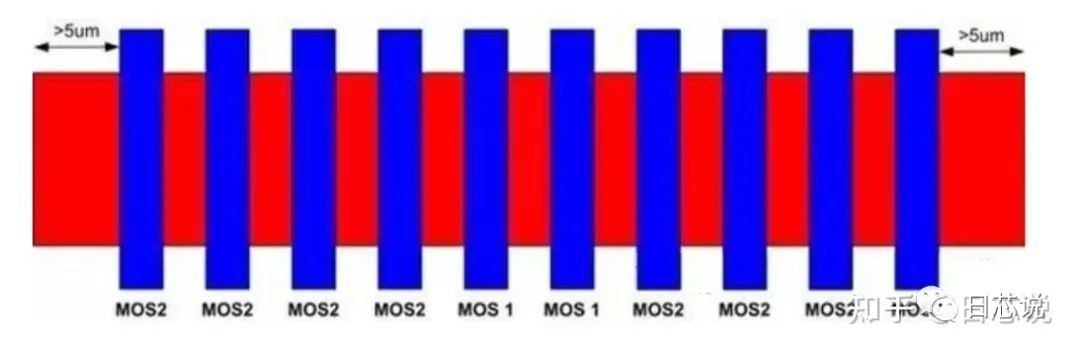

如果我们想要做到Io=4Ii,且是多个finger的情况,在画版图的时候,为了节省面积,在电路图源漏有短接的,在版图中也会源漏共用。在这个电流镜电路中,M1和M2的源端是短接的,因此在版图中也是共用源端。

假设工艺要求中OD长度大于5um以上即可忽略LOD效应,那么如下图,M1的finger是2,M2的finger是8,这样做到了1:4的比例,且所有的finger的poly到STI的距离(即所有的OD长度)均大于5um,可以忽略LOD效应。

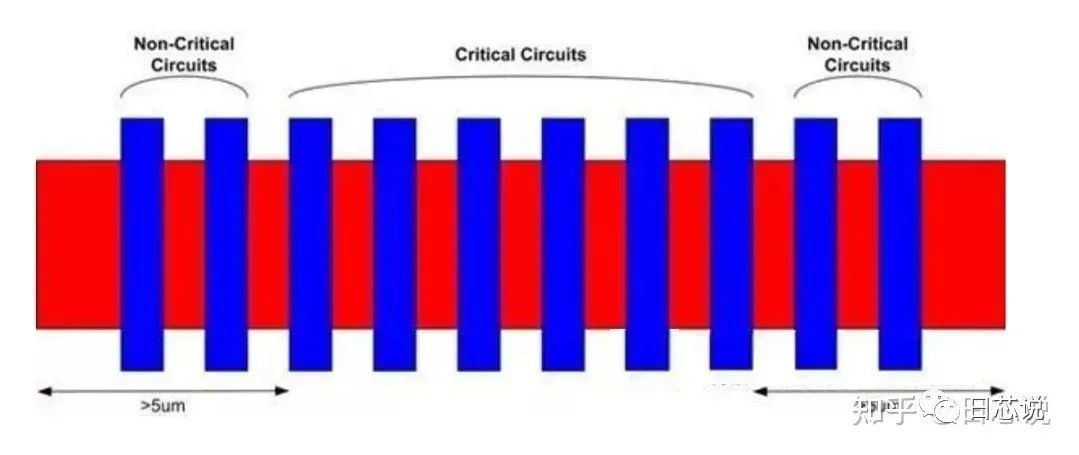

实际画版图时,管子两侧会放置dummy,这样要保证了OD的长度够长,且做到很好的匹配。

有同学会问了,两侧做到5um以上会不会太浪费面积,为什么1:4的比例不做成1:4而是2:8呢?能否做1:4呢?接下来分析这个问题。

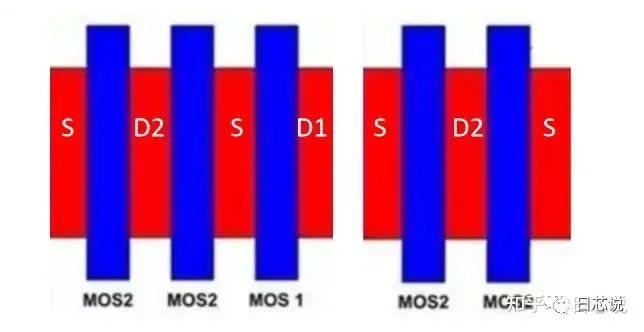

如果做成2:8的比例,即使两侧OD长度不大于5um,那么在两侧放上dummy,其实这时候LOD效应已经很小了,这种放置dummy的方法,如果采用1:4的比例,即M1的finger是1,M2的finger是4,那么版图中会是以下的样子,S代表M1和M2的源端,D1代表M1的漏端,D2代表M2的漏端。即使两侧放了dummy,LOD效应在M1和M2的影响也是不一样的,因此不是完美的1:4的比例了。

-

数采达人第一讲2012-09-13 0

-

FPGA入门公益学习班第一讲精彩回放2013-04-16 0

-

社团崛起之搞定51单片机(第一讲)2014-03-29 0

-

请大神给我讲一讲DCM和CCM的在实际应用中的作用2016-11-18 0

-

高频功率磁性材料特性与应用(第一讲 +第二讲)2018-05-04 0

-

讲一讲嵌入式技术2021-12-21 0

-

讲一讲三大运营商的物联网卡选择哪个比较合适2022-01-12 0

-

讲一讲高级定时器的死区时间是怎么算出来的2022-01-12 0

-

简单讲一讲PCB Layout的设计要点2022-02-22 0

-

讲一讲在FatFs文件系统下读取SD卡的该如何做2022-03-02 0

-

讲一讲generate的用法2022-09-29 0

全部0条评论

快来发表一下你的评论吧 !