SD NAND在PCB上的布局和走线要求

描述

1、SD NAND的布局

SD NAND 芯片最好是要靠近host,这样可以让走线尽可能的短,减少干扰。

在布局的时候需要尽量避免离host过远,距离太远会导致走线过长,容易受到干扰。

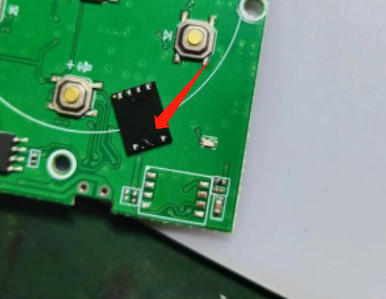

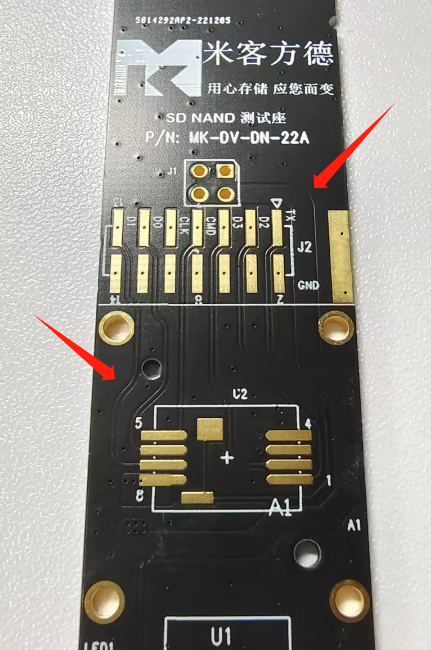

另外,在布局的时候,SD NAND芯片不能放在PCB边缘,这样容易导致焊盘脱落,如下图:

上图就是芯片放在PCB边缘,分板和拆板的时候,芯片受到外力导致的焊盘脱落。

2、SD NAND在PCB上的走线要求

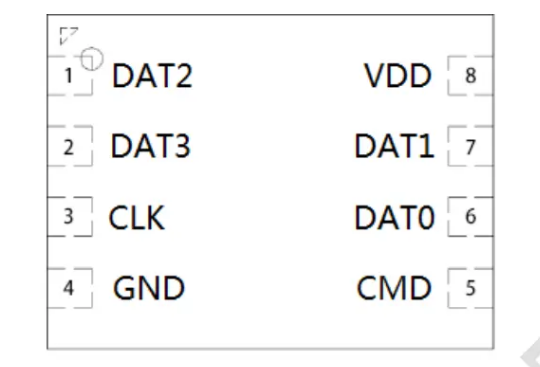

SD NAND一般有8个引脚,

1、VDD和GND的电源走线要求回路尽可能的短,走线需要远离电感,以防止电磁干扰,另外,SD NAND的电源走线宽度需要能过至少300mA的电流。

2、DAT0 ~ DAT3四个数据引脚,如果是emmc,则要求长度不能超过7mm,并且要等长走线。而在SD NAND里面,走线长度在15 ~ 18mm左右,当然这个走线是越短也好,在一些要求比较高的情况下,四根DATD数据线可以等长走线,如下图:

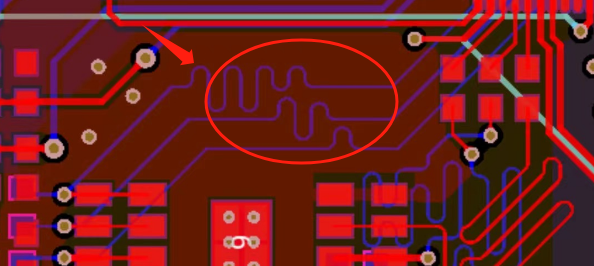

3、CMD和CLK的走线是要求越短越好,并不要求走等长线,像下图中的这种为了强行等长走线而使CLK走线过长是不支持的,这样容易会增加CLK受干扰概率。

3、弧度走线

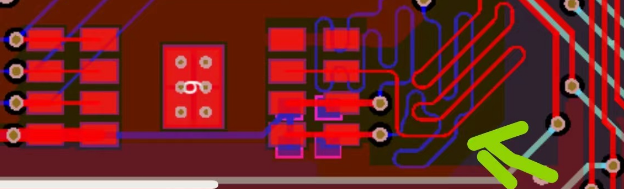

在做一些SD NAND转接板的时候,走线比较长,是要求弧度走线的,如下图:

这个是MK-米客方德做的一款SD NAND 转接板,方便测试芯片,板子的走线全部采用的是弧度走线,

实际上存储行业信号线都要拉弧度处理。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PCB 布局、走线资料2014-08-02 0

-

信号在PCB走线中传输时延 (上)2014-10-21 0

-

请教一下各位pcb板上电源部分布局和走线的有哪些要点哦2014-10-24 0

-

开关电源的PCB设计(布局、排版、走线)规范2015-05-21 0

-

射频线PCB走线屏蔽孔,都有什么要求???2016-01-13 0

-

ddr2和nand走线2016-10-10 0

-

pcb布局,走线方面2016-10-15 0

-

主板的走线和布局设计解读2018-11-23 0

-

pcb蛇形走线2019-05-22 0

-

PCB布局和走线的调整2019-10-17 0

-

电源PCB设计指南:整体布局及走线原则2020-08-01 0

-

电源布局/网口电路/音频走线的PCB设计2021-03-04 0

-

PCB布局之蛇形走线2022-12-27 0

-

在PCB布局走线时CAN需要差分等长线吗?2023-04-07 0

-

PCB走线的设计细节详解2023-04-13 0

全部0条评论

快来发表一下你的评论吧 !