什么是DRP?DRP是如何工作的?

处理器/DSP

描述

什么是DRP?

DRP全称是Dynamically Reconfigurable Processer,即动态可重配置处理器。是瑞萨独创的体系结构,能够动态的调整硬件运算单元的逻辑电路,也能够从软件层面对运算逻辑进行实时修改,保证了灵活性的同时也拥有不俗的图像处理能力。当前,DRP技术已迭代至第三代,并配套开发了一系列相关算法及工具链,免费提供客户参考及使用。

第一代DRP技术被应用在入门级的RZ/A2M MPU等产品中,使其拥有出色的AI及图像加速能力。以下内容,均是基于第一代DRP技术展开介绍的。

DRP如何工作?

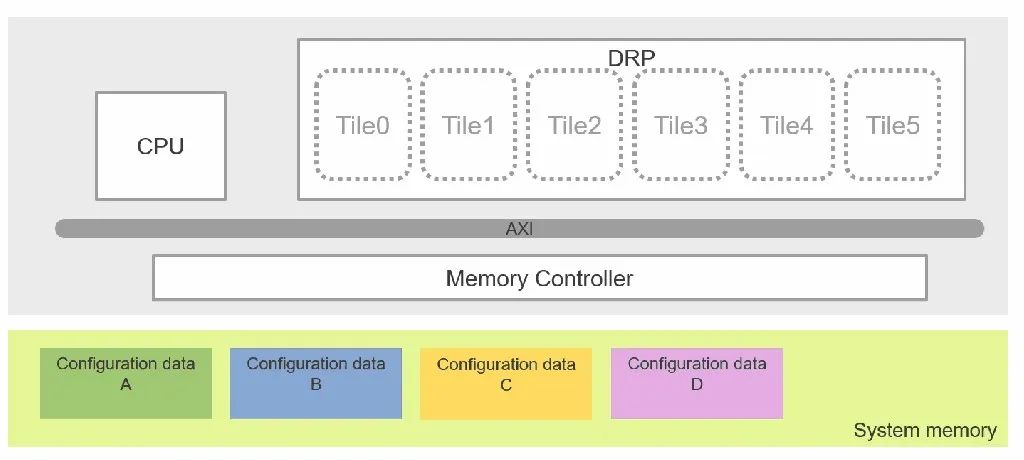

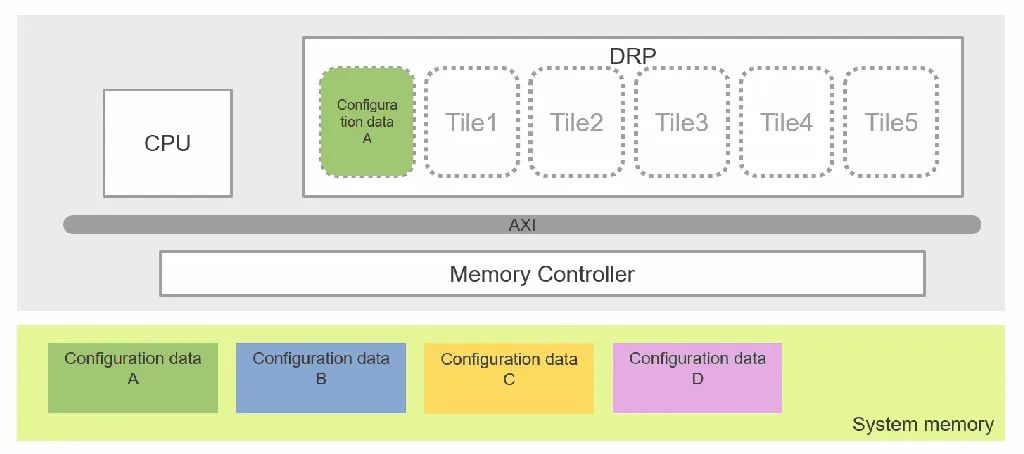

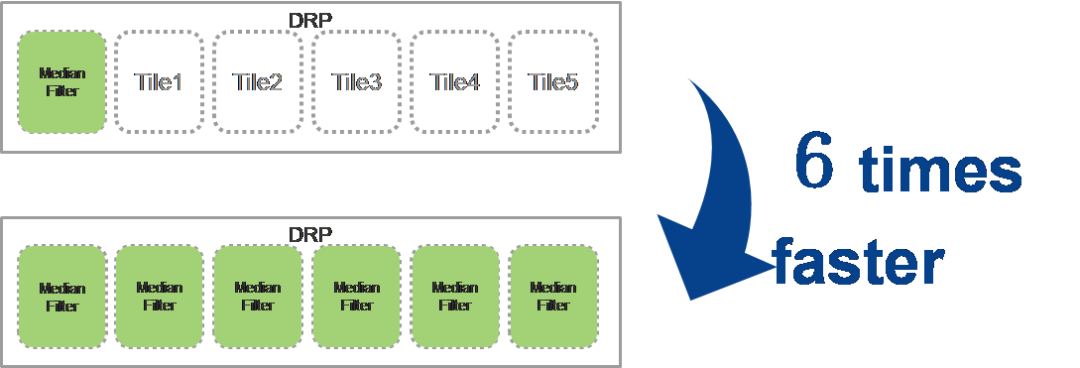

DRP有6个独立的单元称为“Tile”,它们可以加载多个配置数据(即算法库)并且并行的执行,这些算法库存放在系统内存中,在需要的时候由CPU下发指令将其加载到各个Tile中。

任何时候都可以修改各个Tile中的算法库,并且在修改过程中不会影响其它Tile的运行。

DRP采用动态加载的方法可以在极小的硬件资源上实现应用对不同图像处理算法高速处理的需求。

“

DRP凭什么这么优秀?

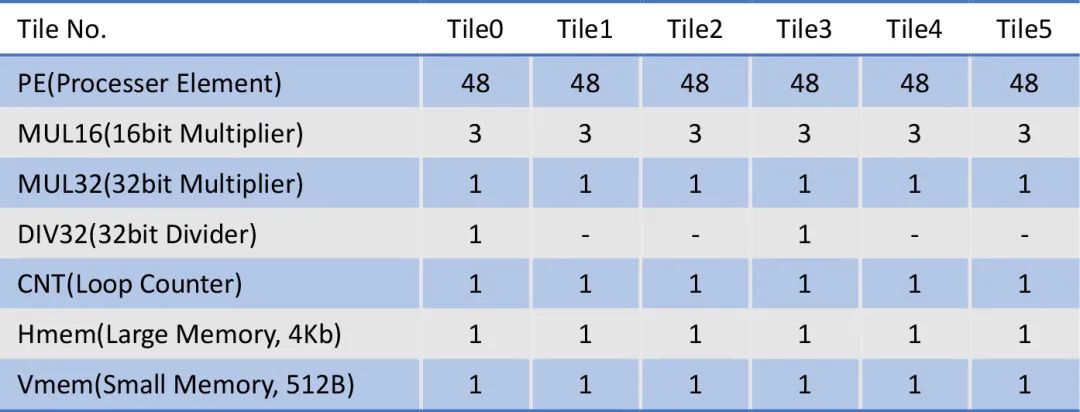

DRP是一个硬件资源,所有的运算逻辑都在硬件层面实现,每个Tile都是一个独立的运算单元,Tile拥有的硬件资源是一定的,所以当有算法库用到的硬件资源较多的时候,就需要两个甚至更多的Tile来协同配合,以下是DRP所拥有的硬件资源。

DRP在运行的过程中,会自动的根据算法库的复杂程度,灵活的对硬件资源进行一些整合,比如在一个Tile内,将两个16bit的乘法器合并成一个32bit的乘法器使用;或者将一个16bit的乘法器与一个计数器组合使用等。进一步扩大了DRP的运算能力。

硬件的运算能力我们都非常清楚,比如目前应用非常广泛的FPGA的算力就和CPU完全不在一个量级,然而FPGA的缺陷也很明显,就是运算规模直接和门电路数量挂钩,需要实现复杂的算法就必须用更多的门数,而且一旦算法要求的门数超出了项目初期的FPGA选型,则不得不更换更大规模的FPGA,非常的不方便。

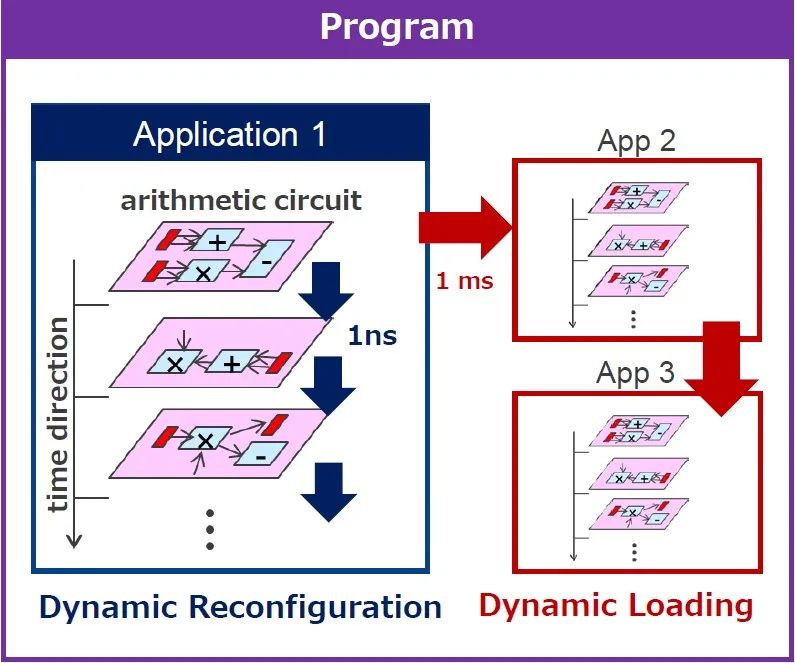

这个时候,DRP的灵活性就体现出来了,它不仅可以在库与库之间灵活切换,在同一个库的内部,也能在不同的时钟周期内,动态调整运算电路之间的逻辑,来实现各种各样的运算方式。通过这种分时复用的方式,最大限度的提升了运算性能,给小体积发挥大能力提供了无限可能。

动态可重配置的性能可以在1ns内修改运算电路的组合方式,动态加载可以在1ms内重新装载整个新的算法库。

DRP甚至可以通过多个Tile运行同一个算法库来提高处理速度。比如将一张图片等分为6份,交给6个Tile进行图像处理,性能直接在原有的基础上提升6倍!

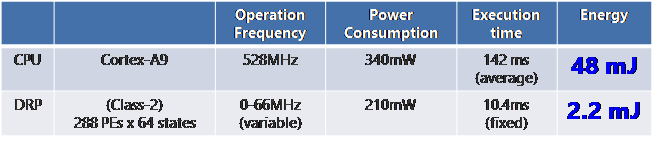

一般来说,性能提升往往会伴随着功耗的增加。但是用DRP来提升图像处理能力是一种另辟蹊径的优化方式,而且这种方式的能耗要远远低于CPU的能耗。

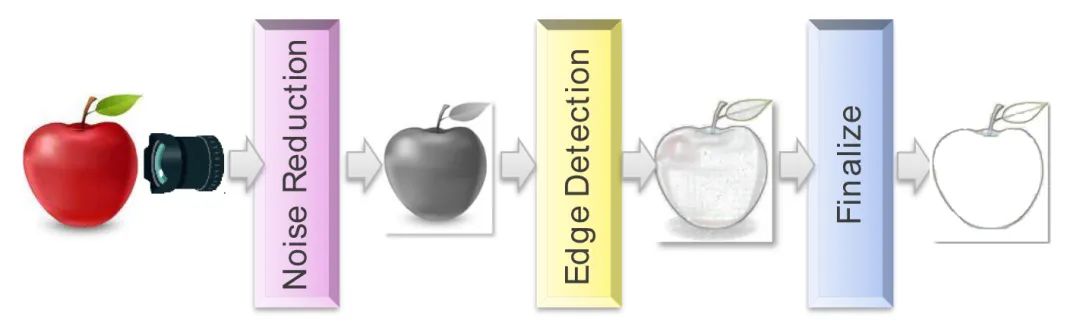

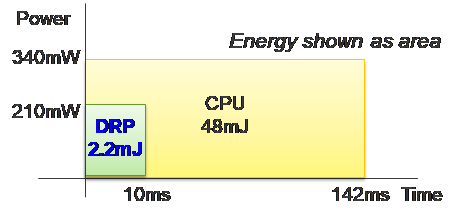

我们使用RZ/A2M这款芯片的CPU和DRP分别运行Canny Edge Detection并测量了这两种情况下的性能与能耗。

Canny Edge Detection拢共分三步:

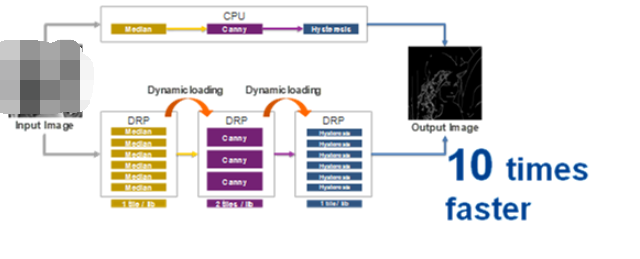

这一连串的流程,交给CPU去做,耗费了142ms左右的时间,但是如果交给DRP做,只需要10.4ms!其中还包含了不同DRP库之间切换的时间!

除了速度上的优势,能耗方面的优点也非常明显:

对比发现DRP不仅在运算速度上提升了14倍,在功耗上也只用了CPU的1/20。

以上,是第一代DRP技术特点的介绍,后续还有关于DRP技术的相关应用及最新的DRP技术介绍,敬请期待!

编辑:黄飞

-

请问CCG7端口可以用作DRP吗??2024-02-23 0

-

基于USB-C DRP的移动电源参考设计包括BOM及层图2018-09-03 0

-

DCM DRP并在运行时重新配置DCM freq2019-02-26 0

-

请问如何初始化PLL_WITH_DRP?2020-08-26 0

-

pads layout 在drp时软件卡死2022-08-22 0

-

DRP型应变式差压传感器及变送器的研制2009-01-12 674

-

RZ/A2M DRP实现二维码编码格式的快速检测2022-04-29 1362

-

RZ/A2M 集团 DRP 驱动程序用户手册2023-02-02 145

-

RZ/A2M 集团 DRP 库用户手册2023-02-02 142

-

DFP、DRP和UFP分别是什么?2023-10-27 2914

-

动态反向脉冲(DRP)实验2023-11-21 803

-

RZ/V2L DRP-AI支持包版本.7.41发布说明2024-02-01 72

-

DRP芯片在多个领域的应用2024-04-13 192

全部0条评论

快来发表一下你的评论吧 !