简单介绍硅通孔(TSV)封装工艺

描述

在上篇文章中介绍了扇入型晶圆级芯片封装(Fan-In WLCSP)、扇出型晶圆级芯片封装(Fan-Out WLCSP)、重新分配层(RDL)封装、倒片(Flip Chip)封装,这篇文章着重介绍硅通孔(TSV)封装工艺。

硅通孔封装工艺

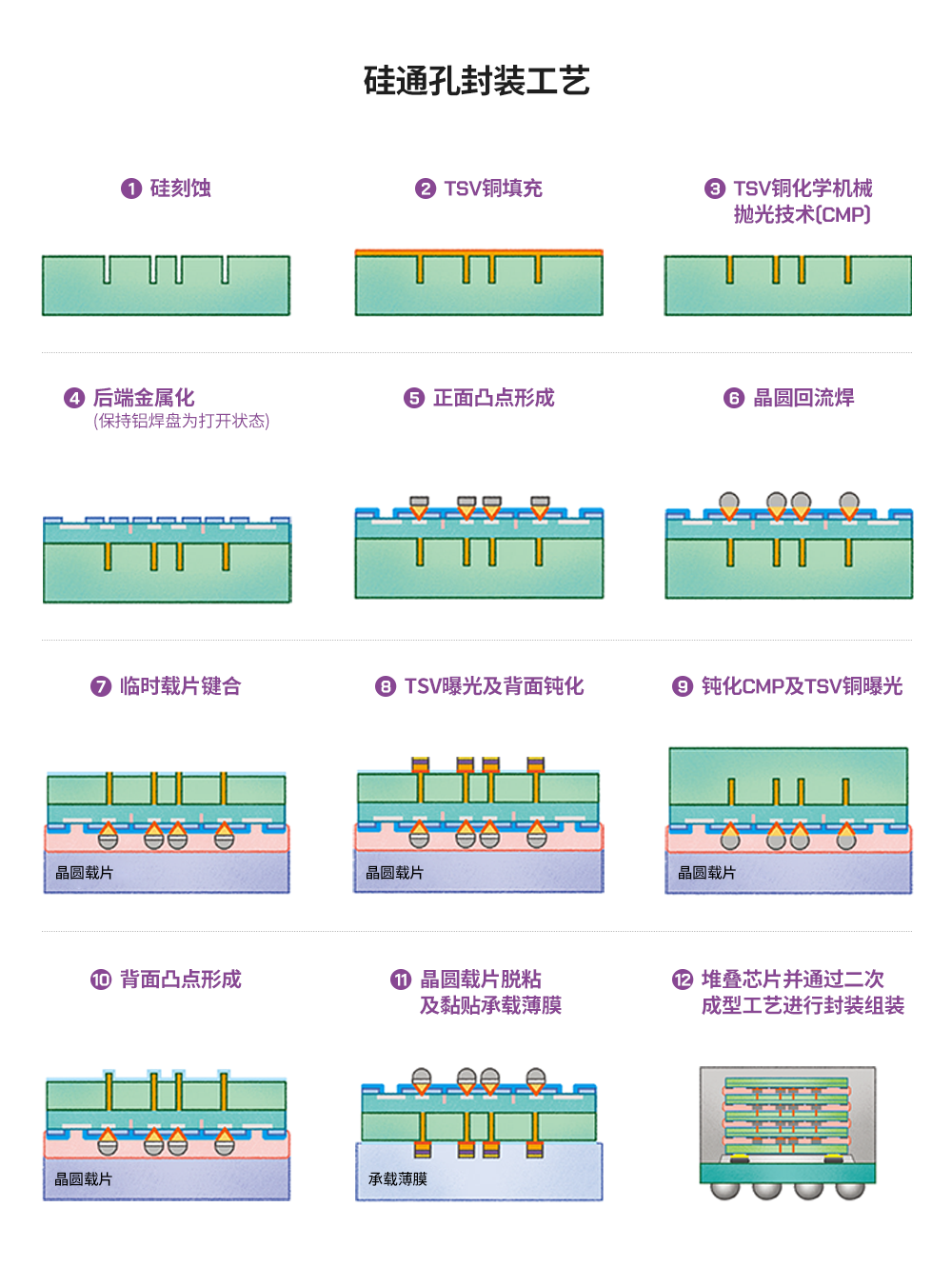

图6展示了采用中通孔(Via-middle)5方法的硅通孔封装工艺步骤。首先在晶圆制造过程中形成通孔。随后在封装过程中,于晶圆正面形成焊接凸点。之后将晶圆贴附在晶圆载片上并进行背面研磨,在晶圆背面形成凸点后,将晶圆切割成独立芯片单元,并进行堆叠。

5中通孔(Via Middle):一种硅通孔工艺方法,在互补金属氧化物半导体形成后及金属层形成之前开展的工序。

接下来,将简单概括中通孔的基本工序。首先在前道工序(Front-end of Line)中,在晶圆上制作晶体管,如互补金属氧化物半导体等。随后使用硬掩模(Hard Mask)6在硅通孔形成区域绘制电路图案。之后利用干刻蚀(Dry Etching)工艺去除未覆盖硬掩膜的区域,形成深槽。再利用化学气相沉积工艺(Chemical Vapor Deposition)制备绝缘膜,如氧化物等。这层绝缘膜将用于隔绝填入槽中的铜等金属物质,防止硅片被金属物质污染。此外绝缘层上还将制备一层金属薄层作为屏障。

6硬掩膜(Hard Mask):一种由硬质材料而非软质材料制成的薄膜,用于绘制更为精细的电路图案。硬掩膜本身对光线并不敏感,所以需使用光刻胶才能进一步绘制电路图案,以最终实施刻蚀工艺。

此金属薄层将被用于电镀铜层。电镀完成后,采用化学机械抛光(Chemical Mechanical Polishing)技术使晶圆表面保持平滑,同时清除其表面铜基材,确保铜基材只留在沟槽中。然后通过后道工序(Back-end of Line)完成晶圆制造。

▲图6:硅通孔封装工序(ⓒ HANOL出版社)

使用硅通孔技术制造芯片堆叠封装体时,一般可采用两种类型的封装方法。第一种方法是利用3D芯片堆叠技术的基板封装。第二种方法则需创建KGSD,然后基于KGSD来制作2.5D或3D封装。下文将详细介绍如何创建KGSD,以及如何基于KGSD来制作2.5D封装的过程。作为利用硅通孔技术制作而成的芯片堆叠封装体,制作KGSD必需经历额外封装工艺,如2.5D封装、3D封装以及扇出型晶圆级芯片封装等,高带宽存储器(HBM)就是KGSD产品的一个典型例子。由于KGSD需经历额外封装工艺,其作为连接引脚的焊接凸点需要比传统锡球更加精细。因此3D封装体中芯片堆叠在基板上,而KGSD中的芯片则堆叠于晶圆上方,晶圆也可以视为KGSD的最底层芯片。就HBM而言,位于最底层的芯片被称为基础芯片或基础晶圆,而位于其上方的芯片则被称为核心芯片。

此方法工序如下:首先,通过倒片工艺在基础晶圆和核心晶圆的正面制作凸点。在制作2.5D封装体时,基底晶圆需要排列凸点,使之能够附着到中介层(Interposer);相反,核心晶圆上的凸点布局则是有助于晶圆正面的芯片堆叠。在晶圆正面形成凸点后,应减薄晶圆,同时也需在晶圆背面形成凸点。然而,正如前文在介绍背面研磨工艺时所述,需注意在减薄过程中导致晶圆弯曲。在传统封装工艺中,进行减薄之前,可将晶圆贴附到贴片环架上,以防止晶圆弯曲,但在硅通孔封装工艺中,由于凸点形成于晶圆背面,所以这种保护方法并不适用。为解决此问题,晶圆承载系统(Wafer Support System)应运而生。利用晶圆承载系统,可借助临时粘合剂将带有凸点的晶圆正面贴附于晶圆载片上,同时对晶圆背面进行减薄处理。此时晶圆贴附于晶圆载片上,即使经过减薄也不会发生弯曲。

此外,因晶圆载片与晶圆形式相同,因此也可使用晶圆设备对其进行加工。基于此原理,可在核心晶圆的背面制作凸点,当核心晶圆正面及背面上的凸点均制作完成时,便可对载片进行脱粘。随后将晶圆贴附于贴片环架中,并参照传统封装工艺,对晶圆进行切割。基础晶圆始终贴附于晶圆载片上,从核心晶圆上切割下来的芯片则堆叠于基础晶圆之上。芯片堆叠完成后,再对基础晶圆进行模塑,而后进行晶圆载片脱粘。至此,基础晶圆就变成了堆叠有核心晶圆的模制晶圆。随后对晶圆进行研磨,使其厚度达到制作2.5D封装体所需标准,然后再将其切割成独立的芯片单元,以制作KGSD。HBM成品包装后将运送至制作2.5D封装体的客户手中。

审核编辑:汤梓红

-

pcb封装工艺大全2012-03-14 0

-

晶圆凸起封装工艺技术简介2011-12-01 0

-

芯片封装工艺详细讲解2016-06-16 0

-

【PCB封装工艺】低温低压注塑2018-01-03 0

-

封装工艺的品质check list 有吗(QPA)?2018-04-21 0

-

硅通孔(TSV)电镀2021-01-09 0

-

PCB生产商的通孔插装工艺模板的印刷方法有几种?2023-04-06 0

-

芯片封装工艺流程-芯片封装工艺流程图2008-05-26 7440

-

“封装工艺员”课程详细介绍2010-11-16 703

-

新型封装工艺介绍2011-12-29 983

-

透明封装工艺简介2021-12-15 1862

-

IGBT功率模块封装工艺介绍2022-06-17 2355

-

金属封装工艺介绍2023-04-21 2718

-

硅通孔封装工艺流程与技术2023-05-08 2224

-

半导体后封装工艺及设备2023-07-13 667

全部0条评论

快来发表一下你的评论吧 !