IC设计必须关注的时钟抖动

电子说

描述

时钟抖动是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动,可以用抖动频率和抖动幅度对时钟抖动进行定量描述。通常希望一个周期性波形(特别是时钟)跨过特定门限的时间非常精确,与该理想值的偏差称为抖动.

时钟的抖动可以分为随机抖动(random jitter,简称rj)和固有抖动(deterministic jitter),随机抖动的来源为热噪声、shot noise和flick noise,与电子器件和半导体器件的电子和空穴特性有关,比如ecl工艺的pll比ttl和cmos工艺的pll有更小的随机抖动;

固定抖动的来源为:开关电源噪声、串扰、电磁干扰等等,与电路的设计有关,可以通过优化设计来改善,比如选择合适的电源滤波方案、合理的pcb布局和布线。

在通信网络、无线传输、CPRI和SONET等高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。

在数字系统中时钟边沿决定了每个基本单元的开始和结束时间。当抖动改变了时钟边沿从而导致时钟周期变化时,每个基本单元的有效工作时间也会发生变化,可能会导致信号的建立时间和保持时间不能满足要求,从而影响电路的正常工作。

当使用Serdes发送或者接收串行bit流时,时钟是用于对传输的数据进行编码,并将时钟信息嵌入到传输的数据中。接收器会从传输的比特流中分离出单独的时钟,用于对数据进行采样和捕捉。在该系统中累计抖动决定了bit到达与采样之间的时间差,因此它是最重要的。

在模数转换器(ADC)和数模转换器(DAC)中,对信号的采样可以转换为信号与时钟时域乘积。

时钟决定了信号采样时间,如果时钟抖动导致采样时间偏离了理想采样时间,会导致采样到的信号值相比于理想的信号值发生变化,从而恶化信噪比和动态范围,降低转换器的有效分辨率。

抖动可以通过许多方式测量(不同方式测量到的抖动被分别加以定义),以下是主要的抖动分类:周期抖动(Period Jitter);相邻周期间的抖动(Cycle to Cycle Period Jitter);长时间抖动(Long Term Jitter);相位抖动(Phase Jitter);单位时间间隔抖动(TIE,Time Interval Error)。

周期抖动是时钟信号的实际周期长度与理想周期长度之间的偏差,测量样本为数目不定(随机)的一组周期。如果给定一定数目的单个时钟周期,我们就可以通过测量每个周期的长度并计算平均的周期长度,以及这些时钟周期的标准差和峰峰值。

相邻周期抖动,根据 JEDEC 标准 65B,是通过一定数量的相邻周期随机样本的计算得出相邻周期的时间变化。JEDEC 标准进一步规定:每个样本的大小应大于或等于 1,000。相邻周期抖动一般体现为以ps为单位的峰值,用于定义任意两个连续时钟上升沿之间的最大偏差。

此类型的抖动规范常用于体现扩频时钟的稳定性,因为周期抖动对频率扩展特性更加敏感,而相邻周期抖动则不然。时间间隔误差 (TIE) 是指实际信号的事件边沿时间点相对于理想信号的事件边沿时间点的时间偏差。实际上,TIE 是相位噪声频谱在时域离散信号序列的表达,以秒或 ps 为单位。理想信号通常是信号处理软件利用对实际信号周期的平均估算而得到的参考信号。

为成功地设计高速数字系统,不仅需要理解什么是抖动,计算抖动的大小,还需要对不同的抖动分量进行隔离和分解,分析造成抖动的原因,进而避免在高速系统中出现抖动造成的系统故障。在了解抖动测试前,明智选择合适的抖动测试工具和方法成为整个抖动测试工作的第一步。

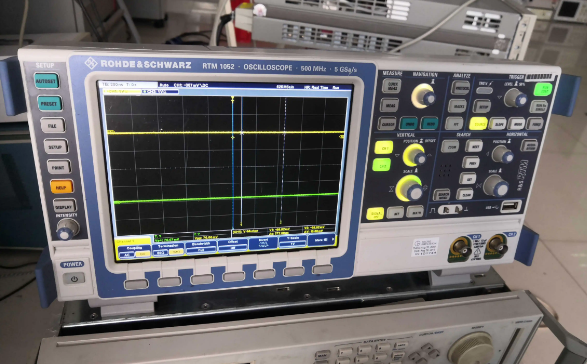

目前有几种抖动测试工具可供选择,误码仪(BERT)直接测试系统的误码率,但是价位昂贵,功能单一,不适合设计人员和调试人员;采用时间间隔分析仪测试抖动也存在功能单一,抖动分析能力不足的限制。高性能数字示波器成为当前最流行的抖动测试工具。示波器采样系统中定时元件的稳定性直接影响着定时测量精度。

如果时基有误差,那么基于该时基进行的测量会具有同等或更大的误差。示波器中的时基稳定性包括参考时钟、倍频器、计数器等相关电路的稳定性。当通过实时采集模式进行抖动测试时,由于示波器工作在单次触发模式,连续实时采集所有信号,所以它不受仪器多次触发带来的触发抖动影响。

另外两个误差源分别是ADC孔径不确定性和量化误差。这些误差可以表现为幅度噪声和定时噪声,具体取决于取样数据使用的方式。很难区分该误差的实际来源,因为模数转换的时间不同。

抖动测试时不仅需要对示波器整体性能进行评估,例如示波器的带宽,采样率,还需要与之匹配的高采样率下的采集内存长度,这样才能测量从接近DC直流到仪器带宽的抖动,同时保持各种相位和谐波关系,对被测信号的抖动有一个全面的分析。

时钟抖动是设计中常见的问题,可能对系统的性能和可靠性产生负面影响为了减少时钟偏差和抖动,我们需要选择高质量的时钟源,加强时钟同步与校准,降低电磁干扰和噪声,控制温度变化,优化时钟电路设计,以及使用时钟补偿技术通过遵循这些设计指导原则,可以提高系统的时钟准确性和稳定性,确保系统的性能和可靠性。

-

超低抖动时钟的产生与分配2021-04-18 423

-

时钟抖动使随机抖动和相位噪声不再神秘2022-11-07 275

-

微控制时钟抖动如何改善?2020-08-19 0

-

高速ADC的低抖动时钟设计2009-11-27 543

-

高速互联链路中参考时钟的抖动分析与测量2010-04-15 371

-

理解不同类型的时钟抖动2010-01-06 1659

-

时钟抖动时域分析(下)2012-05-08 606

-

ADI推出完全可编程的抖动衰减双路时钟转换器IC--AD95592012-08-03 1058

-

ADI推出业界最低抖动RF时钟IC AD95252012-11-02 1204

-

时钟抖动的基础2017-04-01 853

-

时钟抖动时域分析 第 3 部分2017-10-26 661

-

时钟抖动解秘—高速链路时钟抖动规范基础知识2022-11-07 329

-

时钟抖动的影响2023-03-10 687

-

时钟抖动的几种类型2023-06-09 1332

-

时钟偏差和时钟抖动的相关概念2023-07-04 1104

全部0条评论

快来发表一下你的评论吧 !