Power Good信号的使用方式

描述

引言:诸如微处理器或系统芯片(SoCs)的敏感负载需要保持稳定的输入电压。如果电压轨有大量的涌流或施加高电容负载,电压可能会下降,导致设备进入欠压锁定(UVLO)/复位状态或损坏下游电路。PGOOD信号可以通过连接信号到下游负载来帮助管理冲击电流或控制电源时序,只有当电压轨达到足以正常运行的值时,才会发出PGOOD。将下游启用引脚或复位监控器连接到PGOOD,以确保下游负载仅在稳定的输入电压下工作,PGOOD功能也适用于功率排序和功率多路复用等应用。

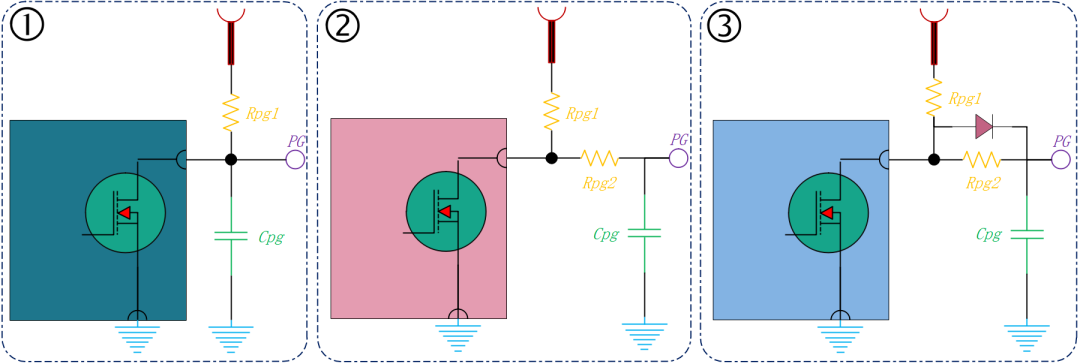

- PGOOD信号的使用方式

连接到下游负载

许多系统正常运行的负载需要稳定的、可调节的功率输入,如果电源轨失调,可能导致系统故障,一些依赖于稳定的电压轨的下游负载包括MCU、FPGA、SOC和其它敏感组件。

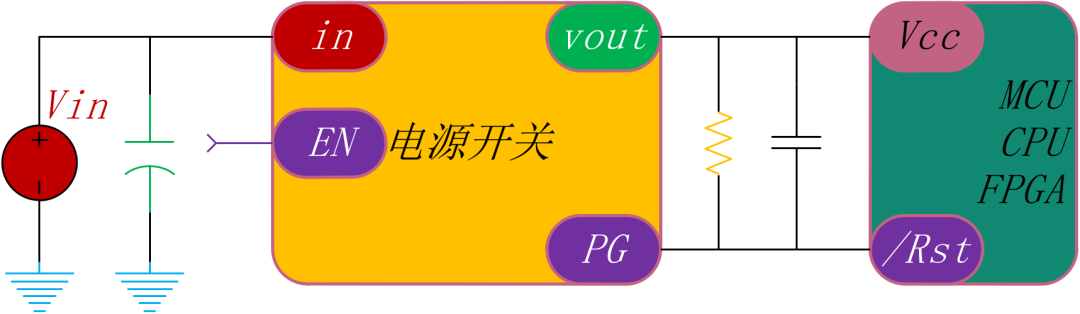

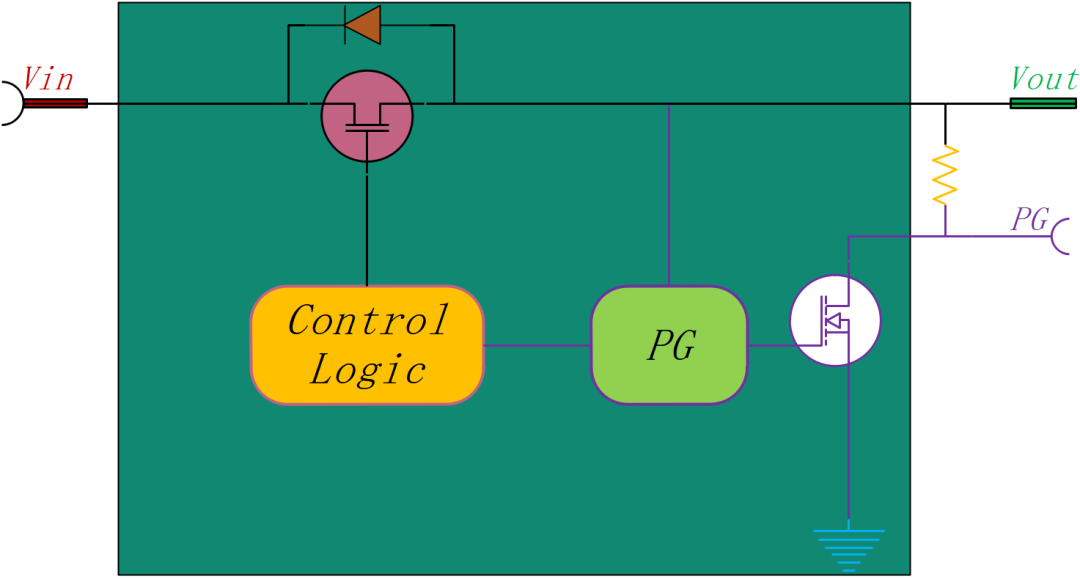

如图10-1所示,当电源轨打开且稳定时,PGOOD信号可以向MCU提供反馈。如果电源开关的输出包含高电容性负载,则在输出电压稳定时才会打开单片机,浪涌电流可以得到有效控制。换句话说,当PGOOD信号不指示时,单片机将保持关闭状态。由于PGOOD的输出通常是开漏,需要一个上拉电阻,以在调节期间将引脚拉高。

图10-1:电源-PG的复位配置

电源轨逻辑

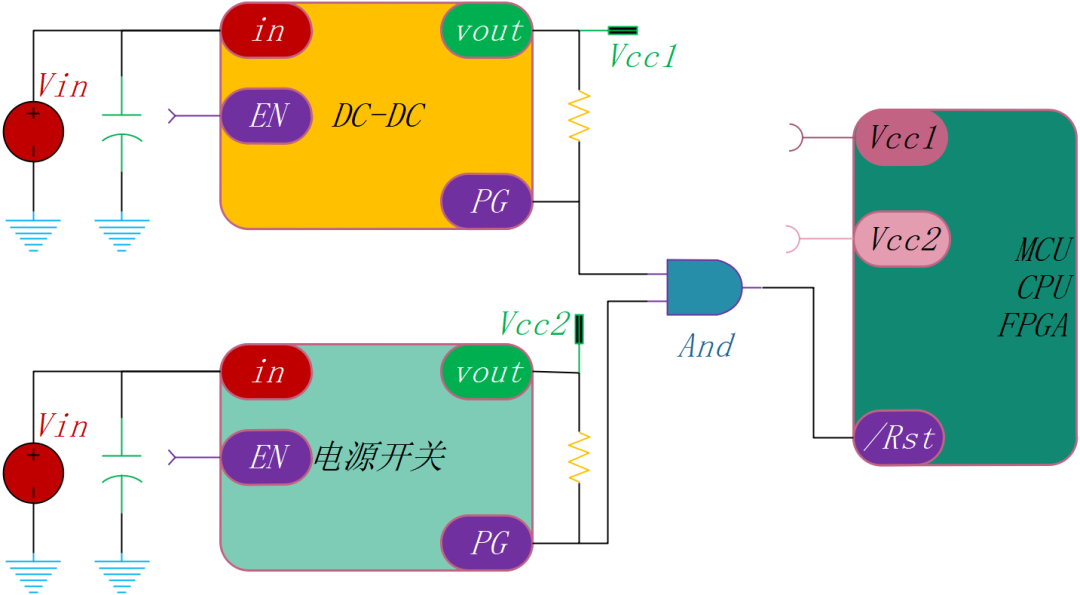

如果多个电源轨需要调节,将PGOOD信号一起连接到重置监控器或IC可确保在任何电源轨超出调节范围时重置信号有效。图10-2通过将DC-DC转换器的PG和电源开关连接在一起演示了这种功能。

图10-2:多电源PG复位配置

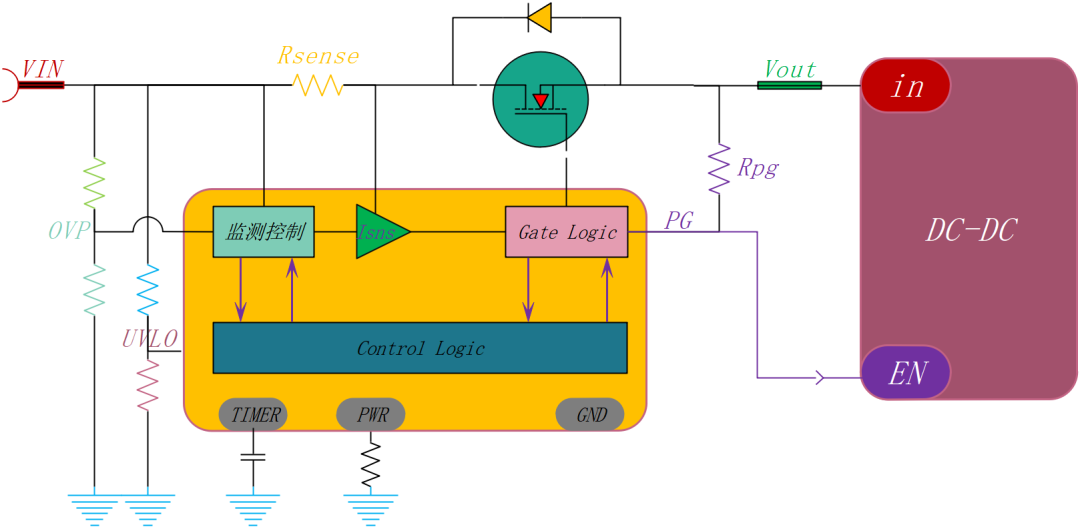

输入保护

需要鲁棒输入保护的系统可以使用PGOOD信号来减少启动期间的系统压力,一些设备,如热插拔控制器,监测外部FET上的应力,使其保持在安全操作区(SOA)内。在启动期间使下游负载导通,而FET没有完全导通可能会在外部FET和系统上增加额外的应力。将PGOOD信号连接到下游负载的使能信号,如图10-3所示

图10-3:热插拔电源-PG的配置

2.电源时序

许多应用需要控制上电和断电顺序来正确操作子系统和下游组件,对于需要按特定顺序开启以确保操作安全性和可靠性的电源轨,排序至关重要。对电源轨进行排序还有助于在通电期间错开涌入电流,从而减少系统应力和输入电压骤降,同时也有助于防止潜在的反向偏置状况。

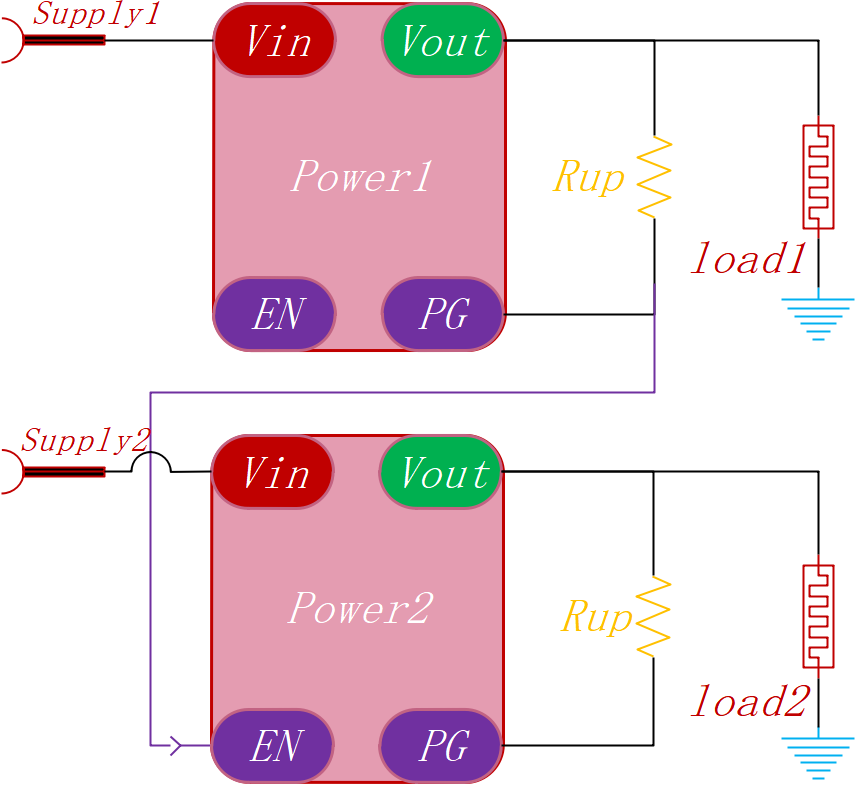

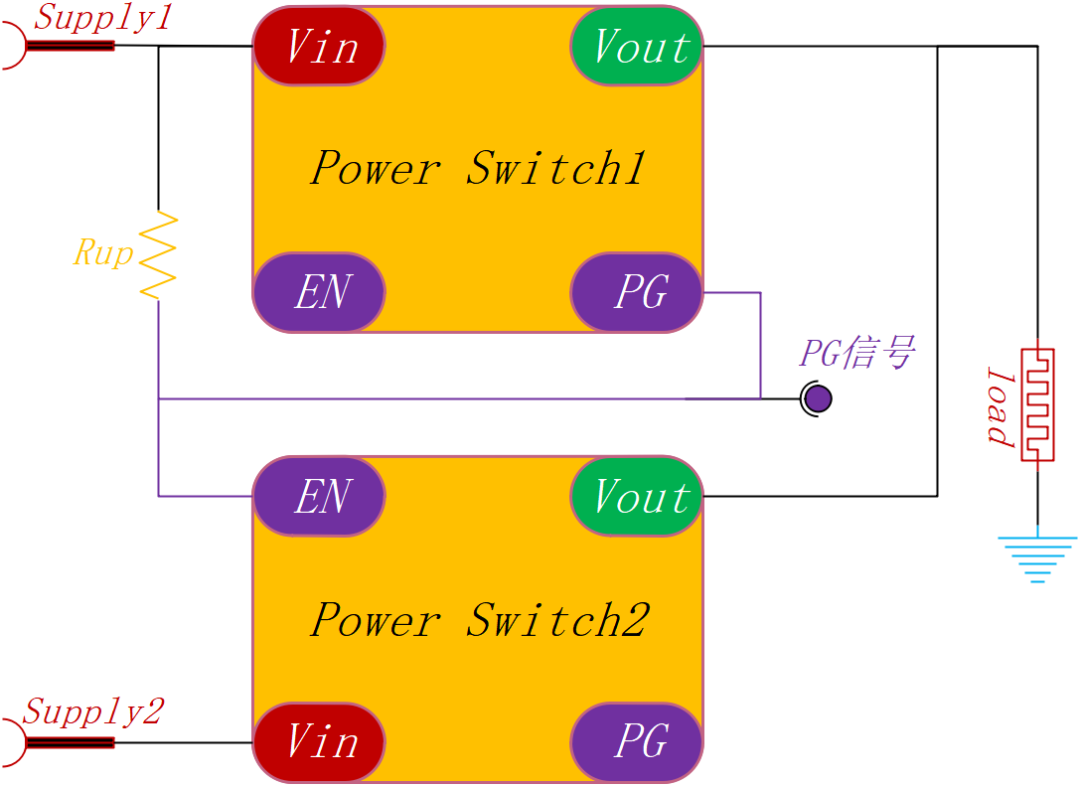

可以使用PGOOD信号对电源轨进行排序,例如,通过将负载开关的PGOOD信号连接到第二负载开关的使能引脚,只有在第一负载开关稳定之后,第二负载切换才会导通。这种情况延迟了第二负载开关的接通,有效地交错电源轨并降低了系统上的浪涌电流应力。当第一个开关被禁用时,PGOOD信号将EN/ON引脚拉低,并阻止第二个开关接通。

图10-4展示了一个使用PGOOD的排序应用方式,还可以在PGOOD信号中添加延迟,以进一步延迟电源轨的开启/关闭,如图10-5所示。

图10-4:电源排序

图10-5:向电源输出引脚添加延迟

3.电源多路复用

电源多路复用是一组电子开关,用于选择多个输入电源轨并将其转换为单个输出,包括备用电源轨或备用电池的系统可能需要在电源之间快速切换,以最大限度地减少输出电压下降并防止系统重置。为了防止出现反向电流情况,可以使用PGOOD信号切换输入。

通过将负载开关等器件的PGOOD信号连接到外部P-FET的栅极,PGOOD信号实现了两个电源轨之间的无缝切换,并消除了对分立时序电路的需要。如图10-6所示,当PGOOD引脚拉高时,P-FET的栅极也拉高,从而关闭FET,当PGOOD引脚指示为低,P-FET的栅极拉低并导通P-FET时,允许电流从IN2流出。

图10-6:先通后断电源多路复用器示意图

4.PGOOD信号的实现

PGOOD可以分立实现,也可以集成实现。

分立的PGOOD

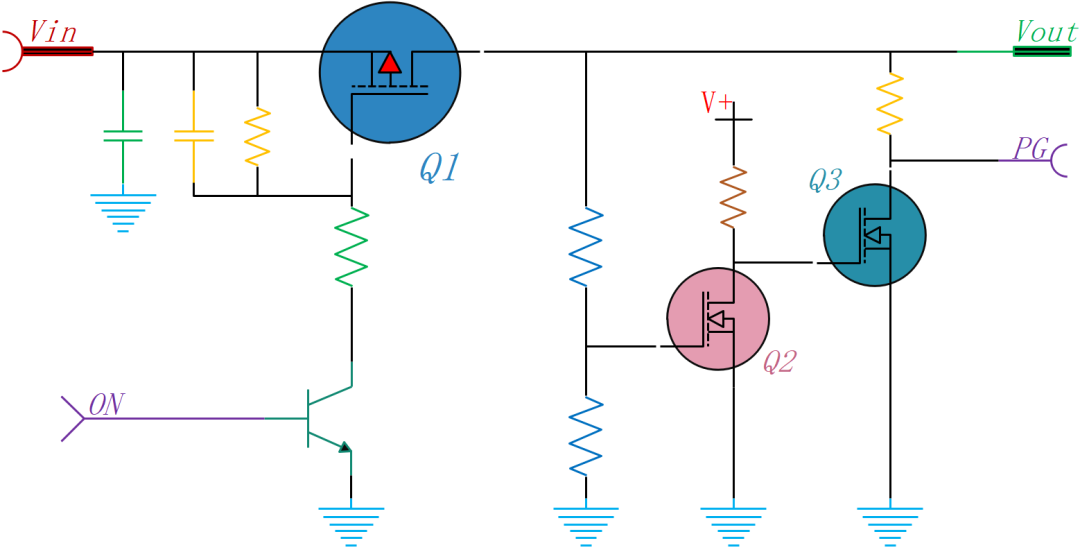

图10-7显示了PGOOD信号的分立实现,在该方式中,PGOOD信号取决于输出电压。一旦输出电压达到某个阈值以偏置分立FET,则PGOOD指示。在这个例子中,当Vout为低时,FET Q2栅极的电压拉低,使其截止,这使得Q3的栅极被拉高到V+,使其导通,并将PGOOD信号拉到地。当Vout达到电阻分压器指定的特定电平时,Q2上的栅极指示为高,这将Q3的栅极拉低,从而关断Q3。这将PGOOD输出拉高到Vout,从而PGOOD正常指示。

图10-7:分立的PG结构

该电路的一个限制是PGOOD信号仅受Vout的影响,当存在Vout时,即使Vout电压轨波动,PGOOD信号也将指示。例如,如果Vout标称为12V,但高电容负载连接到输出,则输入电压可能下降到10V,只要左FET被偏置,PGOOD信号将保持有效。

集成的PGOOD

根据设备的不同,有几种使用集成IC实现PGOOD的方法。第一种方法,Vout/Vin的PGOOD,类似于分立PGOOD的解决方案。如图10-8所示,当输出电压达到Vin的某个百分比时,PGOOD信号生效。对于该示例,一旦Vout达到Vin的90%,PGOOD信号将指示。这是通过Vin和Vout之间的比较提供了PGOOD的简单功能。

图10-8:集成的Vout/Vin--PG

但是当接通高电容性负载时,Vout/Vin的PGOOD会受到限制,由于PGOOD信号仅取决于Vin与Vout的比率,因此即使电压波动,PGOOD也将成立。如果下游负载由于高电容性负载而拉取大量电流,则在启动期间可能会发生大的浪涌电流事件。对负载电容充电可能导致输入电压下降,由于PGOOD最终取决于Vin/Vout比率,因此如果Vin和Vout下降,则PGOOD信号仍将有效。

Vout/Vin的PGOOD在较低电压应用中也有另一个限制,在较低的Vin下,由于导通电阻,PGOOD信号可能无法指示。例如,如果器件在0.5V、1A、导通电阻为100mΩ的条件下工作,则输出电压将为0.4V,这在90%Vin的范围之外,因此,PGOOD信号可能不会指示。

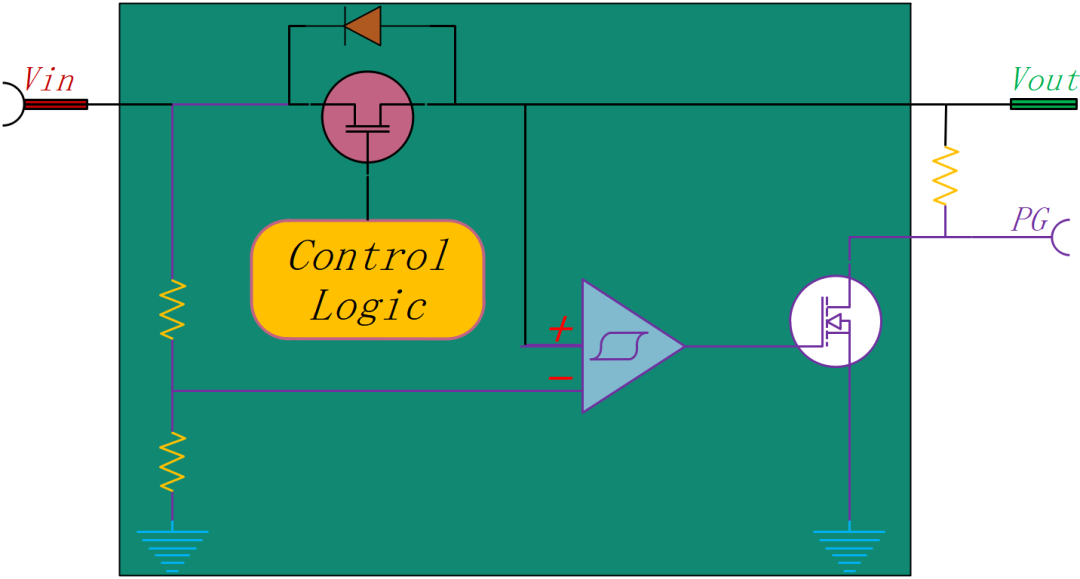

实现PGOOD的一种有效方法是测量通过FET的导通电阻,这种方法有时被称为“VGS

GOOD”,当VGS电压上升到FET导通电阻接近其标称值时,这种方法会触发PGOOD。延迟也被引入到电路中,以防止任何瞬态或涌入事件意外地触发VGS GOOD。在EN/on引脚上的电压超过器件的VIH电平之后,器件将测量导通电阻并等待一定时间(tBLANK),然后触发为高电平。如果EN/on引脚上的电压降至VIL以下,或者FET的VGS降至阈值以下,则PGOOD关闭指示,图10-9显示了VGS

GOOD的常见实现方法。

图10-9:集成的VGS--PG

VGS GOOD提供了在较低Vin值下工作的优点,因为导通状态电阻波动较小,并防止瞬态或浪涌条件导致PGOOD引脚的意外触发。VGS GOOD的一个限制是启动期间的VBIAS和VON,如果VBIAS和VON引脚为高电平,并且Vin开始斜坡上升,则由于VGS阈值保持高电平,PGOOD将被触发,由于VBIAS为提供给栅极的电压供电,因此VGS阈值将保持高电平。

5.小结

需要稳定输入电压的敏感应用可以使用PGOOD信号来保持电源轨在调节范围内,PGOOD信号可以帮助管理涌入电流或控制电源轨时序,这在诸如负载工作顺序或功率复用之类的应用中是非常有用的。

-

good2013-04-28 0

-

Good view Good Job2015-01-13 0

-

请问DC-DC电源芯片Power good信号怎么输出?2019-10-16 0

-

ADC Input Noise: The Good,The2009-09-23 1358

-

TPS77215,pdf(Power Good Output2010-10-17 413

-

TPS77150,pdf(Power Good Output 150-mA LDO Regulator)2010-10-17 764

-

TPS77115,pdf(Power Good Output2010-10-17 315

-

TPS77227,pdf(Power Good Output2010-10-18 312

-

TPS77201,pdf(Power Good Output2010-10-18 367

-

TPS77128,pdf(Power Good Output2010-10-18 346

-

TPS77127,pdf(Power Good Output2010-10-18 377

-

用于信号调理的微电路2012-01-06 800

-

LT8709 Demo Circuit - Negative Inverting Regulator with Output Current Monitor & Power Good (-4.5V to -42Vin to 5V @ 4A)2021-03-09 452

-

AD5592R-KGD:数据Sheet的Known Good2021-04-24 370

-

BD9S系列: 配置Power Good功能的车载ADAS用超小型降压DC/DC转换器2023-02-09 468

全部0条评论

快来发表一下你的评论吧 !