EC SRAM映射到CPU Memory空间的共享内存设计

描述

ShareMemory,顾名思义就是共享内存。这个概念在很多计算机系统中都存在,本文特指 EC SRAM 映射到 CPU Memory 空间的共享内存设计。

01—ShareMemory 简介

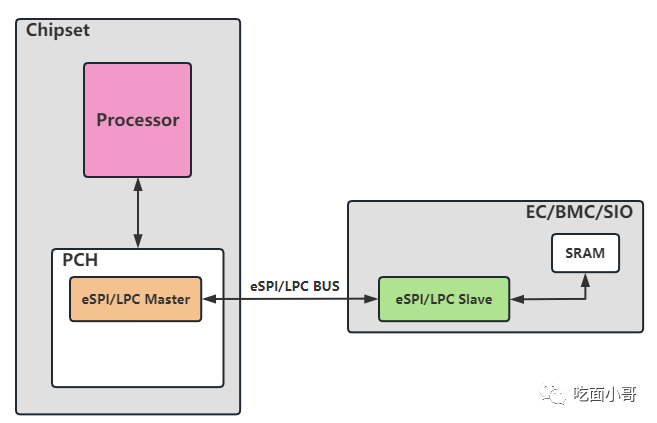

此处的 ShareMemory 特指,在 EC 和 CPU(x86/ARM) 通过 eSPI/LPC 总线连接的系统中,EC SRAM 映射到 Host Memory 空间。当 Host 端需要访问 EC SRAM 时,就和访问 Host 的 Memory 一样简便。

ShareMemory 的设计极大提高了CPU 和 EC 之间的数据传输效率。

eSPI/LPC 的 Master Controller,一般作为一个 PCI 设备存在。因此可以通过修改 eSPI/LPC Controller 的 PCI 配置空间寄存器将指定的 IO 空间和 Memory 空间等资源分配给 eSPI/LPC Master Controller。

当 OS 或者应用软件通过 CPU 指令访问指定 IO端口,或者访问指定 Memory 地址时,访问操作会被转发至 eSPI/LPC 的

Controller。最终由 eSPI/LPC Controller

生成通讯协议发送给 eSPI/LPC 总线上连接的从设备,如下图所示。

eSPI/LPC Slave 一般有 EC、BMC、SIO 等。以EC 为例,当从设备接到 eSPI/LPC 总线上的 Memory Cycle后,eSPI/LPC Slave Controller 就会解码 Memory 地址。

如果发现该地址在配置的Memory 空间内,eSPI/LPC Slave Controller 就会把数据写入指定的 SRAM,或者将指定SRAM 的值返回。如此就完成了 EC SRAM 映射到 CPU Memory 空间,这就是 EC ShareMemory 实现的原理。

02—CPU 端的配置

由于设计上的差异,不同 CPU 针对

ShareMemory 的配置有所不同。

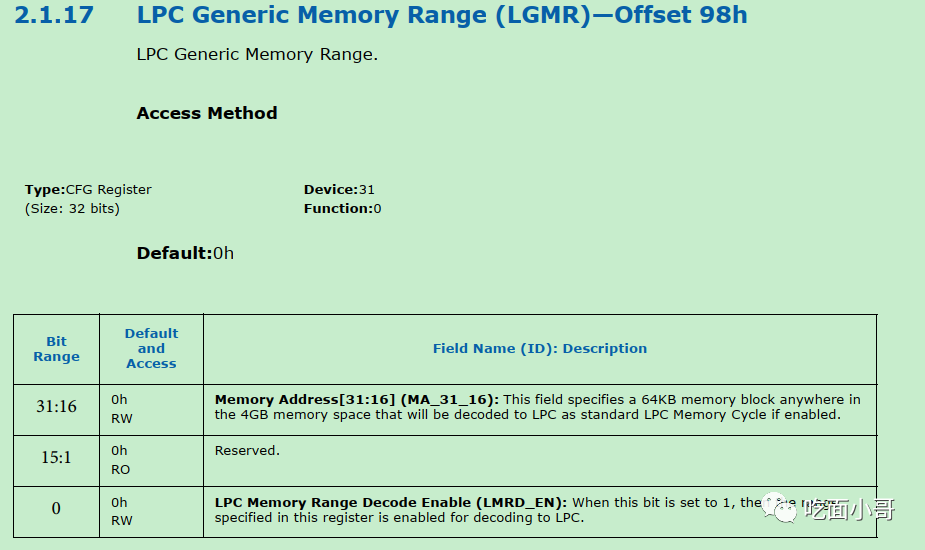

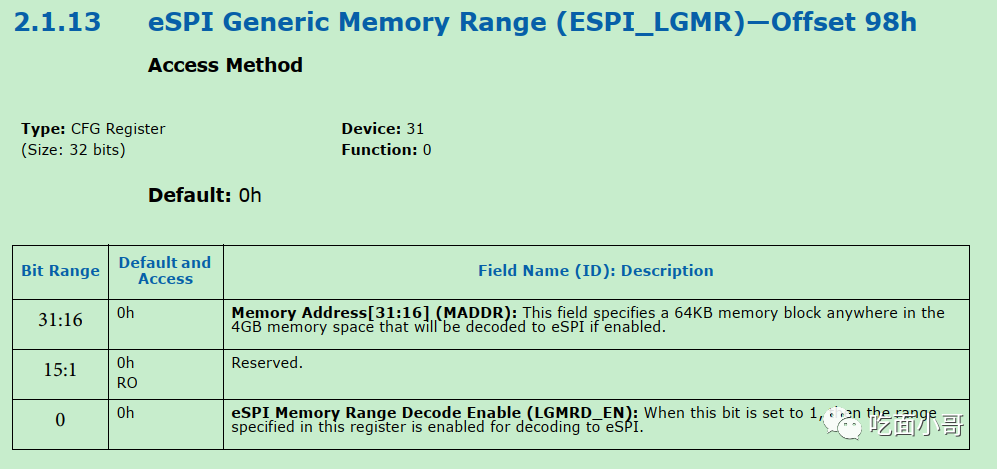

x86 Intel 平台

在 Intel 平台上,eSPI 和 LPC Controller 都是作为一个 PCI 设备存在,两个控制器的 PCI 设备号一致,都是B0:D31:F0,实际使

用时二选一。

如下图所示,配置 Offset 98h 寄存器,即可把 CPU 的指定Memory 空间分配给

eSPI/LPC Master Controller。

x86 AMD 平台

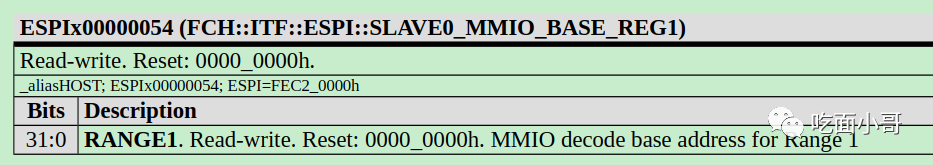

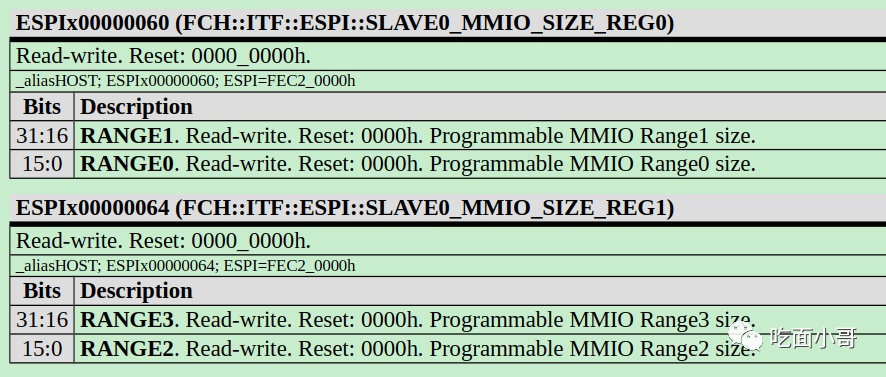

在 AMD 平台上 eSPI 的配置寄存器先被映射到指定的 Memory 空间。配置eSPI MMIO 寄存器即可把指定的CPU Memory 空间分配给 eSPI 控制器。eSPI 配置空间基地址为 0xFEC2_0000,MMIO 基地址配置寄存器为 Offset 50/54/58/5C,长度配置寄存器为 Offset 60/64。

注意 : 此处的寄存器配置后直接生效。

ARM Phytium 平台

飞腾平台上的 LPC Controller 作为一个外设存在,支持 DMA模式、IO模式、

Memory模式、FirmwareMemory 模式。

由寄存器 INT_APB_SPCE_CONF 配置,每个模块占用Memory 空间大小为 32M。

如下表格所示访问 CPU Memory 空间 0x20000062,会发起 LPC 的 IO Cycle(IO Port 62)。

访问 CPU Memory 空间 0x22000000,

会发起 LPC 的 Memory Cycle。

LPC Controller 的 CPU Memory 资源划分如下:

| 模块 | 基地址 |

|---|---|

| IO | 0x20000000 |

| Memory | 0x22000000 |

| FirmwareMemory | 0x24000000 |

| DMA | 0x26000000 |

其他 CPU 平台

eSPI/LPC Master Controller 的资源分配方法在不同的 CPU 平台上都不一样,需要

根据 CPU 指导手册完成配置。

03—EC 端的配置

EC 的硬件设计中,一般有个

ShareMemory Controller,作为一个SIO设备存在,负责处理 eSPI/LPC 总线上的 Memory Cycle。

EC 端有如下两个参数需要配置:

第一,指定可识别的 Host 端的Memory 基地址。这就指明了 EC 可解码的

Host Memory 起始地址。配置寄存器一般位于 SIO 配置空间。

第二,指定EC端匹配的 SRAM 基地址和长度。这就指明了 EC 端的某段

SRAM 空间被映射到 Host Memory 空间。配置寄存器一般位于 EC 的

ShareMemory Controller 内。

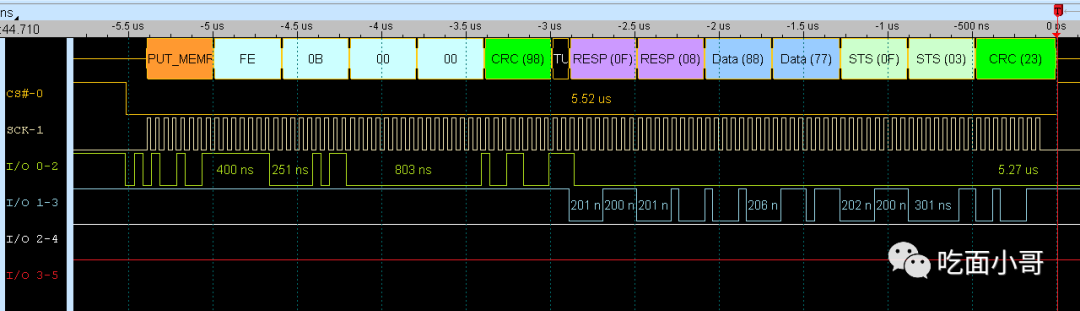

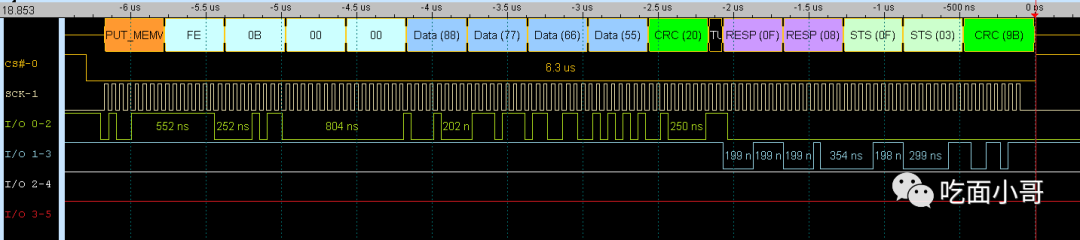

上述2个配置参数的配置方法以及寄存器位置,查阅对应 EC 芯片的用户手册即可获取。如下图所示,是基于 eSPI 总线实现

ShareMemory 访问功能后,Host 读写

EC SRAM 的通讯波形。

EC 端和 CPU 端都完成相应配置后,在OS 下访问 Memory 即可访问到指定的 EC SRAM 存储区间。

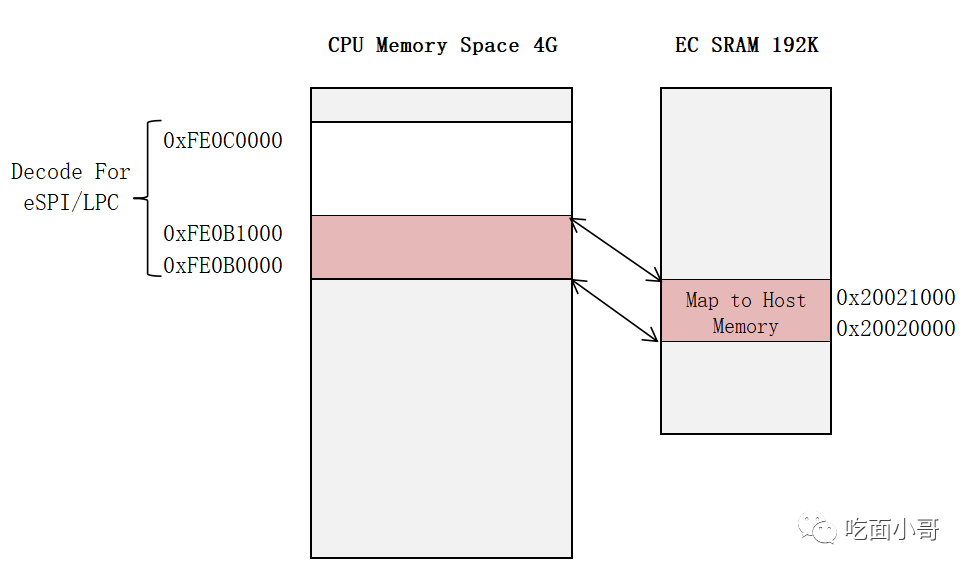

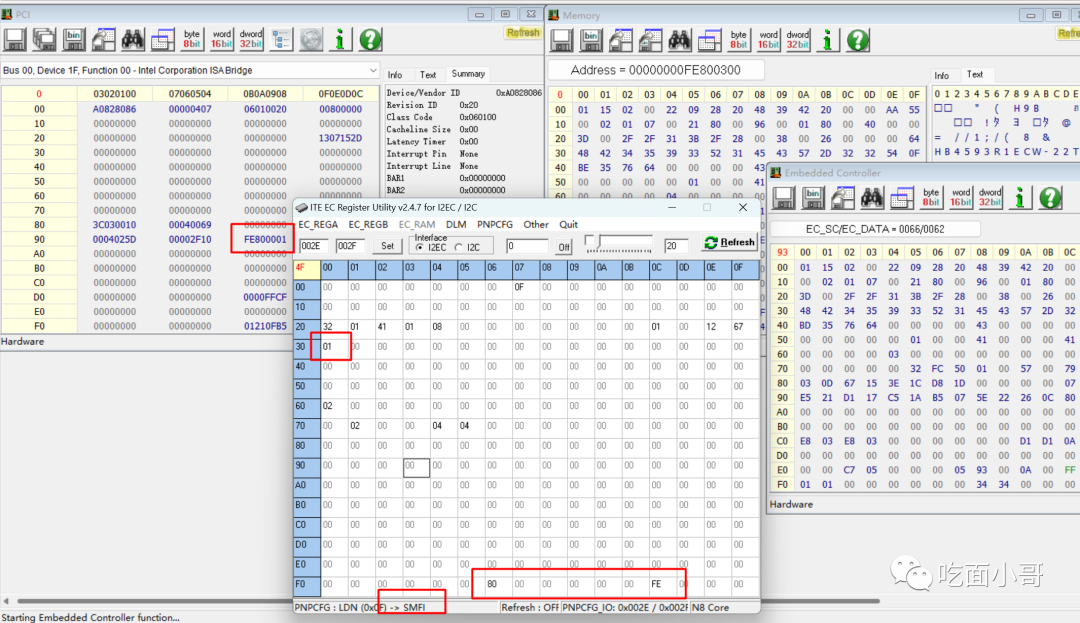

下图 Intel ADL 平台和 EC 的配置结果,最终实现了 EC SRAM 0x300映射到

Host Memory 空间的 0xFE800300 位置。

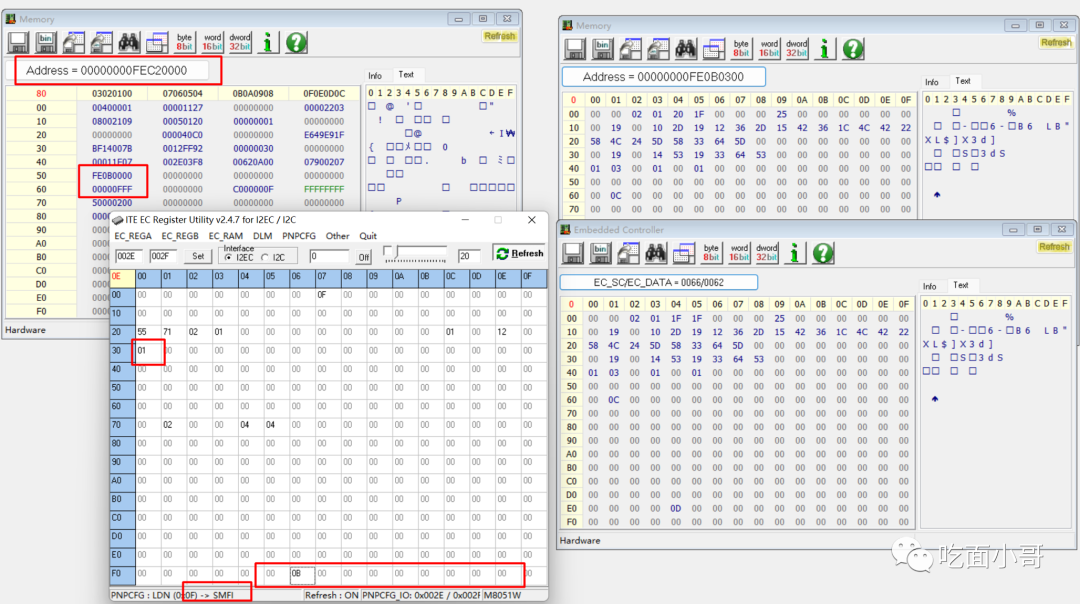

下图是 AMD Ryzen7840 平台和 EC 配置结果,最终实现了 EC

SRAM 0x300 映射到 Host Memory 空间的 0xFE0B0300 位置。

04—ShareMemory 的应用

ShareMemory 的目的就是把 EC 的 SRAM 存储映射到 CPU Memory 空间,如此 CPU 就可以快速完成大量的 EC 数据访问。使用 EC 端提供的

ShareMemory Semaphore,Host 访问完 EC SRAM 还可以通知 EC 内核。

ACPI 规范定义的 ECI 也可以访问 EC SRAM,但是涉及到状态位的等待同步,访问速度没有 ShareMemory 快。

因此 Host 和 EC 之间有大量数据需要传递的时候,ShareMemory 就是第一方案。当然EC SRAM也可以映射到 CPU的 IO 空间,实现原理一样。只是方向 CPU IO端口,最终会在eSPI/LPC 总线上发起 IO Cycle,EC端接到后按映射关系转换为 SRAM的访问即可。

-

linux如何共享内存实验2020-06-08 0

-

如何将共享代码映射到DSPR5以及将其映射到其他RAM区域?2024-01-24 0

-

Linux的mmap文件内存映射机制2017-03-08 0

-

请问如何在platform文件中实现将msmc映射到0xa0000000起始的地址空间中?2018-07-24 0

-

mmap()函数映射到内存中出现bus error的错误2019-02-25 0

-

为何启动模式为SRAM时0x20000000不会映射到0x00000000 ?2019-07-29 0

-

使用UARTLite IP如何找到内存映射IO方法2020-04-16 0

-

共享内存知识记录2021-12-15 0

-

地址总线是要映射到FPGA的内部还是直接ARM的内存空间2022-11-22 0

-

STM32G0将地址0x00000000重新映射到SRAM不起作用咋办2022-12-22 0

-

ESP32-D0WDR2-V3带外接flash和emmc,外部闪存将无法将内存映射到cpu内存空间是怎么回事?2023-04-12 0

-

浅析linux内存映射原理2019-08-24 1480

-

世上最好的共享内存(Linux共享内存最透彻的一篇)上集2019-11-29 18002

-

虚拟机:linux高端内存管理之永久内核映射2020-06-23 3401

-

内存是怎么映射到物理地址空间的?内存是连续分布的吗?2023-06-30 2047

全部0条评论

快来发表一下你的评论吧 !