如何用HLS实现UART

描述

用 HLS 实现 UART

介绍

UART 是一种旧的串行通信机制,但仍在很多平台中使用。它在 HDL 语言中的实现并不棘手,可以被视为本科生的作业。在这里,我将通过这个例子来展示在 HLS 中实现它是多么容易和有趣。

因此,从概念上讲,这是一个微不足道的项目;然而,它对于对 HLS 感兴趣的人来说是有启发性的。

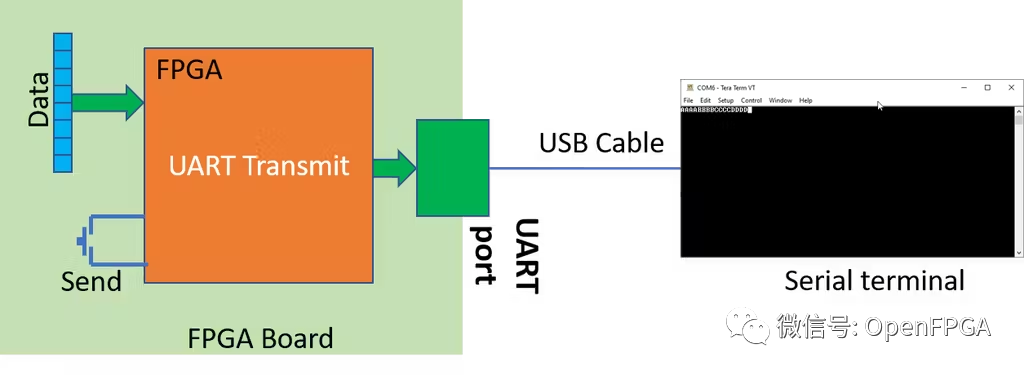

现在项目定义: 下图显示了项目的简单结构。

我们在 FPGA 中的设计UART发送,每当按下按钮时就会将其发送到计算机上的串口调试助手。

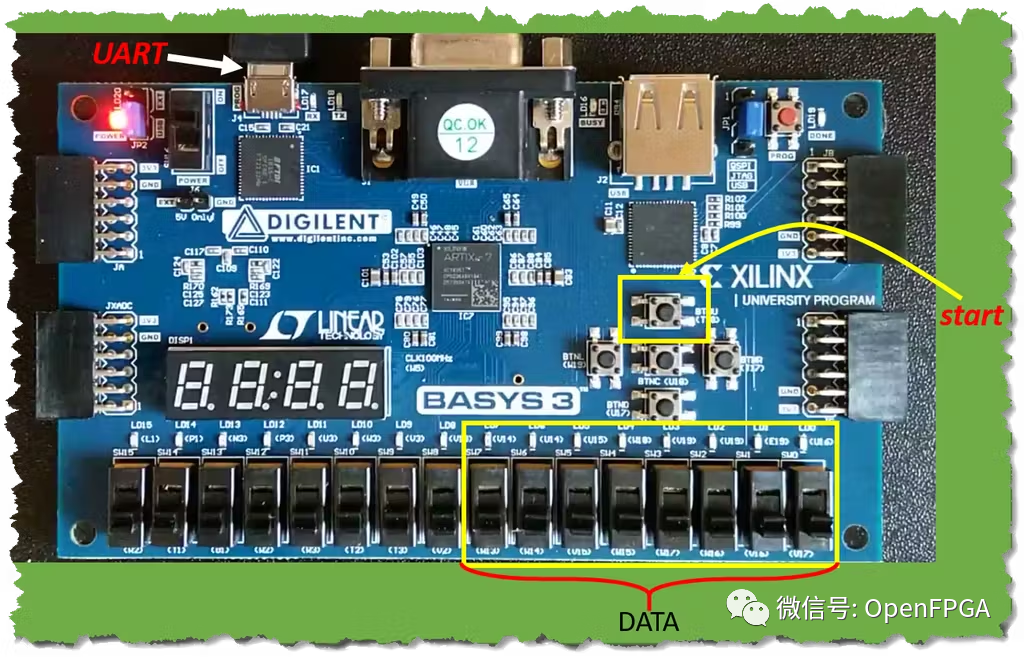

FPGA 板上的八个滑动开关用于输入数据字节(例如字母或符号的 ASCII 代码)。此外,UP 按钮用作发送控制键。

设计很简单,程序本身能接受开发板上拨码开关的数据,然后添加一个“0”起始位和一个“1”停止位,最后以9600 bit/s的波特率发送出去。

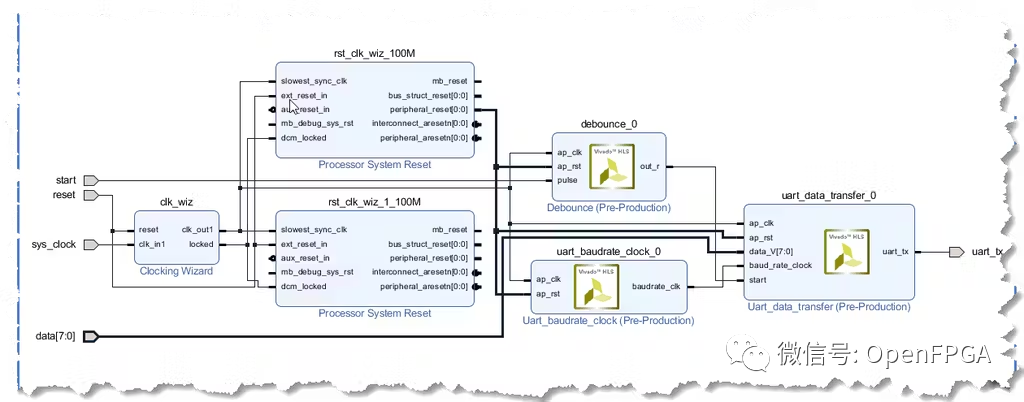

首先需要根据开发板上的时钟(本例是100MHz),进行分频,生成串口发送所需的时钟。

bool delay(long long int n) {

static bool dummy = 0;

for (long long int j = 0; j < n; j++) {

#pragma HLS pipeline

dummy = !dummy;

}

return dummy;

}

void uart_baudrate_clock(bool &baudrate_clk) {

static bool s = 0;

s=!s;

baudrate_clk = s;

delay(5208);

}

生成速率时钟后,简单的状态机可以将数据发送出去。

void uart_data_transfer(bool &uart_tx, ap_uint<8> data, bool baud_rate_clock, bool start) {

static bool send_bit = 1;

static bool start_state = 0;

static bool transfer = 0;

static unsigned int count = 0;

static int state = 0;

ap_uint<10> d= ((bool)0b1, (ap_int<8>)data, (bool)0b0);

if (start == 1 && start_state == 0) {

transfer = 1;

start_state = 1;

count = 0;

}

if (start == 0 && start_state == 1) {

start_state = 0;

}

if (baud_rate_clock == 1 && state == 0 && transfer == 1) {

send_bit = d[count++];

if (count == 10) {

transfer = 0;

}

state = 1;

}

if (baud_rate_clock == 0 && state == 1) {

state = 0;

}

uart_tx = send_bit;

}

将这些代码综合到 RTL 模块后,我们可以创建 Vivado 项目并生成 FPGA 比特流,并验证。

总结

很简单的一个实例,大家可以自行和HDL实现的方式进行对比。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

新手求助,HLS实现opencv算法加速的IP在vivado的使用2017-01-16 0

-

hls之xfopencv2022-09-09 1076

-

Vivado HLS实现OpenCV图像处理的设计流程与分析2021-07-08 0

-

Vivado HLS设计流的相关资料分享2021-11-11 0

-

如何用示波器查看串口UART的波形?2021-12-16 0

-

IO模拟UART实现2010-03-26 904

-

HLS系列 – High Level Synthesis(HLS) 的一些基本概念12017-02-08 696

-

用Vivado-HLS实现低latency 除法器2017-12-04 1145

-

TI配置Hercules ARM安全MCU SCI和LIN 模块如何用于UART通信2018-05-28 1124

-

探索Vivado HLS设计流,Vivado HLS高层次综合设计2020-12-21 3220

-

FPGA——HLS简介2023-01-15 3239

-

HLS协议实现2023-04-06 486

-

调用HLS的FFT库实现N点FFT(hls:fft)2023-07-07 1047

-

调用HLS的FFT库实现N点FFT2023-07-11 662

-

如何用HLS实现UART呢?2023-11-20 359

全部0条评论

快来发表一下你的评论吧 !