一种高性能多通道通用DMA设计与实现

描述

摘 要:

为充分发挥异构多核DSP芯片的实时计算能力,设计并实现了一种高性能多通道的通用DMA,该DMA最大支持64个通道的数据搬运,并支持一维、二维、转置以及级联描述符等多种传输模式。芯片实测传输性能最高可达11.7 GB/s,实现了高效率、高性能的数据供给。

0引言

DSP芯片因其强大的实时计算能力,在军事、通信、工控等领域嵌入式系统中应用广泛[1]。应用需求的不断提高以及信息技术的不断进步,推动了高性能DSP芯片向异构多核、高并行、高集成的方向发展,在DSP芯片具有高算力的同时,其对高效率、高性能的数据供给同样提出了更高的要求。DMA(Direct Memory Access)技术能够提供内存和内存、内存和外设之间的直接数据传输通道,不仅能够提高数据传输速率,还能使得DSP核从复杂的数据传输任务中脱离出来,从而有效提升芯片性能,已成为行业的研究热点[2-5]。

本文面向异构多核DSP芯片的需求,设计实现了一种高性能多通道通用DMA(Multi-channel General-purpose DMA,MG-DMA),支持一维、二维、转置以及级联描述符等多种传输模式,最大64通道,大幅提升了数据传输速率,有效匹配了DSP芯片的计算能力。

1设计与实现

1.1 总体设计

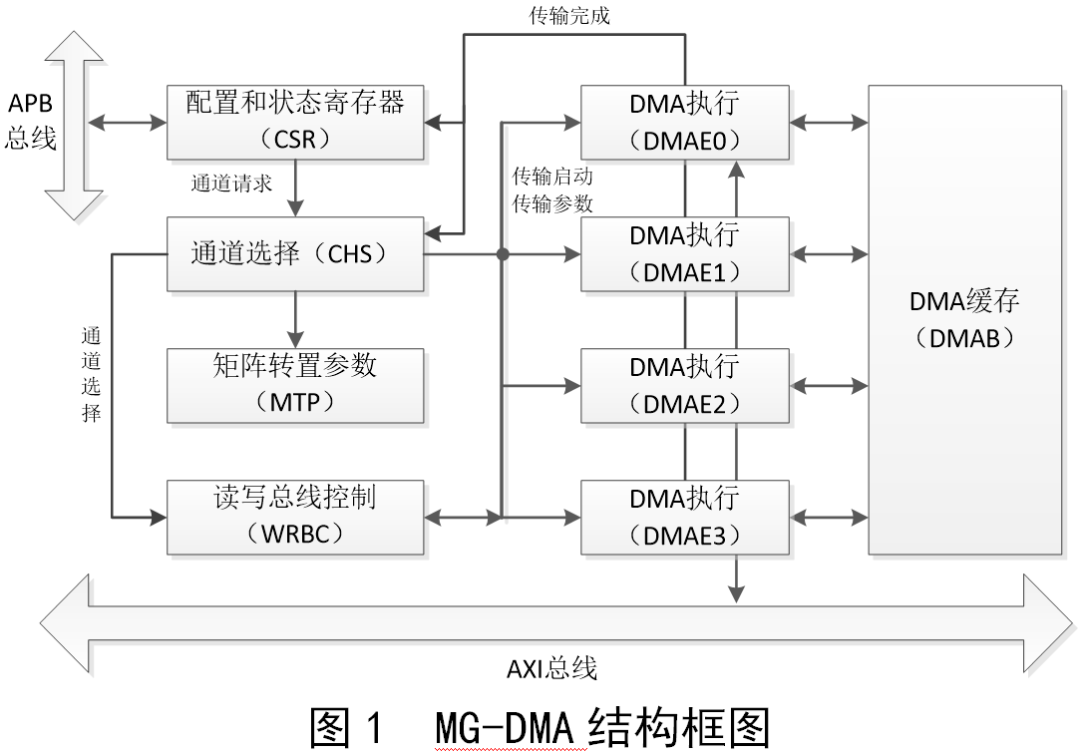

MG-DMA的结构框图如图1所示,包括配置和状态寄存器模块(CSR)、通道选择模块(CHS)、矩阵转置参数模块(MTP)、读写总线控制模块(WRBC)、4个DMA执行模块(DMAE0~DMAE3)以及DMA缓存模块(DMAB)。

各模块功能如下:

(1)配置和状态寄存器模块(CSR):CSR模块有64个逻辑通道的配置寄存器组以及一个总的中端和状态控制寄存器,其中,配置寄存器组主要包括通道传输数据量、数据源地址、数据目的地址、外部描述符地址等信息,64个逻辑通道可根据用户需求映射到任意4个物理通道,映射关系由对应物理通道编号寄存器的值决定。当配置好寄存器组后,CSR模块将对应产生通道请求信号送给通道选择模块,启动一次DMA传输,当DMA传输完成或发生传输错误时,触发相应中断。

(2)通道选择模块(CHS):CHS模块根据接收到的通道请求信号产生通道选择信号,并计算本次传输的配置参数,将参数和传输启动信号传输给对应的DMAE模块,同时将通道选择信号送给WRBC模块,启动一次传输。

(3)DMA执行模块(DMAE):DMAE内部读写各自独立,当一次传输启动后,DMAE模块先启动一次burst读,将读出的数据缓存在DMAB中,一次burst最大支持128个256 bits的数据,读完后再将缓存中的数据写出到相应地址。当所有数据写完或者发生错误时,产生相应的中断信号。4个物理通道各对应一个DMAE模块,4个通道可以同时进行数据传输,但同时只有一个模块可以进行矩阵转置操作,4个物理通道轮流进行矩阵转置。

(4)DMA缓存模块(DMAB):DMAB模块存储空间共32 kByte,每个通道使用4 kByte的RAM,其余16 kByte作为矩阵转置使用。读数据时,DMAE模块将读到的数据进行256 bits拼接对齐后存入DMAB模块;写数据时,由于RAM不是寄存器输出,DMAB模块会将RAM的输出数据进行寄存器锁存后送给DMAE模块,DMAE模块按照地址进行对齐移位后再写出。

矩阵转置时,为实现对存放在内存中的矩阵进行从源矩阵到目标矩阵的行列转置功能,DMA每次转置一个32×32的小矩阵,自动累加矩阵的源地址和目的地址,最终实现一个大矩阵的转置。DMAB中使用了4个4 kByte的RAM,每两个作为一组,组成两个8 kByte的乒乓RAM,每组支持32行×32列×8 kByte的矩阵,实现了乒乓操作。

(5)矩阵转置参数模块(MTP):MTP模块主要用于矩阵转置时的参数计算,每个小矩阵的大小为32行×32列,不足的按实际大小读写。当小矩阵读或写完毕后,计算下一个小矩阵的地址和对应在RAM中的地址。

(6)读写总线控制模块(WRBC):WRBC主要包括读通道编号和写通道编号两个动态的寄存器,读通道编号表示当前使用AXI读操作的通道编号,写通道编号表示当前使用AXI写操作的通道编号,在当前物理通道传输完成后,会判断下一个通道是否需要操作,如果需要,则将AXI总线使用权交给下一个通道。

1.2 工作流程

MG-DMA典型工作流程如下:

(1)通过APB接口配置通道寄存器;当有通道请求时,CSR模块将请求送给CHS模块。

(2)判断是否是矩阵转置请求,如果是,判断矩阵工作编号是否等于通道编号,如果不是,通道允许传输;如果矩阵工作编号等于通道编号,通道允许矩阵传输,将传输启动信号和传输参数送给DMAE模块。如果不相等,等待其他通道矩阵传输完成。

(3)DMAE模块收到传输启动信号后,根据收到的传输参数开始读取数据;DMAE模块每次发送一个burst读操作,读取不超过16个256 bits的数据,可以连续发送多个读命令。

(4)当DMAE模块发送的读命令达到上限时,通知WRBC模块,WRBC模块判断下一个通道是否要读取数据,如果是,更新到下一个通道编号的值,如果不是,按照4个通道顺序轮询。

(5)当DMAE模块在缓存数据大于16个256 bits时,开始burst写操作;如果当次读的数据被写完,通知WRBC模块;WRBC模块判断下一个通道是否要写数据,如果是,更新到下一个通道编号的值,如果不是,按照4个通道顺序轮询。

(6)当收到通道传输停止或总线响应错误时,DMAE模块在发完本次burst读命令后停止读取新数据,在写完所有的数据后,提起总线错误或传输错误中断。

(7)如果不需要读取描述符,当所有数据写完时通道传输完成;如果需要读取描述符,读取下一个描述符后进行下一次DMA操作。

1.3 物理实现

本文所述MG-DMA模块应用于3080型DSP芯片,该芯片包括4个处理核和4个专用加速核,支持PCIe、SRIO等高速接口以及2路DDR4大带宽存储,其片内DMA的性能对DSP芯片计算能力的发挥有着重要作用。物理实现后,MG-DMA模块的总规模约41万Inst,工作主频达到800 MHz。芯片流片后的实物图如图2所示。

2测试

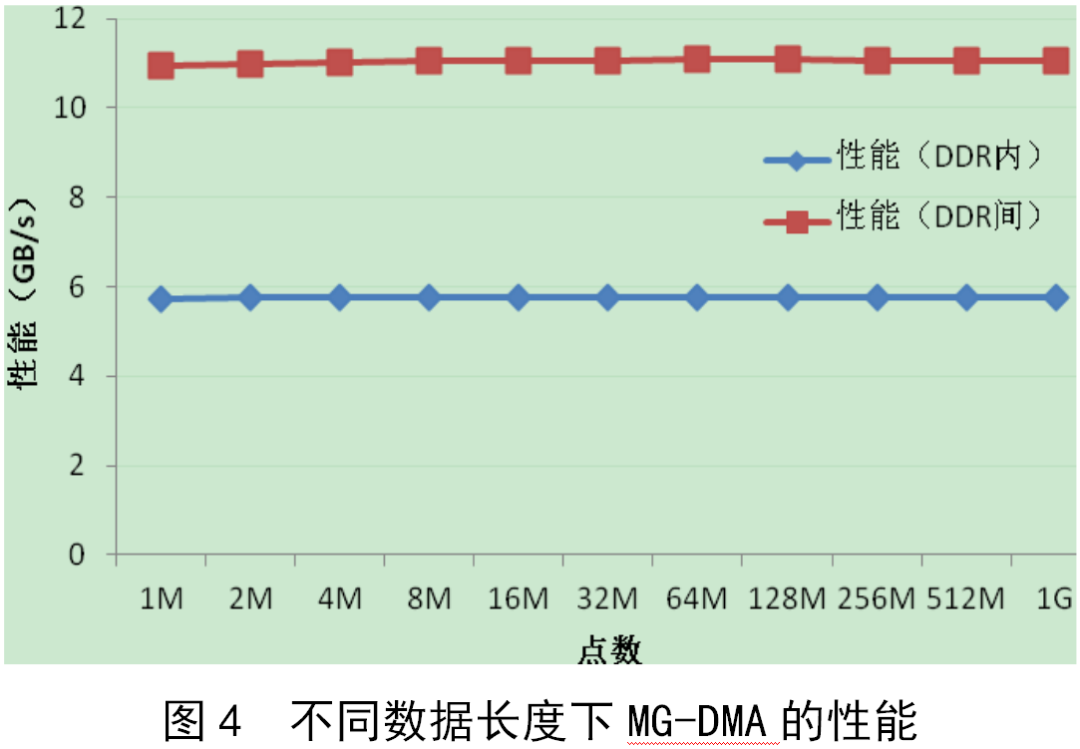

3080型DSP芯片测试板如图3所示。设置芯片DDR速率为2 400 MT/s,分别选择传输数据长度为1 MB~1 GB,测量MG-DMA的性能如图4所示,可以看到,DMA性能随点数的变化不大,在同一DDR内部从一段地址搬运数据到另一段地址的性能平均在5.76 GB/s,从一个DDR搬运到另一个DDR的性能平均在11 GB/s。

改变DDR的速率从1 600 MT/s到3 200 MT/s,设定数据长度为1 MB,测量MG-DMA的性能如图5所示,可以看到,随着DDR速率增加,MG-DMA的性能呈线性增加,DDR速率为3 200 MT/s时,DDR内DMA传输性能为6.7 GB/s,DDR间的DMA传输性能高达11.7 GB/s。

3结语

本文面向异构多核DSP芯片对数据传输性能的需求,设计并实现了一种高性能多通道的通用DMA,实现了64个逻辑通道、4个物理通道的数据搬运,能够支持一维、二维、转置以及级联描述符等多种传输模式。芯片实测结果显示,单个DDR内DMA传输性能为6.7 GB/s,DDR间的DMA传输性能高达11.7 GB/s,大幅提升了数据传输速率,有效匹配了DSP芯片的计算能力。

审核编辑:汤梓红

-

Xilinx FPGA 1/4/8通道PCIe-DMA控制器IP,高性能应用介绍2024-03-07 0

-

用DMA实现的STM32ADC多通道采集读数问题2014-03-26 0

-

一种基于FPGA的多通道频率测量系统的实现方法介绍2019-06-27 0

-

如何设计并实现一种高性能中频采样系统?2021-04-07 0

-

请问怎么设计一种高性能集成电压比较器?2021-04-21 0

-

请问怎么设计一种高性能数据采集系统?2021-04-21 0

-

如何去设计一种高性能的数据采集系统?2021-04-22 0

-

分享一种多通道天线校准参考解决方案2021-05-10 0

-

如何去实现一种高性能网络接口设计?2021-05-20 0

-

分享一种高性能的FM内置天线解决方案2021-05-26 0

-

如何去实现一种高性能IP电话语音终端系统的设计?2021-06-04 0

-

求一种高性能视频系统的解决方案2021-06-07 0

-

如何去实现一种基于STM32的DMA驱动设计呢2021-12-10 0

-

多通道高性能视频采集与加速系统|2023集创赛紫光同创杯优秀作品2023-09-21 0

-

Xilinx高性能PCIe DMA控制器IP,8个DMA通道2024-02-22 300

全部0条评论

快来发表一下你的评论吧 !