高增益单级运放和增益自举电路设计

描述

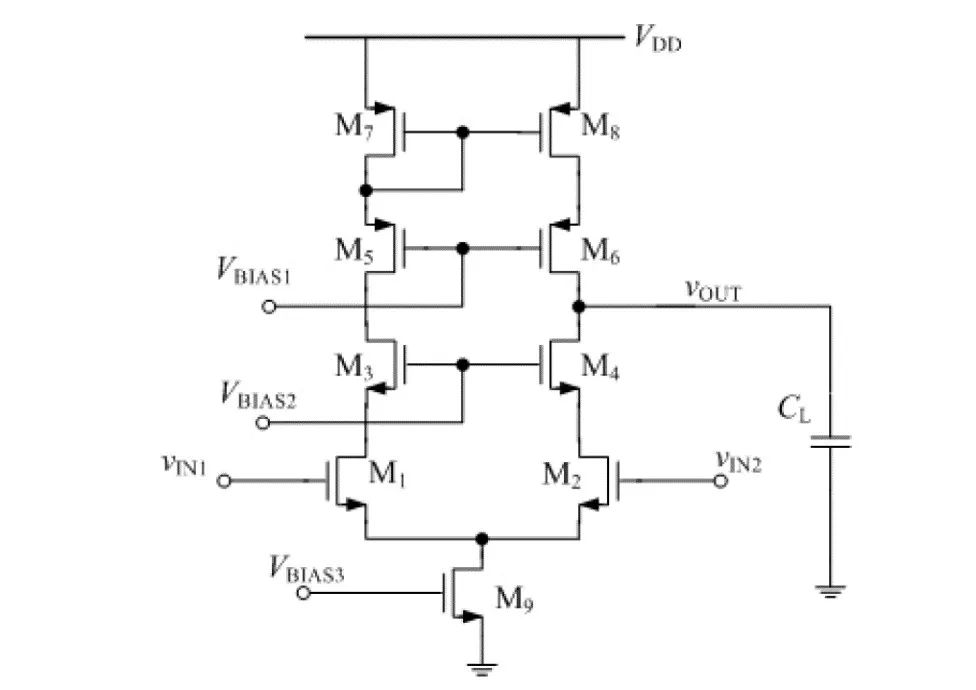

一、套筒式(telescopic)单级单端输出运放

figure 1 套筒式运放原理图

设计思路:

- 通过M9电流200uA,两条支路分别是100uA的电流。我们计算设计仿真的顺序是:M9-M7M8-M5M6-M1M2-M3M4。

- M9电流大,过驱动电压给大些,Von9=300mV,I9=200uA,利用饱和区电流公式计算M9的W/L。偏置电压用Von+Vth算。

- M7M8的PMOS管本应该给大Von,但是其二极管连接,Vds大,由于沟道调制效应,所以给小Von=200mV,I=100uA,计算M7和M8的W/L。

- M5M6手工计算不准确,但还是得初步计算。I=100uA,pmos需给大Von=300mV,算出宽长比。偏置电压Vb1

- M1和M2,Von=200mV,I=100uA,计算宽长比。偏置电压Vcm=Vds9+Von1+Vth1。此时的Vth1和Vds9都需要仿真后查看再调整输入共模电压。

- M3和M4与M1和M2宽长比计算一样。Vb2= Vds9+Vds11+Von3+Vth3,同样需要仿真后回头调整。

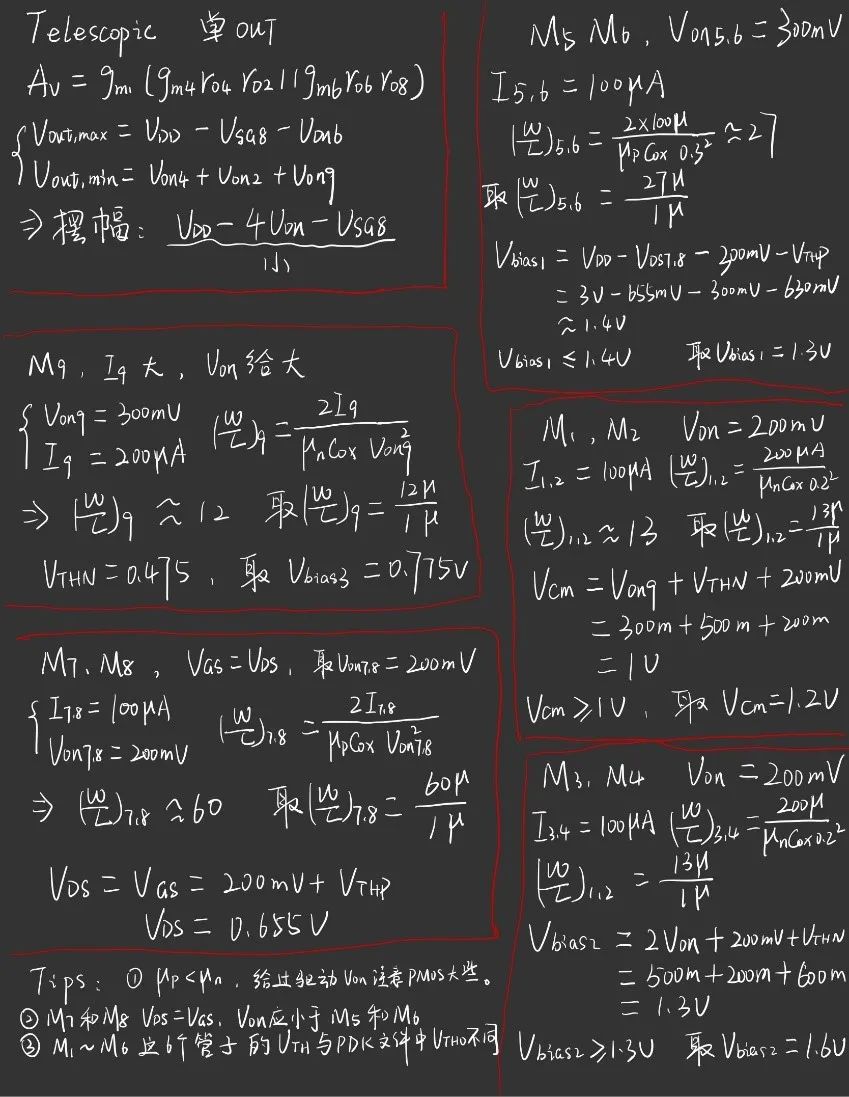

图2是手算的记录:

figure 2 telescopic手算

M5和M6最难调整,可以将其余的偏置电压确定后,用parametricanalysis扫描一下这两管子的宽,确定一个精确值。在TSMC180nm工艺下,我的电路的参数如下:

| Vcc | 3V | (W/L)9 | 12u/1u |

|---|---|---|---|

| Vcm | 1.2V | (W/L)7,8 | 60u/1u |

| Vb1 | 1.3V | (W/L)5,6 | 27u/1u |

| Vb2 | 1.6V | (W/L)3,4 | 13u/1u |

| Vb3 | 775mV | (W/L)1,2 | 13u/1u |

| CL | 3pF |

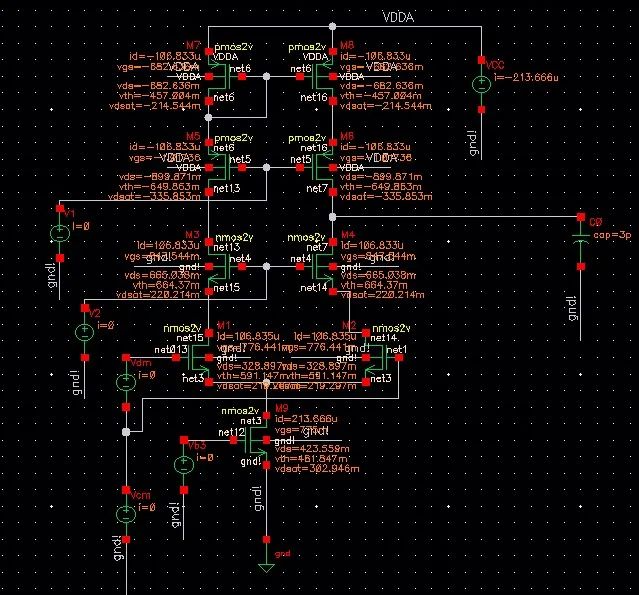

DC仿真结果如下:

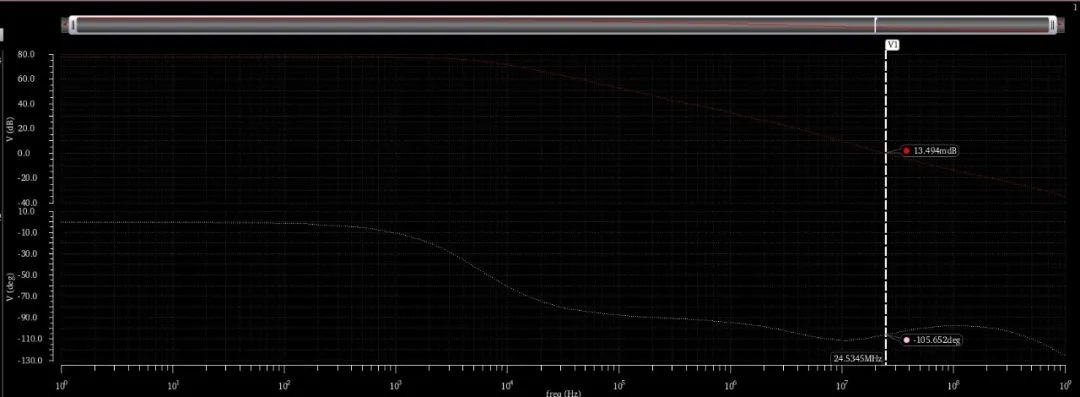

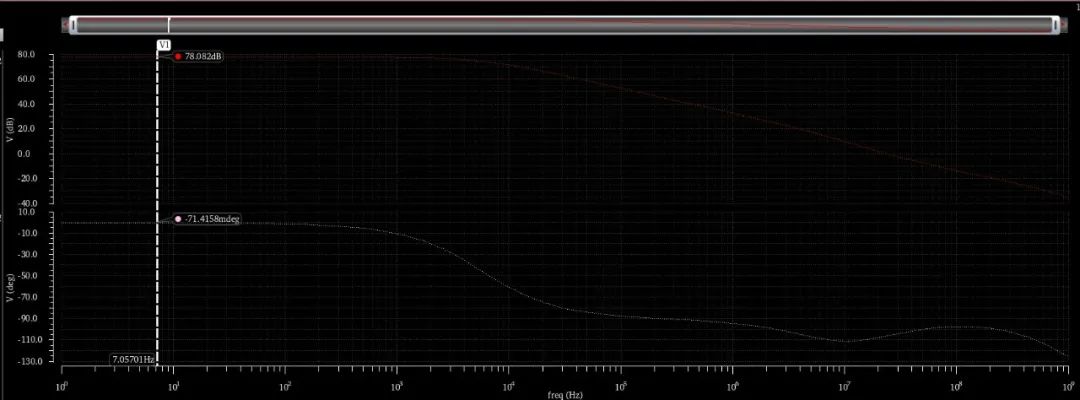

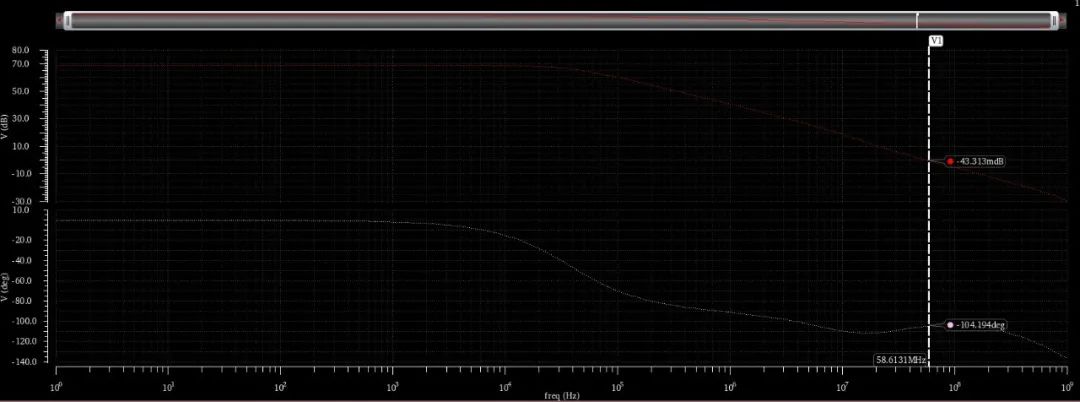

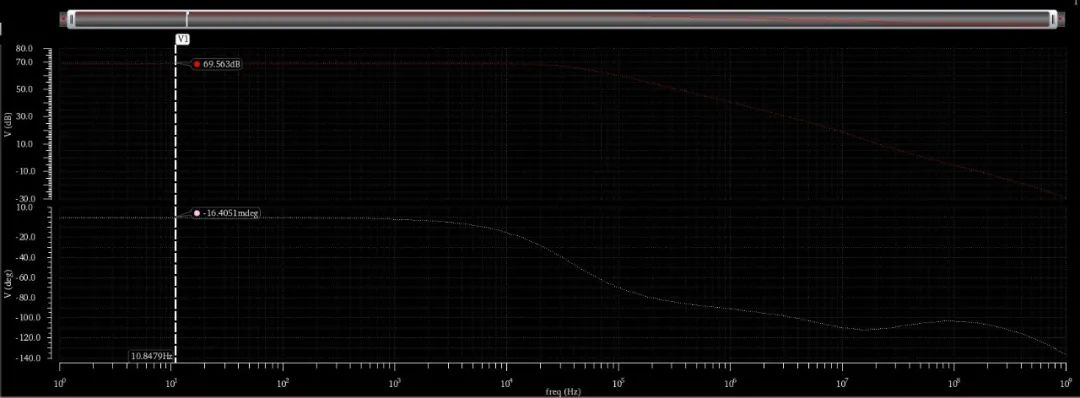

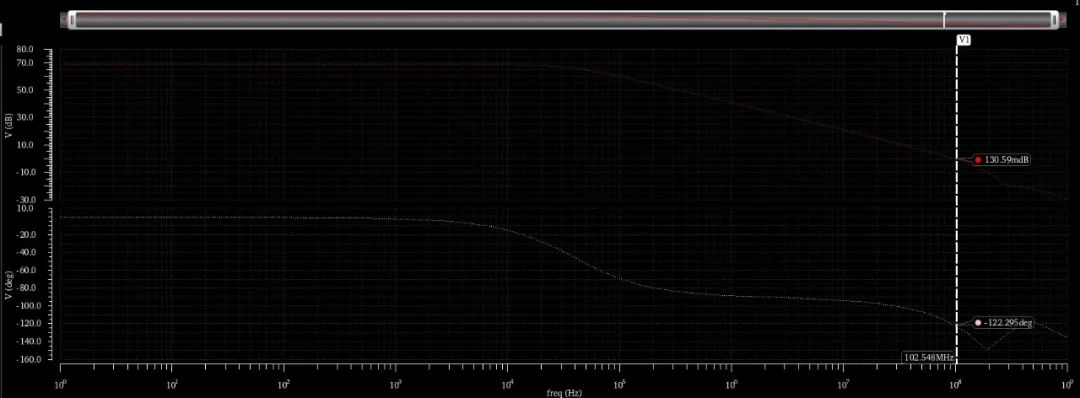

ac仿真结果如下,低频增益78dB。

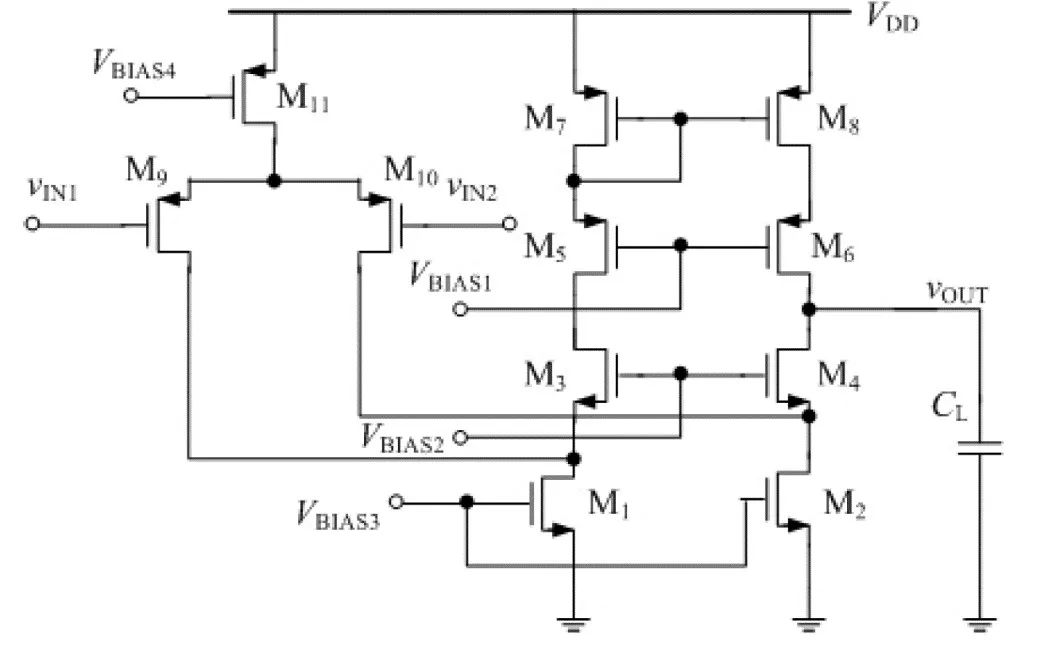

二、折叠共源共栅单级单端输出运放

figure 3 折叠共源共栅运放电路原理图

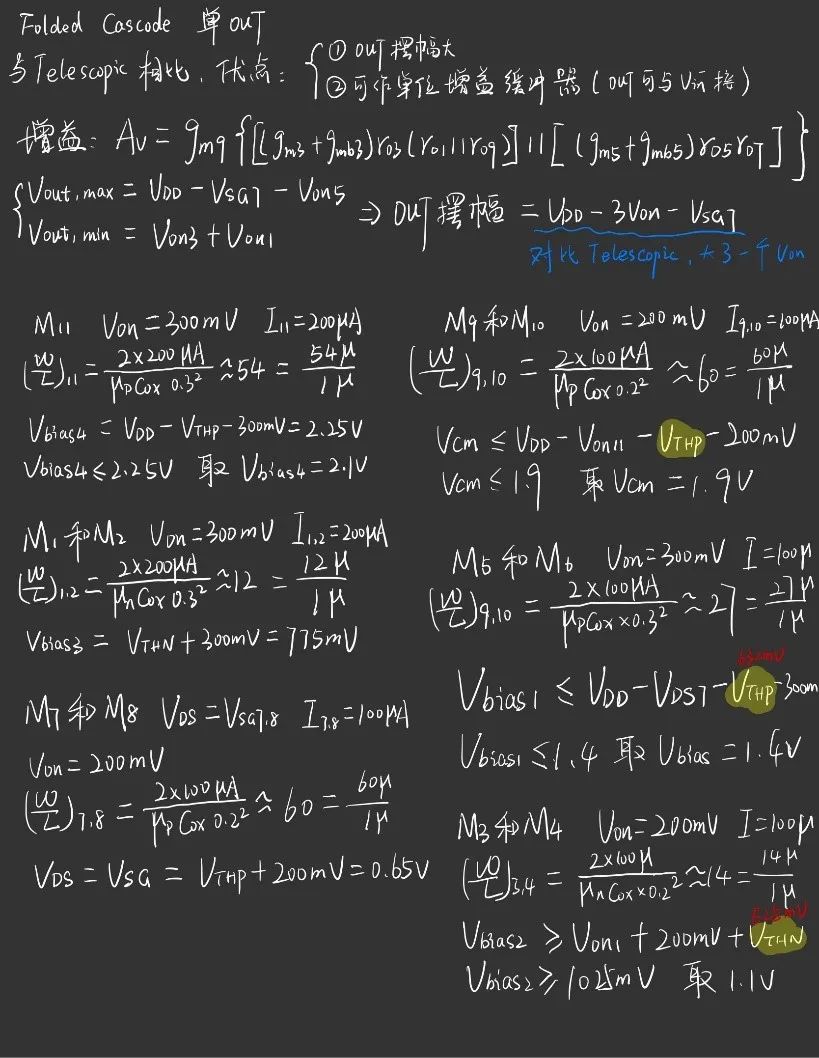

设计步骤与telescopic差不多,主要就是每个偏置电压需要多次仿真调节,M5和M6的宽长比很敏感,需要parametricanalysis扫描一下。图4是手算记录:

figure 4 折叠共源共栅运放参数手算

在TSMC180nm工艺下,电路参数如下表:

| Vcc | 3V | (W/L)9 | 12u/1u |

|---|---|---|---|

| Vcm | 1.5V | (W/L)7,8 | 60u/1u |

| Vb1 | 1.3V | (W/L)5,6 | 29u/1u |

| Vb2 | 1.1V | (W/L)3,4 | 14u/1u |

| Vb3 | 775mV | (W/L)1,2 | 12u/1u |

| Vb4 | 2.2V | (W/L)9,10 | 70u/1u |

| CL | 1pF | (W/L)11 | 54u/1u |

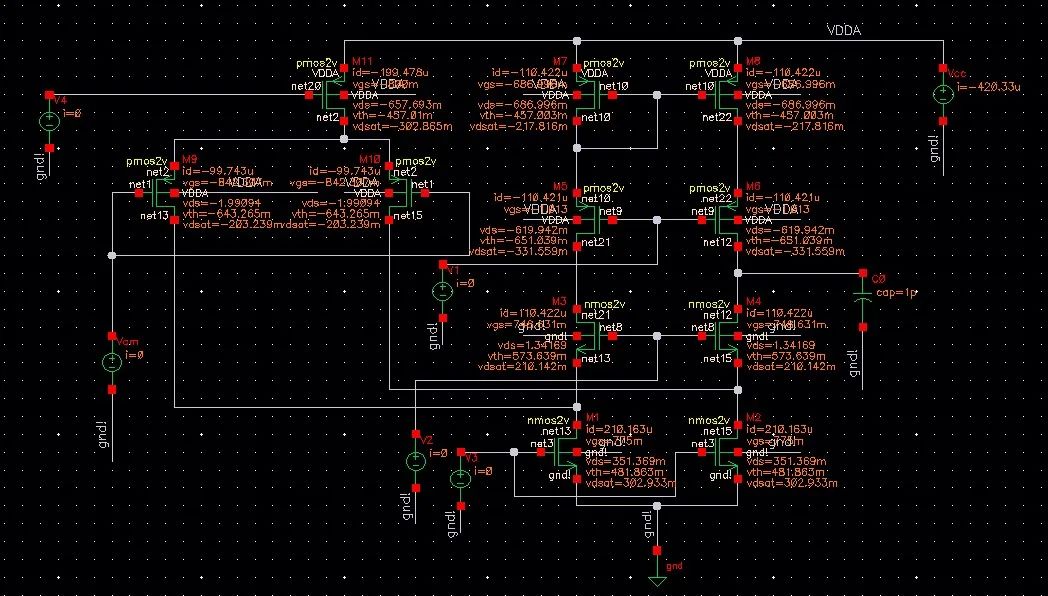

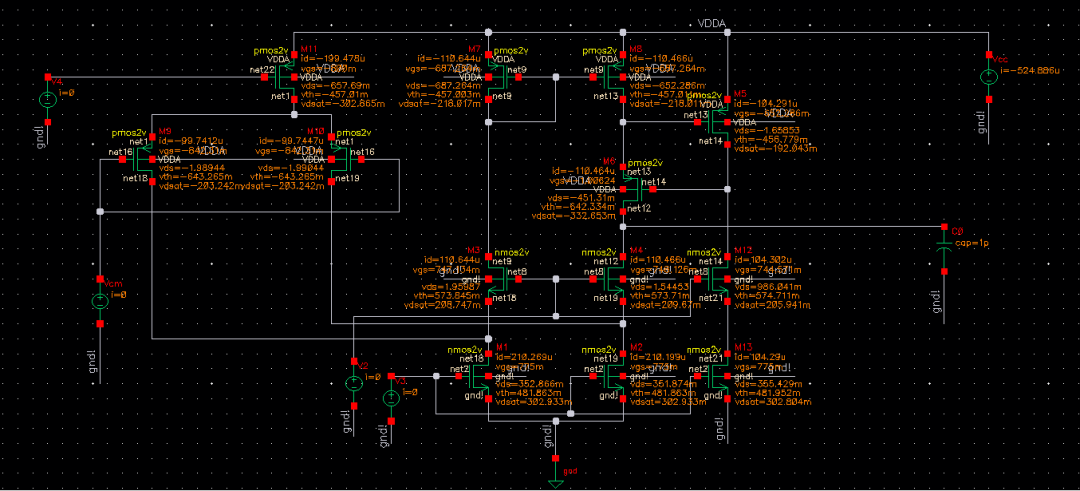

dc直流仿真结果如下图:

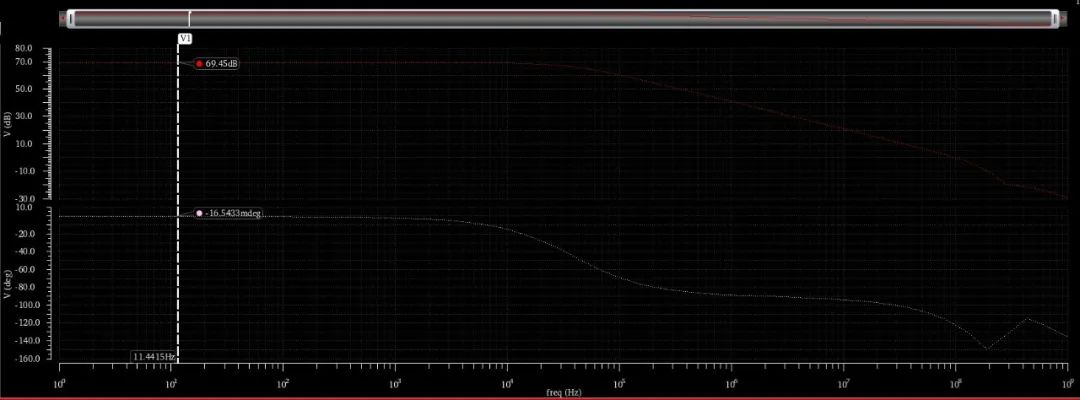

ac仿真结果如下图,低频增益69dB:

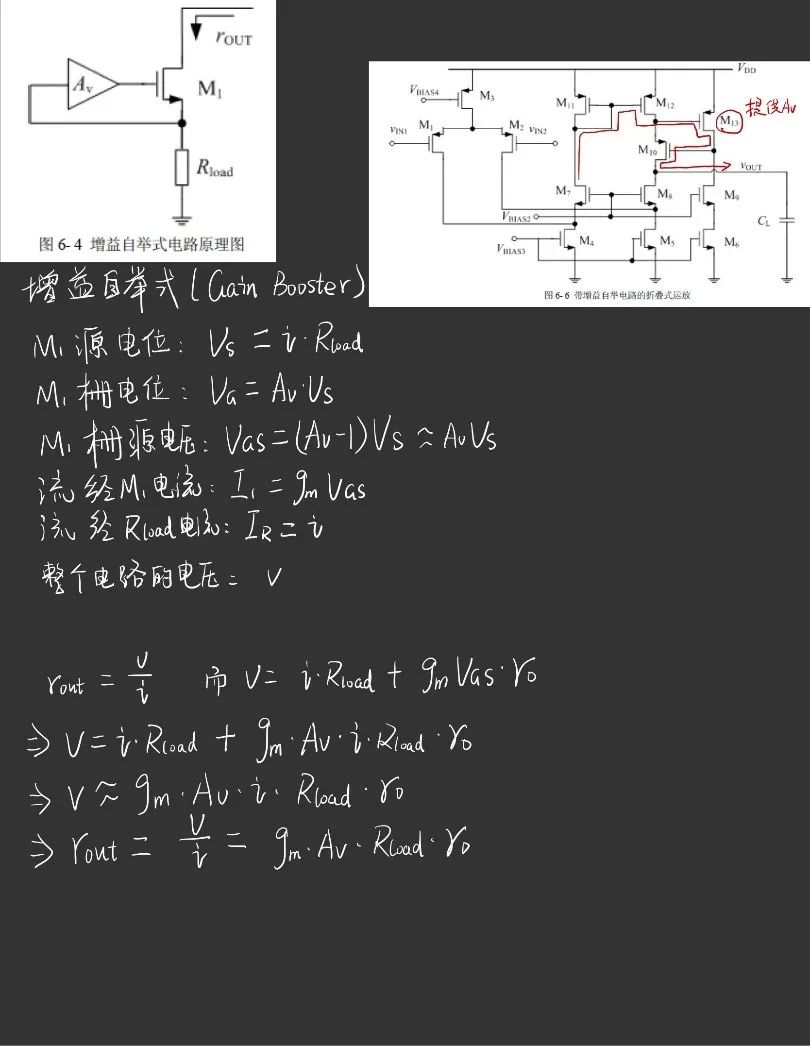

三、增益自举(Gain Booster)

增益自举原理如下图:

将折叠共源共栅运放改进成下面的电路,并给出仿真直流参数:

上面的电路的M5宽长比调节至关重要,要使其Vds恰好给M6提供偏置电压,而M6所需偏压和前述折叠共源共栅的M5和M6一模一样。在TSMC180nm工艺下,该电路参数如下表:

| Vcc | 3V | (W/L)9 | 12u/1u |

|---|---|---|---|

| Vcm | 1.5V | (W/L)7,8 | 60u/1u |

| Vb1 | 1.3V | (W/L)5 | 72u/1u |

| (W/L)6 | 29u/1u | ||

| Vb2 | 1.1V | (W/L)3,4,12 | 14u/1u |

| Vb3 | 775mV | (W/L)1,2=2(W/L)13 | 12u/1u |

| Vb4 | 2.2V | (W/L)9,10 | 70u/1u |

| CL | 1pF | (W/L)11 | 54u/1u |

ac仿真结果如下图,低频增益69dB(不知为何增益没有提高,但是GBW增大了一倍,猜测是引入了零点):

四、总结

不管是折叠共源共栅还是套筒式,电流源负载管M5和M6的偏置电压和宽长比总是最敏感的,需要多次仿真调整。

对于增益自举电路的加入,没能提升共源共栅运放的增益这点有待深入学习。

给过驱动电压Von一般:NMOS小些,PMOS大些,二极管连接的PMOS小些。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

求大神看个简单的运放电路,关于运放闭环增益的问题2013-06-10 0

-

运放的闭环增益问题2018-05-24 0

-

请问使用普通运放时如何获取运放的增益误差和增益非线性这些指标呢?2018-07-27 0

-

高增益与高带宽怎么兼得2018-09-20 0

-

高增益与高带宽怎么兼得?2018-09-21 0

-

高增益低噪声的探测器读出电路设计2018-11-12 0

-

关于运放在工作频点的开环增益如何计算的问题。2019-05-22 0

-

三运放放大器怎么提高增益和CMRR?2020-03-11 0

-

运放里常说的“单位增益稳定”是什么意思?2021-05-31 0

-

运放的开环增益和比较器的增益大小是否是一致的?2021-06-24 0

-

使用普通运放时如何获取运放的增益误差和增益非线性这样的指标呢?2023-11-17 0

-

单位增益稳定的运放是什么类型的运放?2023-11-23 0

-

高增益对讲电话电路2009-01-18 956

-

高增益、宽脉冲单稳态电路图2009-06-26 407

全部0条评论

快来发表一下你的评论吧 !