关于2nm先进制程芯片的白热化竞争

制造/封装

描述

虽然2nm先进制程芯片尚未量产,但是晶圆代工厂商之间的设备争夺战已经进入白热化阶段。各大厂商纷纷加大投资力度,竞相升级和引进最先进的设备技术,以争夺2nm制程芯片的高地。这场激烈的竞争不仅体现了对市场份额的争夺,更是对技术实力和制程能力的一次全面较量。各家厂商都希望能够在这个领域占据先机,因为2nm制程芯片被认为是未来高性能、低功耗、高集成度的关键技术。半导体fab巨头台积电、三星、英特尔、Rapidus各有动作。

最早的2nm芯片,可能来自Intel?

台积电和三星的一致口径是2nm工艺预计于2025年开始量产——但起码也是2025年下半年或者更晚的时间。

这里需要注意的问题是,“开始量产”“准备好量产”并非芯片问世时间。比如如果台积电N2工艺将在2025年下半年开始量产,则N2工艺的芯片真正上市至少需要等到2026年;且从营收的角度来看,N2工艺产生的营收也要到2026年才会反映到财报中。

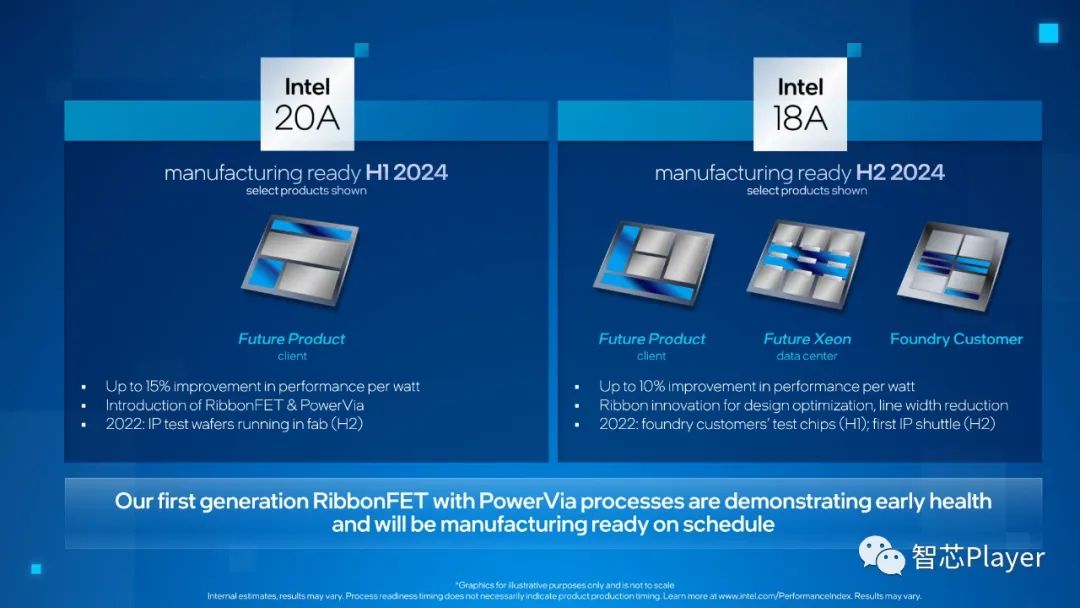

Intel这边:自从7nm/5nm时代,在半导体制造工艺技术上被台积电和三星赶超,Intel就改变了技术迭代策略。从2022年Intel投资者会议更新过的计划表来看,Intel 20A工艺——通常可看作是Intel版本的2nm工艺,即便Intel现在在市场宣传上很忌讳去谈x nm——“准备好量产”的时间是2024年上半年。

今年2月Intel在国内举办的战略媒体沟通会上再度确认了Intel 20A“测试芯片已流片”。不过需要注意的是,因为现在foundry厂的工艺名称(比如Intel 20A, TSMC N2, Samsung 2GAP)越来越放飞自我,而工艺名称并不代表晶体管或器件的实际物理尺寸,加上现在我们并不十分清楚这三家的“2nm”工艺的器件尺寸,所以仍然很难在同一平台上去说这三者是同代工艺。

Intel 20A工艺的后续工艺是18A——也是Intel此前宣称要重返半导体制造工艺王座的一代节点,预期“准备好量产”的时间已经被提前到了2024年下半年。如果各家foundry厂的未来工艺能如期交付,则显然Intel会是最快的。

但如前文所述,尖端制造工艺foundry厂有放卫星的传统——当然这也不是他们想看到的。毕竟尖端制造工艺的技术难度和成本攀升速度,造就了大量的不确定性。

三星密谋已久

这不是三星首次披露其2nm的计划,其实针对这个被广泛看好的“大节点”,这家韩国巨头密谋已久,他们在这次代工论坛上也带来了更多的消息。

据semiwiki报道,与英特尔一样,三星自己的芯片也是自己的代工客户,因此他们在2nm上首先生产的是内部产品,而不是外部代工客户。这当然是 IDM 代工厂的优势,可以结合工艺技术开发自己的芯片。三星拥有开发领先内存的额外优势。

报道指出,三星将于 2025 年开始量产用于移动应用的 2nm 工艺,然后于 2026 年扩展到具有背面供电的 HPC,并于 2027 年扩展到汽车领域。与 3nm 工艺 (SF3) 相比,三星的 2nm (SF2) 工艺已显示出性能提升 12%,功率效率提高提升 25%,面积减少 5%。

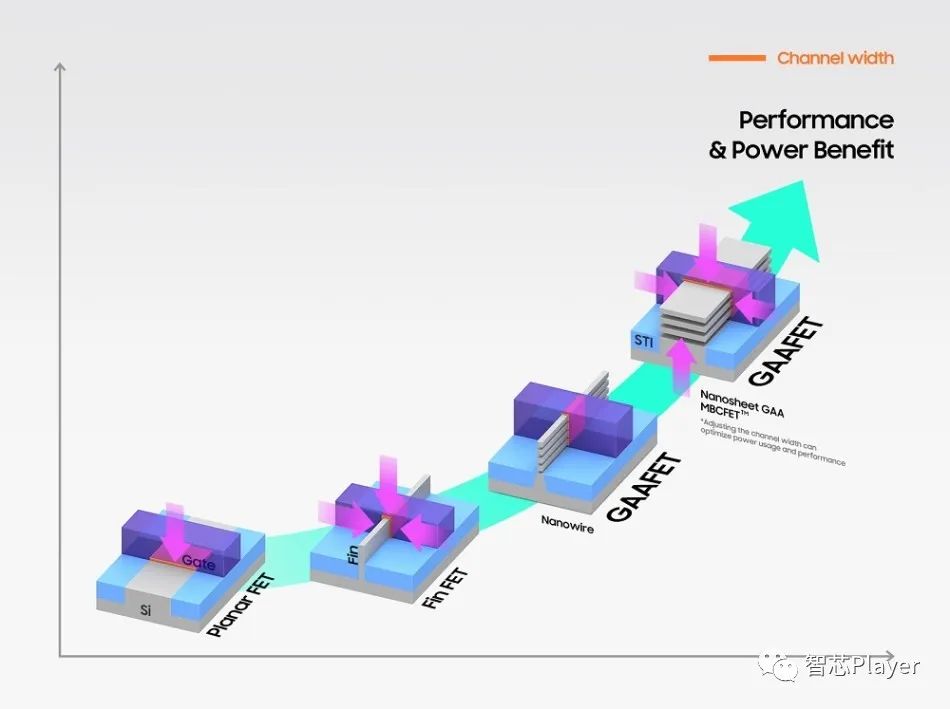

按照三星的规划,其GAA MBCFET无疑是2nm工艺的最大竞争优势所在,在上个月的时候,他们就公布了公司在3nm GAA MBCFET技术的最新进展,这将给他们的2nm提供参考。

三星表示,与 FinFET 相比,MBCFET 提供了卓越的设计灵活性。晶体管被设计成有不同量的电流流过它们。在使用许多晶体管的半导体中,必须调节电流量,以便在所需的时序和控制逻辑下打开和关闭晶体管,这需要增加或减少沟道的宽度。

而在传统的FinFET结构中,栅极所包裹的鳍片(Fin)的高度是不可调节的,因此为了增加整体沟道宽度,需要水平地增加鳍片的数量。但这种方法只能调节不连续的沟道宽度,因为当栅包围文件的沟道宽度为α时,也只能减小或增大α的倍数。这是一个严重的限制。

另一方面,MBCFET 彼此堆叠在一起,鳍片侧向放置,纳米片的宽度可以调整,以提供比 FinFET 更多的沟道宽度选项,这是一个对整个设计有用的功能,这在模拟 SRAM 中具有显著的优势设计。

”MBCFET 具有这些优势,因为它们的设计允许独立微调晶体管的沟道宽度,以便在 P 型金属氧化物半导体晶体管 (PMOS) 和 N 型金属氧化物半导体晶体管(NMOS)之间找到最佳平衡”,三星强调。

台积2nm2025如期上线

2022 年技术研讨会上,台积电正式公布了其 N2(2 纳米级)制造技术,当时台积电表示该技术计划于 2025 年某个时间投入生产,并将成为台积电第一个使用其基于纳米片的栅极全方位场效应的节点晶体管(GAAFET)。新节点将使芯片设计人员能够显著降低其产品的功耗,根据台积电公布的 N2 技术指标,可以看到,相较于其 N3E(3 纳米的低成本版)工艺,在相同功耗下,台积电 2 纳米工艺的性能将提升 10%~15%;而在相同性能下,台积电 2 纳米工艺的功耗将降低 23%~30%;晶体管密度提升 10%。

在近日召开的 Q1 季度财报会上,台积电表示客户对 2 纳米工艺热情高涨,并且重申 2 纳米将按计划在 2025 年量产,同时台积电也表示原本计划建立成熟制程的高雄厂未来将改成先进制程。从目前台积电透露的信息来看,台积电对于 2 纳米能按时交付颇有自信。

2nm搅局者Rapidus

除了代工的三大巨头,一家日本公司也声势浩大地加入了 2 纳米的竞争。

2022 年 8 月,8 家日本顶级企业:索尼、丰田汽车、日本电信电话、日本电气、日本电装、软银、铠侠和三菱日联银行分别出资 3 亿-10 亿日元不等,合资打造了这家定位高端芯片公司。同年 12 月,IBM 宣布将与 Rapidus 合作计划于 2025 年在日本启动 2 纳米制程制造基地。

IBM 的加入让 Rapidus 的计划看起来更加有希望,IBM 虽然已经不再是 IDM 公司,但仍保留了一家芯片制造研发中心。而在 2021 年,IBM 推出全球首款 2 纳米制程的芯片。同样 IBM 的 2 纳米也使用了 GAA 结构。所以,可以说 Rapidus 虽然起步晚了一些,但在 2 纳米制程方面也有了底气。

此外,该公司正在获得ASML的大力支持,主要是因为EUV技术是批量生产5-7nm以下芯片的重要制造技术。在这个领域里,Rapidus的光刻设备有望在未来两年内扮演重要的角色。据悉,ASML将于2024年在日本北海道建立技术支持基地,并派遣约50名工程师协助在Rapidus的2nm芯片工厂中试生产线上搭建EUV光刻设备,提供调试、维护和检查方面的协助。

审核编辑:黄飞

-

台积电、三星、英特尔先进制程竞争白热化2023-11-19 846

-

2nm芯片工艺有望破冰吗?亿佰特物联网应用专家 2023-10-11

-

照明市场该如何应对竞争“白热化”时期?2018-09-21 0

-

先进制程布局各有打算,GF/联电争抢晶圆榜眼2013-06-11 1074

-

新融资高达6.6亿欧元 Parrot与大疆竞争陷入白热化2016-11-10 474

-

7nm制程竞争白热化:台积电抢夺苹果A12代工 三星计划5年内占晶圆代工市场25%份额2018-01-05 783

-

中国封装市场竞争日趋白热化2019-11-18 3387

-

从代工厂看先进制程2022-01-27 808

-

2nm芯片问世了吗 2nm芯片优势是什么2022-06-23 1447

-

2nm芯片是极限吗2022-06-23 4310

-

台积电2nm芯片什么时候量产2022-06-27 1192

-

2nm芯片有望破冰吗 台积电2nm芯片什么时候量产2022-06-30 992

-

台积电2nm芯片最新信息 台积电计划2025年投产2nm芯片2022-07-01 1705

-

欧洲冲刺2nm芯片研发,建设2nm工厂2022-07-06 1155

-

台积电冲刺2nm量产,2nm先进制程决战20252023-08-20 2170

全部0条评论

快来发表一下你的评论吧 !