为什么要有TLB

描述

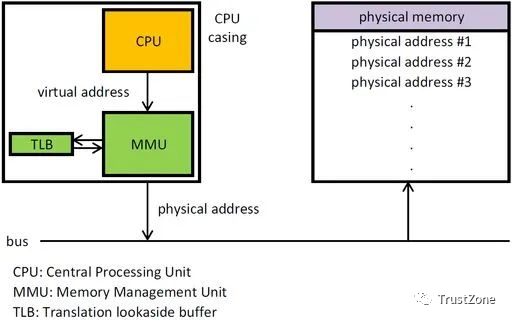

TLB 是 translation lookaside buffer 的简称。首先,我们知道 MMU 的作用是把虚拟地址转换成物理地址。

虚拟地址和物理地址的映射关系存储在页表中,而现在页表又是分级的。

64 位系统一般都是 3~5 级。

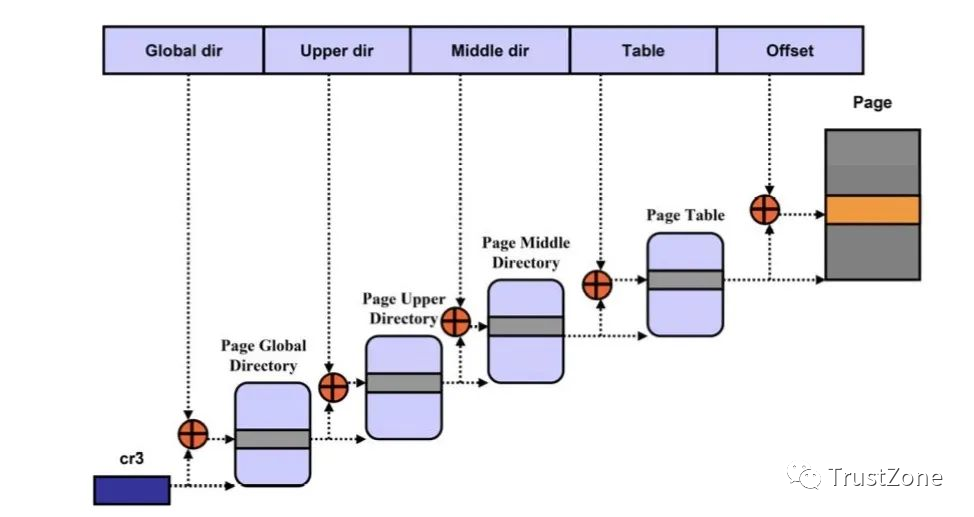

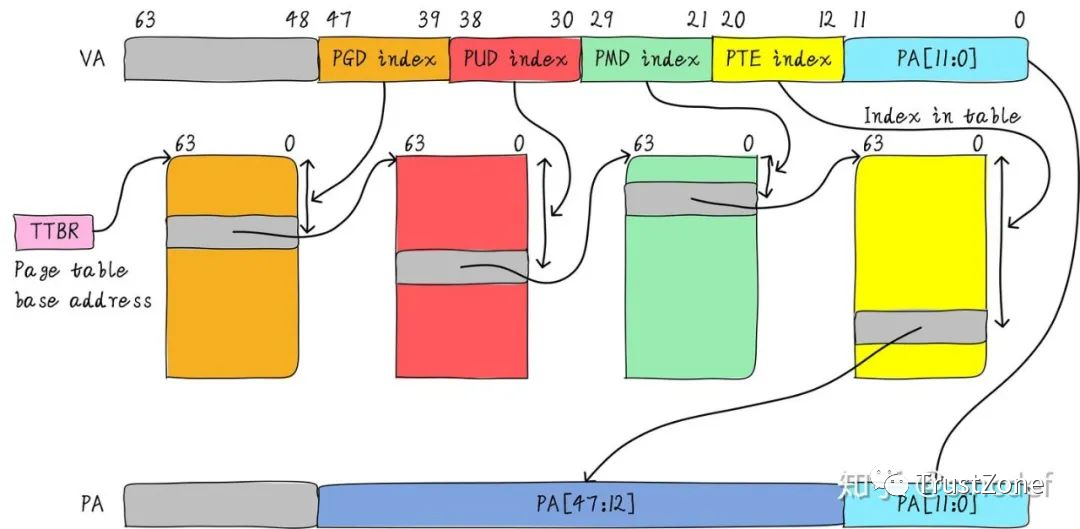

常见的配置是 4 级页表,就以 4 级页表为例说明。

分别是 PGD、PUD、PMD、PTE 四级页表。

在硬件上会有一个叫做页表基地址寄存器,它存储 PGD 页表的首地址。

MMU 就是根据页表基地址寄存器从 PGD 页表一路查到 PTE,最终找到物理地址(PTE页表中存储物理地址)。

这就像在地图上显示你的家在哪一样,我为了找到你家的地址,先确定你是中国,再确定你是某个省,继续往下某个市,最后找到你家是一样的原理。一级一级找下去。(这个比喻真的不错)

这个过程你也看到了,非常繁琐。如果第一次查到你家的具体位置,我如果记下来你的姓名和你家的地址。下次查找时,是不是只需要跟我说你的姓名是什么,我就直接能够告诉你地址,而不需要一级一级查找。

四级页表查找过程需要四次内存访问。延时可想而知,非常影响性能。页表查找过程的示例如下图所示。以后有机会详细展开,这里了解下即可。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

嵌入式处理器的TLB电路设计2010-05-12 422

-

请问TLB框架程序谁有?求坛友共享一个2018-04-03 0

-

请问AM335 u-boot 中的MMU,gd->arch.tlb_addr是在哪里初始化的?2018-06-20 0

-

labview2015调用tlb库错误信息:LabVIEW: 输入为空引用句柄或之前已删除的引用句柄。2018-07-12 0

-

FIDEMAILATION中的TLB异常2019-09-18 0

-

以Freescale的E500内核为例简单介绍TLB Entry基本组成结构2022-09-07 0

-

看一条关于TLB维护的指令2023-02-16 0

-

P2020 TLB0/TLB1失效的原因?怎么解决?2023-03-21 0

-

搞嵌入式,为啥要有uboot?2020-02-05 2664

-

CPU场景下的TLB相关细节2020-12-26 3620

-

详解TLB的作用及工作原理2022-05-12 3768

-

TLB是什么?有何作用2022-07-28 12746

-

Versal ACAP、APU - DSB 指令后可能会发生推测性 TLB 填充2022-08-05 273

-

小体积、广应用的B型剩余电流检测模组——TLB1506-P2022-09-01 1315

-

要有光2022-11-07 75

全部0条评论

快来发表一下你的评论吧 !