I2C通信序列的典型特征

接口/总线/驱动

描述

I2C(或IIC)代表IC间通信,是流行的微控制器通信协议之一。I2C通常用于与传感器通信,但也用于许多其他应用。

I2C是一种同步协议,这意味着它有一条时钟线(有关同步和异步通信的更多信息,请参阅我们的关于该主题的文章)。

I2C通信

虽然I2C只使用两条通信线路(时钟和数据),但它可以在同一条I2C总线上容纳多个设备;这是通过利用一种寻址方案来实现的,其中总线上的每个设备都有一个唯一的地址。通信始于发送通信所针对的设备地址,然后被寻址的设备必须确认其存在并准备好进行通信。

由于只有一条数据线(SDA串行数据)用于发送和接收数据(半双工),因此需要一种方案,使通信中的主机和从机都能无冲突地控制数据线。必须避免总线争用,即一个器件试图向总线写入高电平,而另一个器件试图向总线写入低电平,这会造成短路。

为了实现这一点,使用开漏方案;其中任一器件只能驱动总线“低电平”或“释放”总线,上拉电阻用于在总线被释放时将线路拉高(如果您不熟悉开漏或上拉电阻这两个术语,请参考我们的关于该主题的文章)。时钟线(SCL串行时钟)也利用了这一方案,一些创新的技术被用来为I2C协议增加一些有用的功能——稍后会详细介绍。

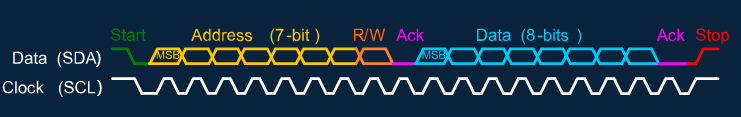

下图说明了I2C通信序列的典型特征:

通信从I2C总线空闲开始,时钟和数据线都不被驱动,因此被上拉电阻拉高。然后,主机(启动通信的器件)启动通信,首先拉低SDA线,然后拉低SCL线,这被定义为起始条件。

接下来,主机发送它希望与之通信的设备的7位地址,随后是一个“读或写”位,表示主机希望写入(0)还是读取(1)该设备。数据线在时钟线的上升沿被视为有效(从机读取),数据首先以最高有效位(MSB)传输(如果您不熟悉术语最低有效位和最高有效位,那么您可以阅读本文了解更多信息)。

地址发送后,假设被寻址的从机出现在I2C总线上,主机将释放数据线(开漏),从机将在一个时钟周期内保持数据线为低电平,以确认(ack)其存在并准备好通信。如果从机不在总线上,则上拉电阻会将数据线拉高,主机将知道从机不可用。

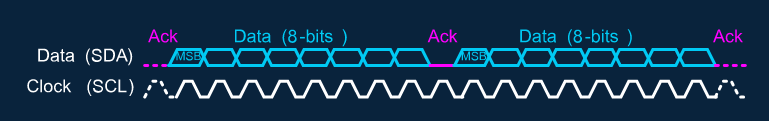

在这个阶段,主机和从机之间可以传输数据。如果正在读取数据,则从机将发送数据(同时主机继续驱动时钟线),或者如果正在写入数据,则主机将发送数据。每个数据字节后都有一个Ack位,在此期间,接收器(可以是主机,也可以是从机,取决于哪一方发送数据)应使数据线保持低电平,以指示其已接收到通信(并准备好进行下一次通信,如果适用)。

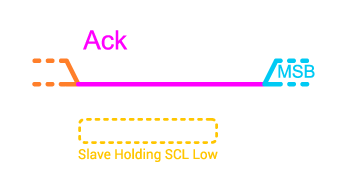

时钟拉伸

I2C总线上的从设备能够通过将时钟(SCL)线保持在低电平来延迟它们的响应(如果它们仍然忙碌并且还没有准备好响应),这种特性被称为“时钟拉伸”;一旦准备好响应,从机就释放时钟线,数据传输继续进行。这类似于UART (CTS/RTS)中的流控制线路,但不需要额外的通信线路(注意SPI协议没有流控制功能)。

一个或多个数据字节可以按顺序传送,在每个字节之后出现一个ack。

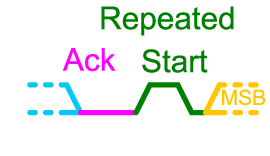

重复开始

因为从设备可能具有大量可读取的值(例如多个传感器读取值以及设置值),所以从设备可能要求主设备在进行实际读取之前首先写入指示其想要读取什么的指令。在这种情况下,主机将首先发出一个写操作,数据是指示应该读取什么的指令,然后主机将立即发出读操作。然而,在两者之间没有发出stop,而是主机使用重复起始条件(后跟7位地址和1位读/写位,显然现在设置为read)从写切换到读。要发出重复启动信号,主机首先将数据线拉高,然后是时钟线,然后主机将数据线拉低,接着是时钟线。

数据速率和距离

I2C总线上的通信通常以100kHz或400kHz的频率进行。这些相对较低的速度适合少量数据传输,但SPI(使用MHz范围内的时钟,可能采用双通道或四通道模式)通常更适合需要传输大量数据的高吞吐量应用。I2C通常仅用于相对较短距离的通信,但也有一些方案可以通过差分对传输I2C,以实现更长距离的通信。

审核编辑:黄飞

-

3分钟理解通信协议之I2C总线 #通信协议硬声课堂 2021-10-18

-

I2C规范,I2C总线原理2009-04-09 0

-

I2C通信设计深度解析2012-08-12 0

-

I2C通信2016-04-22 0

-

I2C的通信问题2016-10-05 0

-

如何用MSP微控制器开始一个与I2C通信有关项目2018-06-04 0

-

i2c通信协议2020-03-06 0

-

请问STM8芯片I2C总线的通信过程及主模式是怎样的?2020-11-09 0

-

理解I2C协议所需的工具与资源2020-12-14 0

-

i2c不通的原因是什么2021-03-02 0

-

I2C简介2021-08-10 0

-

什么是软件I2C和硬件I2C2021-08-23 0

-

STM32硬件I2C重新编制I2C的通信流程2021-12-14 0

-

I2C通信协议的原理是什么2022-02-17 0

-

I2C通信详解2022-02-28 0

全部0条评论

快来发表一下你的评论吧 !