关于AMBA APB总线的知识点介绍

接口/总线/驱动

描述

本篇先总结一些APB总线的知识点。

1 学习资料

·由于师兄给的设计要求是AMBA2.0,所以参考了ARM官网关于AMBA2.0的技术手册《AMBA™ Specification (Res2.0)》,这本技术手册英文比较好理解,篇幅也很短,可以直接看英文版,问题不大。

·在这本书中,介绍了AMBA基本信号、AHB总线、ASB总线、APB总线,由于写的项目主要设计APB接口,所以在本文中主要介绍APB的部分。

AMBA(Advanced Microcontroller Bus Architecture)高级处理器总线架构;

APB(Advanced Peripheral Bus)高级外围总线;

2 AMBA APB的优点

先说用途和目的:APB可以实现与低功耗、低速设备进行数据传输。

接下来介绍其特点:AMBA APB总线可以用在低带宽和不需要高性能的外设上(即低速且低频率的外设);可以将APB视作AHB的二级总线;

·低功耗(APB总线信号端口比较简单,复杂度低,低频工作环境等因素都可以降低功耗)

·低成本(用的广泛,可以兼容很多IP,降低开发成本)

·低带宽(信号的位宽有限,而且简单的外设也不需要多位宽)

·无流水线结构(区别于AHB,但效率没有AHB高)

·APB总线中,唯一的master就是APB Bridge,其他设备都是slave。

3 典型的AMBA APB端口信号(APB Bridge、slave为例)

3.1 模块端口示例(所有的AMBA APB信号使用P字母开始)

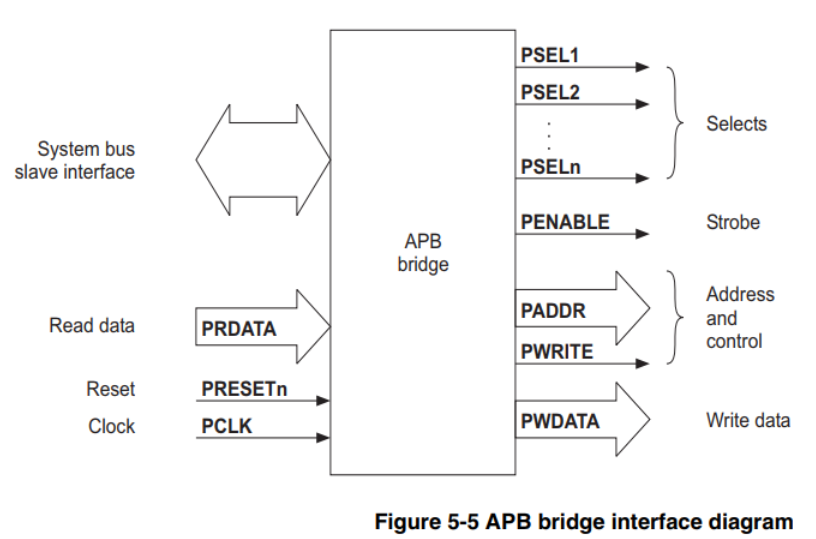

APB总线协议中唯一的master—APB Bridge模块结构:

关于system bus slave interface信号的来源,其实是有一个AHB-APB模块和APB进行连接通信;

实际的信号流:cortex M3核-》bus matrix -》 AHB-APB -》 APB bridge -》 APB slave(后续可能会提到,要看我能不能实现软硬结合了~)

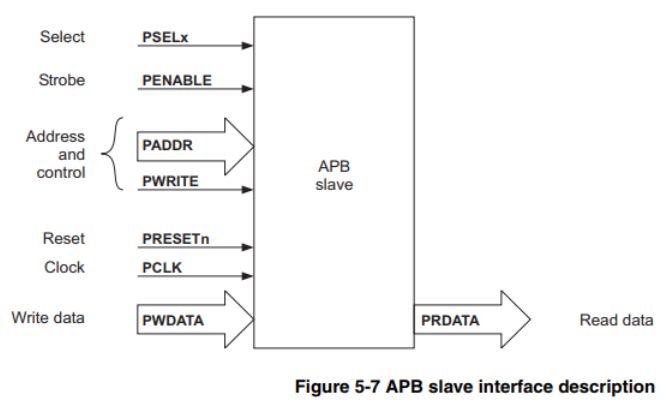

APB中slave模块结构:

APB Bridge和slave的信号其实是可以进行互联的,APB Bridge(master)将控制信号和数据传输给slave,slave将部分信号传输给APB Bridge(master),从而完成通信;

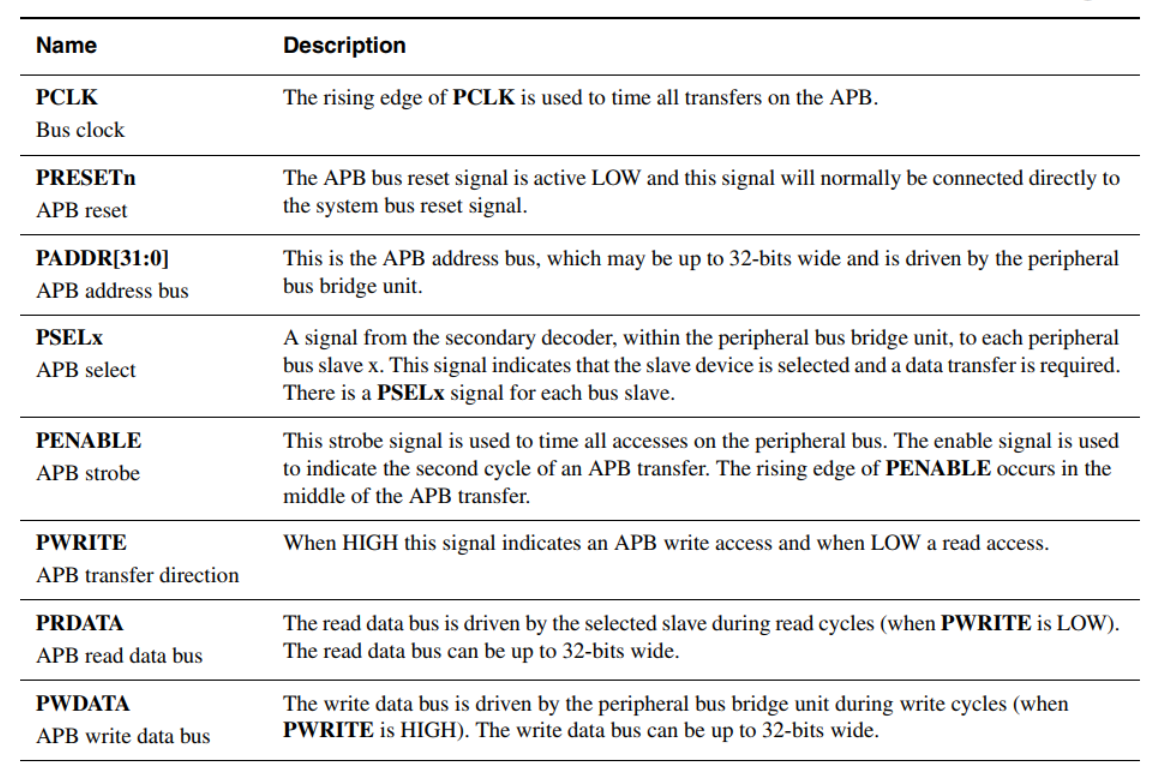

信号及其来源:

SignalSourceDescription

PCLK时钟源系统时钟,传输发生在上升沿

PRESETn复位源复位信号,低使能

PADDR[31:0]APB桥地址信号,最高可达32位

PSELxAPB桥由APB bridge产生的信号,针对每一个Peripheral Bus Slave片选信号,表示x从机是否被选中

PENABLEAPB桥使能信号,标记传输使能

PWRITEAPB桥读/写控制信号,高位写,低为读

PWDATAAPB桥写数据

PREADY从机标记从机是否已将数据发送到总线,高为ready(给出的slave没有,但是官方slave代码会有的,常设定为assign PREADY = 1)

PRDATA从机读数据

PSLVERR从机故障信号,为高时发生故障(给出的slave没有,但是官方slave代码会有的,常设定为assign PSLVERR = 0)

3.2 PCLK、PRESETn:首先来进行分析,一个APB总线信号肯定要有时钟信号PCLK来管理数据传输,其次是异步复位信号PRESETn 信号,这两个信号是基本所有模块的基础。

3.3 PADDR[31:0]:这里表示地址信号(地址与存储的数据是一一对应的关系,要求是对齐的关系,这里没有涉及),一般以16进制表示形式,也就是0xXXXX XXXX;

3.4 PSELx:在一个APB总线中,只有一个master(也就是APB桥),但是可以接很多slave。至于选择哪个slave就需要PSELx信号进行选择;

3.5 PENABLE:传输使能信号,表示当前传输是否有效;

3.6 PWRITE:读写信号,APB Bridge需要进行写传输时,该信号拉高;APB Bridge需要进行读传输时,该信号拉低。(这个信号是告诉slave的,表示master正在想干什么事情)

3.7 PRDATA:读数据(slave传输给master)

3.8 PWDATA:写数据(master传输给slave)

附上ARM官方文档的APB信号端口,供大家欣赏:

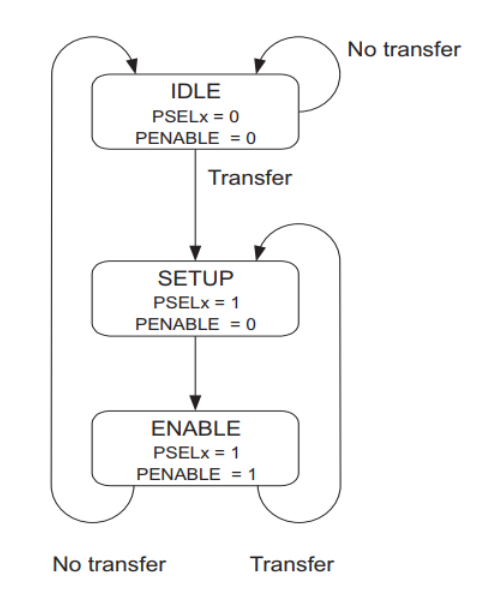

4 APB状态机

官方文档的状态机:

状态功能

IDLE默认状态(我的理解是一种待机状态)

SETUP总线的传输状态来到SETUP状态,slave的PSELx被选中(拉为1),但只保持一个时钟周期。之后就要在下一个时钟上升沿时候,来到ENABLE状态

ENABLE在ENABLE状态,PENABLE被拉高。在SETUP和ENABLE状态,地址、写信号、选择信号都要保持稳定。在ENABLE状态也只持续一个时钟周期,如果没有后续传输,总线又将回到IDLE状态。如果有后续传输,总线将回到SETUP状态。

从状态机来看,APB对每一笔数据的传输,都需要两个周期(省略掉IDLE),因此APB数据不适合流水线架构的模块设计中。

(注意:在ENABLE回到SETUP状态时,对于地址信号、写信号、选择信号的要求并不高,可以出一点小错误,因为简单外设接受数据的速度还可以,后期出一些小问题影响不大)

5 写传输和读传输时序逻辑

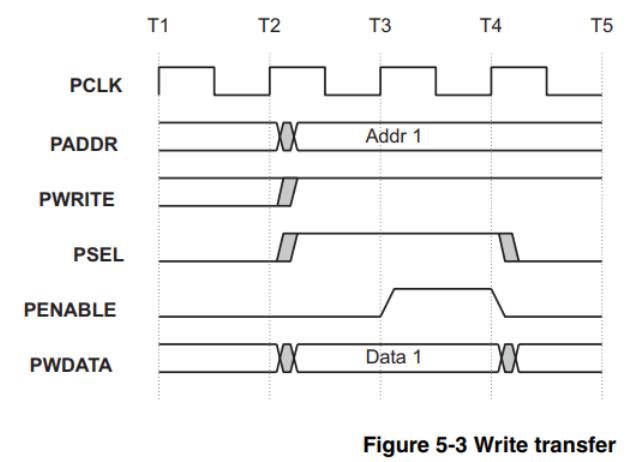

5.1 写传输:

先放出写传输时序图:

分析(注意,我理解的这个时序图是从master的角度进行分析的,要结合master和slave的共有信号去理解时序图):

[T1,T2)对应IDLE状态 (这里采用闭区间、开区间的表达方式,用作表示T1上升沿起作用,但T2上升沿还未起作用,下同);

[T2,T3) 对应SETUP状态。此时,由于T2上升沿的有效,电路状态开始发生改变,在这个时钟周期内,PADDR、PWRITE(拉为1)、PSEL(选中哪个slave)、PWDATA等信息开始加载到数据线上,注意此时PENABLE还没有起效果,只起到一种预加载的效果。

[T3,T4)对应ENABLE状态。此时,由于T3上升沿有效,PENABLE开始有效,在这个时钟周期内,上个状态选中的slave开始接受PADDR、PWRITE、PSEL、PWDATA等信息。

[T4,T5)阶段,由于T4时刻上升沿开始触发,导致PENABLE和PSEL信号恢复默认值,等待下一次指令进行5.2 读传输:

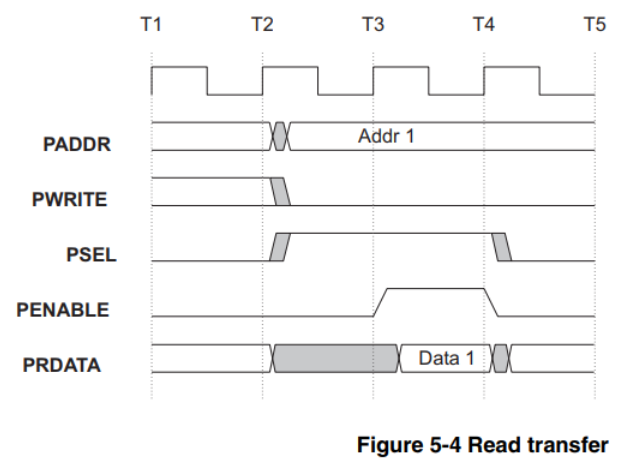

放出写传输时序图:

分析(注意,我理解的这个时序图是也从master的角度进行分析的,要结合master和slave的共有信号去理解时序图):

[T1,T2)对应IDLE状态;[T2,T3) 对应SETUP状态。此时,由于T2上升沿的有效,电路状态开始发生改变,在这个时钟周期内,PADDR、PWRITE(拉为0)、PSEL(选中哪个slave)等信息开始加载到数据线上,注意此时PENABLE还没有起效果,只起到一种预加载的效果。(注意此时没有PRDATA数据线上没有有效信息)

[T3,T4)对应ENABLE状态。此时,由于T3上升沿有效,PENABLE开始有效,在这个时钟周期内,上个状态选中的slave开始接受PADDR、PWRITE、PSEL等信息,并传输PRDATA信号给master。 4. [T4,T5)阶段,由于T4时刻上升沿开始触发,导致PENABLE和PSEL信号恢复默认值,等待下一次指令进行何种操作。

一些疑惑

·为什么读操作在第一个时钟周期里的PRDATA没有有效数据?

在对比写操作和读操作的过程中,发现读操作在SETUP时钟周期里没有有效数据,个人理解是因为低速外设准备数据的速度太慢了,如果在SETUP时钟周期就要求有效数据,很有可能传输不了正确的数据,索性降低要求,让其在ENABLE时钟周期才有效。

而APB Bridge准备数据的速度很快,因此可以在SETUP状态就可以准备好数据,方便在ENABLE状态给外设数据。

(待续)

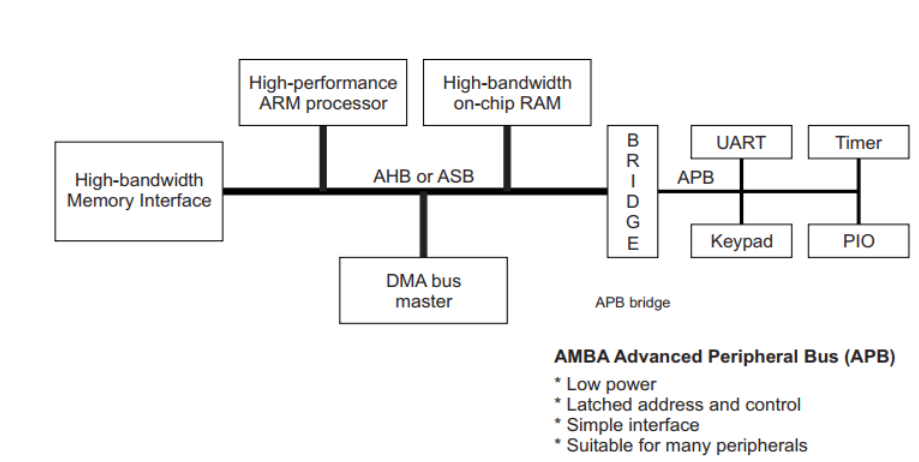

6 APB总线连接外设应用

官方文档给出的一些应用:

从这里可以看出对于AMBA APB总线来说,只有一个master(APB Bridge),同时可以挂载多个slave(比如uart,keypad,timer,PIO)。

审核编辑:黄飞

-

AMBA AHB总线与APB总线资料合集2022-04-07 0

-

ARM总线协议AMBA中AHB、APB的区别与联系2022-02-09 0

-

AMBA、APB、AHB简介2022-02-17 0

-

AMBA中的APB总线协议详解2022-06-07 0

-

基于AMBA APB总线NandFlash控制器的设计2011-11-03 773

-

APB总线的应用框图及接口信号2020-11-17 12341

-

基于AMBA总线介绍2021-05-19 1903

-

浅述AMBA-APB总线2021-07-23 1984

-

介绍AMBA2.0总线2021-09-06 2824

-

AMBA总线那些事之APB2023-05-04 1968

-

AMBA总线—apb简介2023-06-05 1235

-

AMBA总线那些事之APB协议入门2023-06-05 1465

-

什么是APB协议/总线?APB总线入门2024-01-02 1325

-

AMBA总线中APB interconnect的介绍2024-01-13 331

-

AMBA总线中APB slave设计介绍2024-01-13 377

全部0条评论

快来发表一下你的评论吧 !