开关电源BUCK 拓扑的EMI对策

EMC/EMI设计

描述

电磁干扰的来源

开关电源与 LDO 相比,具有效率高、体积小、可升压等显著优点,但是开关电源在工作时,会对外产生电磁辐射,若辐射过大,则会对周围器件造成严重影响,导致系统不能稳定工作。要实现抑制电源对外的电磁辐射,首先应明确电磁辐射产生的机理与源头。开关电源是通过功率管打开时给电感充电,电感储能;功率管断开时,电感释放能量,实现电压变换。

由于功率管、续流二极管不断的打开与关断,造成电流不连续,此变化电流会产生尖峰电压(由 V=L*di/dt 可以推导出,尖峰电压等于电流回路中的寄生电感乘以电流变化率,L 是开关电流回路的寄生电感),此尖峰电压会产生较大的电磁干扰,可以通过抑制此尖峰电压来降低电磁干扰。通常可以通过以下几种方法来降低开关电源对外产生的电磁干扰。

改善方法一:缩短开关电流回路

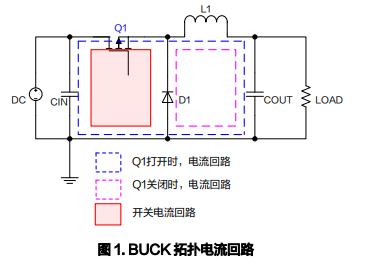

BUCK 拓扑电流回路图,以系统工作在连续状态下为例。

由“图 1”可知,当功率管 Q1 打开时,电流回路是 CIN-》Q1-》L1-》COUT;当 Q1 闭合时,电流回路是 L1-》COUT-》D1;不论功率管 Q1 打开还是关断,电流均流过 L1 和 COUT,表明流过 L1 和 COUT 处电流是连续电流,流过 CIN、Q1、D1 的电流是开关电流,开关电流会在寄生电感上产生毛刺电压,对外辐射电磁波。由 V=L*di/dt 可知,在 di/dt 不变的条件下,可以通过缩短 CIN、Q1、D1 的电流回路,来减少开关电流回路的寄生参数,从而实现降低系统产生的电磁辐射。

改善方法二:降低电流变化率

降低开关电流变化率(即降低 di/dt 的值),首先在使用条件不变的情况下,电流的变化量基本不会变化,只好通过延长电流的变化时间来降低 di/dt 的值。可以通过使用开关速度稍慢的二极管来降低 D1 回路电流变化率,但是使用开关速度稍慢的超快恢复二极管,会导致二极管的损耗增大,不仅会影响效率,还会导致二极管温度过高,反向漏电流增大,影响系统稳定性。

改善方法三:抑制高频噪声

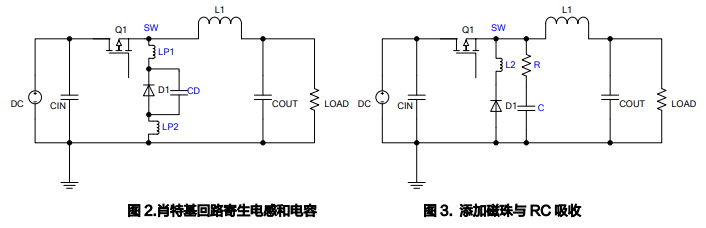

参考“图 2”,肖特基本身具有寄生电容,回路上存在寄生电感;开关电流会流过肖特基 D1,寄生的电感、电容会产生振铃,若振荡频率超过 30MHz,进入辐射测试频率段,则会被测试仪器捕捉到。我们可以通过在肖特基处串联磁珠来滤除高频信号,降低高频信号对外电磁辐射能量。但是肖特基上串联磁珠,会产生较大负向尖峰电压,需要控制输入电压与尖峰电压绝对值之和小于芯片的耐压,确保系统稳定性。

备注:我们常用的贴片式磁珠材料主要是有磁粉、镍、银浆三大部分组成,其在高频条件下具有相当大的阻抗,可以吸收高频信号(通常 30MHz 以上为高频)。

改善方法四:添加 RC 吸收电路

在无法进一步降低系统自生的干扰时,可以通过外加对策器件来进一步抑制;在芯片 SW 与 GND 之间并联 RC 吸收电路不仅可以吸收寄生参数产生的毛刺电压,也可以改变谐振频率,从而实现抑制电磁辐射。通常“方案三”与“方案四” 组合使用,抑制效果较佳。相应的电路图如图 3 所示:

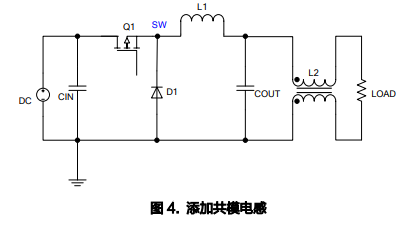

改善方法五:添加共模电感

辐射测试点频率段为30M到1000M,此频率段对应的波长是0.3米到10米,如果要发射一定波长的电磁波,需要一根发射天线,成为天线的必要条件是长度至少要大于波长的二十分之一,当天线是电磁波半波长的整数倍时,发射功率最大。通常输出端的电源线均比较长,有可能成为对外发射电磁波的天线,可以通过在系统输出端串联共模电感(参考“图4”),滤除共模信号来抑制辐射超标,但同时共模电感具有体积大、成本高、不易加工等缺点,不适合应用于小体积、低成本方案。

综上:

通过以下简单实用的步骤来帮助我们设计的开关电源快速通过相关的辐射测试

1.优化 PCB 走线,输入端电容靠近芯片 VIN 与 GND 引脚,反馈走线远离开关信号节点,使用 GND 走线包围开关信号节点,同时缩短开关电流回路路径,即将输入端电容正极靠近芯片 VIN 引脚,肖特基阴极靠近芯片 SW 引脚,肖特基阳极靠近输入电容负极;

2.在肖特基处串联磁珠和 RC 吸收电路,磁珠通常选用交流阻抗 60-80R,直流阻抗越小损耗越小;RC 吸收电路中的电阻阻值在 10R 左右,电容容量在 1nF 以内。

审核编辑:黄飞

-

开关电源拓扑结构有那几种?有什么特点?2021-03-11 0

-

基本开关电源拓扑(2)-BOOST/BUCK-BOOST拓扑2023-05-30 1659

-

介绍直流开关电源中的buck电路2023-06-09 758

-

几种构成线性电源和开关电源的基本拓扑2021-10-28 0

-

三种电源的拓扑以及Buck型开关电源芯片各引脚的作用2021-10-28 0

-

Buck开关电源的拓扑结构2021-10-28 0

-

5种经典开关电源拓扑结构2010-11-08 1476

-

开关电源中如何选择合适的拓扑2018-05-09 10519

-

开关电源的BUCK 电路拓扑过程分析2019-04-25 10384

-

开关电源的EMI2021-09-15 1026

-

BUCK开关电源的应用资料2021-09-18 1092

-

开关电源必会拓扑1-buck2021-09-18 749

-

Buck开关电源拓扑结构分析2021-10-21 825

-

开关电源拓扑结构该如何选择呢?2023-04-26 1271

-

基于PSIM软件的BUCK开关电源仿真研究2024-03-14 847

全部0条评论

快来发表一下你的评论吧 !